基于行列扫描的ILV故障测试电路及测试方法

- 国知局

- 2024-07-31 19:45:27

本发明属于集成电路测试与可测性设计领域。

背景技术:

1、随着集成电路技术的发展,晶体管特征尺寸不断缩小,已逼近其物理极限。为了延续摩尔定律,单体三维集成电路(monolithic 3-d integrated circuits,m3d ics)通过在垂直维度上制造多个互相隔离的有源层,使其电路集成度与功能多样性远超传统平面集成电路,成为未来集成电路的发展趋势。在m3d ics中,纳米级层间通孔(inter-layer vias,ilvs)作为不同有源层间垂直维度上的信号通路,保证其有效性与可靠性是保证m3d ics性能良好的关键。然而,高密度的集成设计和氧化隔离层打薄工艺使得ilvs极易产生故障,因此需要在m3d ics生产过程中即时地对新增ilvs进行故障检测与故障定位。ilvs故障检测可发现新增ilvs是否存在缺陷,从而保证m3d ics的良产率;ilvs故障定位可将缺陷ilv的位置信息反馈给制造商,用以优化设计。

2、目前,针对ilvs的故障测试方法主要有以下三种:

3、一是采用基于ieee p1838标准的边界扫描电路对ilvs进行故障测试。该方法虽然技术成熟,但由于ilvs密度高且数量大(最多可达1亿根/mm2),采用该方法进行测试将造成巨大的电路面积开销。

4、二是通过添加专用测试层对ilvs进行故障测试。该方法虽然一定程度的降低了测试成本,但专用测试层只能覆盖上下两层ilvs的故障测试,电路面积开销依然巨大且难以扩展至多层。

5、三是通过内建自测试电路对ilvs进行故障测试。该方法通过特制电路,极大的减少了测试电路的占用面积,并可有效覆盖ilvs常见故障。其主要缺点则是只能判断故障有无,却无法将其定位。

技术实现思路

1、本发明是为了解决现有针对ilvs的故障测试方法中多数方法电路占用面积大,而电路占用面积小的方法又无法对故障进行定位的问题,现提供基于行列扫描的ilv故障测试电路及测试方法。

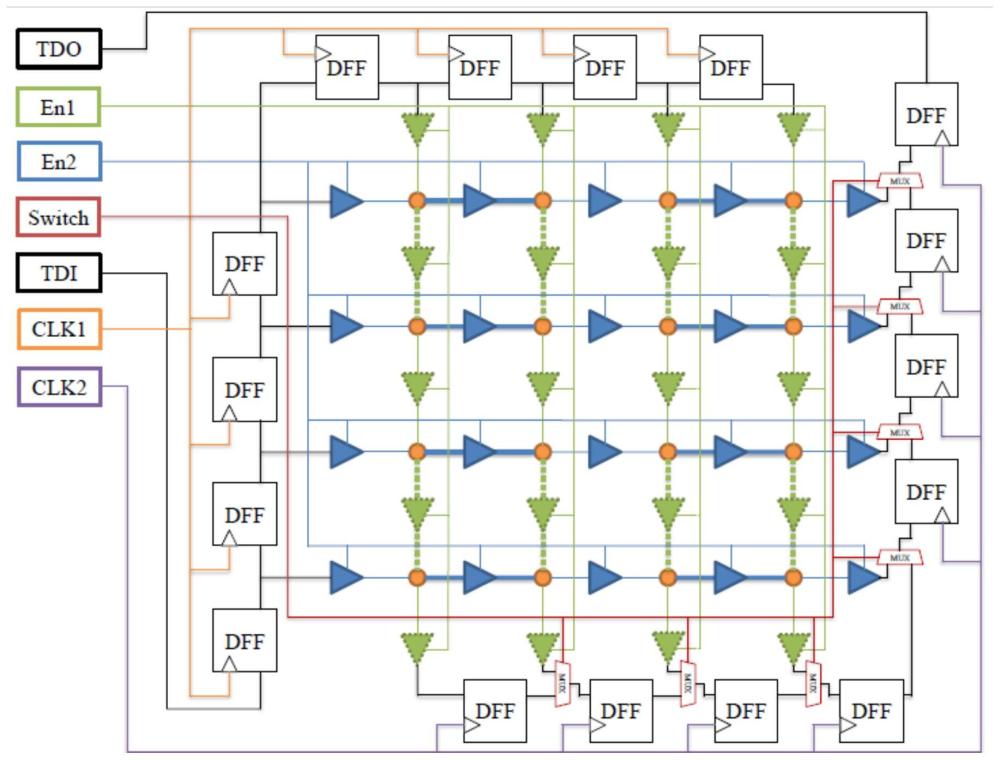

2、基于行列扫描的ilv故障测试电路,在m×n的被测ilv阵列中,每一行的ilv均通过行三态驱动器首尾顺次连接构成一条行菊花链,每一列的ilv均通过列三态驱动器首尾顺次连接构成一条列菊花链,共有m+n条菊花链;

3、所述ilv故障测试电路包括:输入移位寄存器和输出移位寄存器;

4、所述输入移位寄存器的测试信号输入端作为所述ilv故障测试电路的测试信号输入端,所述输入移位寄存器包括m+n个测试信号输出端,该m+n个测试信号输出端分别与m+n条菊花链一一对应,所述输入移位寄存器的每个测试信号输出端均与其对应菊花链的测试信号输入端相连;

5、所述输出移位寄存器的测试信号输出端作为所述ilv故障测试电路的测试信号输出端,所述输出移位寄存器包括m+n个测试信号输入端,该m+n个测试信号输入端分别与m+n条菊花链一一对应,所述输出移位寄存器的每个测试信号输入端均与其对应菊花链的测试信号输出端相连。

6、进一步的,上述输入移位寄存器包括m+n个一号d触发器;

7、所有一号d触发器顺次连接构成输入信号传输链,位于该输入信号传输链输入端的一号d触发器输入端作为所述输入移位寄存器的测试信号输入端,每个一号d触发器的输出端均作为所述输入移位寄存器的一个测试信号输出端。

8、进一步的,上述所有一号d触发器的时钟信号输入端共同连接构成输入移位寄存器的时钟信号输入端。

9、进一步的,上述输出移位寄存器包括交替排布的m+n个二号d触发器和m+n-1个双路选择器,使得相邻两个二号d触发器之间均有一个双路选择器;

10、每个双路选择器的一个信号输入端均作为所述输出移位寄存器的一个测试信号输入端,每个双路选择器的另一个信号输入端均与其相邻的二号d触发器输出端相连,每个双路选择器的信号输出端均与其相邻的二号d触发器输入端相连;

11、一个位于端部且输出端自由的二号d触发器输出端作为所述输出移位寄存器的测试信号输出端,另一个位于端部的二号d触发器输入端作为所述输出移位寄存器的一个测试信号输入端。

12、进一步的,上述所有二号d触发器的时钟信号输入端共同连接构成所述输出移位寄存器的时钟信号输入端。

13、进一步的,上述每条菊花链的测试信号输入端均通过一个测试用ilv通道与其对应的输入移位寄存器的测试信号输出端相连;

14、每条菊花链的测试信号输出端均通过一个测试用ilv通道与其对应的输出移位寄存器的测试信号输入端相连。

15、基于上述基于行列扫描的ilv故障测试电路实现的ilv故障测试方法,具体如下:

16、调整所有行三态驱动器导通且所有列三态驱动器截止时,向所有行菊花链输入测试信号,并采集各行菊花链输出的测试信号,对比同一条行菊花链输入和输出的测试信号电平差异,实现被测ilv阵列的行测试;

17、调整所有行三态驱动器截止且所有列三态驱动器导通时,向所有列菊花链输入测试信号,并采集各列菊花链输出的测试信号,对比同一条列菊花链输入和输出的测试信号电平差异,实现被测ilv阵列的列测试;

18、当被测ilv阵列中存在故障时,故障行与故障列交点处的ilv为故障ilv。

19、进一步的,上述测试信号包括两个不同的数字信号1和0,且相邻两行或两列输入的测试信号不同。

20、进一步的,上述行测试和列测试方式相同,具体如下:

21、当一条菊花链输入和输出的测试信号相同时,则该条菊花链无故障;

22、当一条菊花链输入测试信号为1且输出测试信号为0时,则该条菊花链存在开路或stack-at 0故障;

23、当一条菊花链输入测试信号为0且输出测试信号为1时,则该条菊花链存在stack-at 1故障;

24、当相邻两条菊花链输入测试信号为10或01且输出测试信号均为00时,则相邻两条菊花链之间存在短路故障。

25、进一步的,上述双路选择器包括输出捕获模式和输出移位模式;

26、调整双路选择器处于输出捕获模式,使得各菊花链将测试信号锁存在对应的二号d触发器中;

27、调整双路选择器处于输出移位模式,使得各二号d触发器锁存的测试信号从所述输出移位寄存器中输出。

28、本发明具有以下优点:

29、1.可有效检测ilv的开路、短路、stack-at 0、stack-at 1四种常见故障,并能对以上故障进行故障定位。

30、2.可适用于新增ilvs部分的测试,且可扩展至任意层的m3d ics。

31、3.具有较快的测试速度,对于具有30000个ilv的4层m3d ics而言,完成全部测试仅需3.012ms。

32、4.相较于目前已知的ilv故障测试方法,具有最小的测试面积开销,对于具有30000个ilv的4层m3d ics而言,其测试电路面积开销为4.919μm2/ilv。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183878.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。