一种模拟EEPROM的电路设计方法与流程

- 国知局

- 2024-07-31 19:46:02

本发明涉及控制器和存储器,尤其是指一种模拟eeprom的电路设计方法。

背景技术:

1、在微控制器中,eflash作为一种非易失性存储器,具有容量大,存储密度高,价格低等优势。而eeprom同样也是一种非易失性存储器,相比于eflash,其优点在于编程的方式更为灵活,支持对字节的擦除和编程并且可擦写的次数更多,使用寿命更长。

2、因此,eflash更适合存储代码和常量,即不需要频繁更新、数据量大的场景,比如说音频数据、图片数据、程序等等。而eeprom适合存储需要频繁更新数据、数据量小的场景,比如系统参数配置等等。

3、针对现有的eeprom存储器,一者其受工艺的影响较大,有些成熟的工艺线并不提供eeprom的ip,使得芯片开发者没有任何选择的余地。如果需要使用eeprom,必须采用外置存储芯片。如此一来安全性、可靠性和集成性不能让人满意。二者其成本较高,相同单位容量的eeprom比eflash价格更高。

技术实现思路

1、为解决上述技术问题,本发明的一种模拟eeprom的电路设计方法,所述电路设计方法基于模拟eeprom的结构、sram和eflash中的数据存储格式、操作时序搭建,操作时序包括初始化操作、写入操作、整理操作,先要初始化操作,然后写入操作,写满的时候会发起整理操作,整理完了继续写入操作,然后循环作业;初始化操作包括如下步骤:

2、步骤s501:遍历所有页的首地址,从第一个扇区开始,读取扇区的首地址,遍历完所有的32个区域,如果有数据页、擦除页则写入对应的寄存器;

3、步骤s502:判断是否在活动数据页,即32个区域里是否存在活动数据区域,如果不存在活动数据区域,则初始化操作已完成,如果存在活动数据区域;

4、步骤s503:从活动数据区域的下一个页开始,遍历该页并且加载数据,读取每页的首地址;

5、步骤s504:判断是数据页则准备加载数据跳转到下步骤s505,否则跳转到步骤s503;

6、步骤s505:逐条读取数据页中的有效数据以及数据的实际地址,把数据写入datasram同时把数据的实际地址写入对应的tag sram并且标记为有效;

7、步骤s506:是否所有的页已遍历完毕,如果是则初始化已完成,否则跳转到步骤s503;

8、写入操作包括如下步骤:

9、步骤s301,查看擦除页寄存器,是否有需要擦除但是还没有执行页擦除操作的页;判断是则跳转到步骤s304,否则跳转到步骤s302;

10、步骤s302,查看地址指针,是否已指向活动页的最后一个地址;判断是则跳转到步骤s303,否则跳转到步骤s305;

11、步骤s303,查看空白页寄存器,是否还有剩余;判断是则跳转到步骤s306,否则跳转到步骤s307;

12、步骤s304,执行页擦除操作:

13、判断是首页,则读取该页的擦除次数,把次数暂存在寄存器中,若不是首页则直接对该页进行一次页擦除操作;

14、判断是首页,则在完成以后把擦除次数加1写回到首地址,否则不需要执行该操作,页擦除操作完成;

15、步骤s305,对数据区的下一个空白页做初始化:

16、判断当前有活动页,则在上一个活动页写入非活动标记;

17、在下一个将要写入数据的空白页的首地址写入数据活动标记;

18、步骤s306,数据写入与维护:

19、读取tag sram得到旧数据的映射地址以及有效位,读取data sram得到可能存在的旧数据;

20、若有效位有效则跳转到下工序ⅰ,无效则跳转到工序ⅱ;

21、工序ⅰ,在旧数据的映射地址写入数据无效状态位,跳转到工序ⅱ;

22、工序ⅱ,把新数据写入活动区的下一条存储位置,同时写入实际地址以及有效状态位;

23、把新数据的映射地址写入tag sram,并且标注为有效;

24、步骤s307,转入整理操作;

25、整理操作包括如下步骤:

26、步骤s401,查看空白页寄存器,寻找一块新的页并且标记为替换区;

27、步骤s402,从tag sram读取有效数据,然后搬移到替换页,跳转到步骤s403;

28、步骤s403,判断是否把的data sram读取完毕;若是则跳转到步骤s405,否则跳转到步骤s404;

29、步骤s404,替换页的数据是否已经写满;若是则跳转到步骤s401,否则跳转到步骤s402;

30、步骤s405,把除了替换页以外的数据页全部标记为等待被擦除的状态;

31、步骤s406,把替换页的标记全部改成数据页,并且把最后一个替换页改成数据活动页。

32、在本发明的一个实施例中,整理操作中步骤s402中还具体包括如下工序:

33、工序1,从0地址开始逐条读tag sram,若没有读完则继续读取;

34、工序2,得到有效位,若该数据有效,则跳转到工序3,若该数据无效,则跳转到工序1;

35、工序3,读data sram得到数据;

36、工序4,把该数据写入到eflash替换区的下一条地址;

37、工序5,写tag sram更新当前数据的存储位置,跳转到工序1。

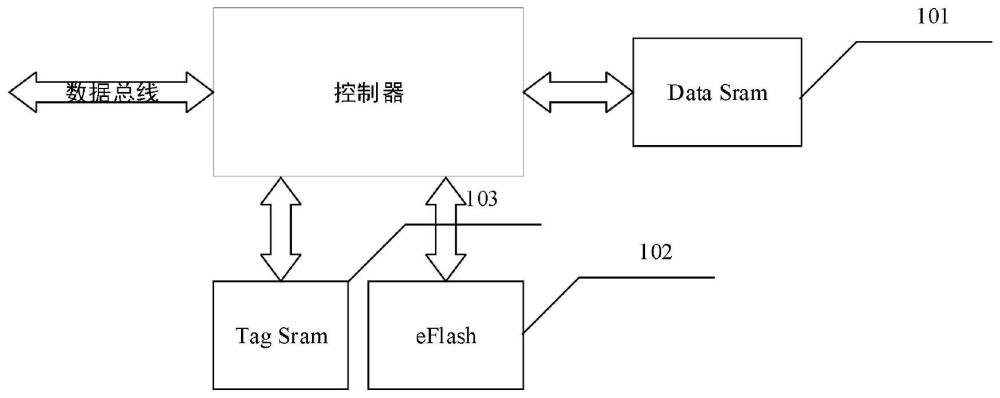

38、在本发明的一个实施例中,模拟eeprom的结构包括:

39、data sram;用于缓存写入eeprom的数据,其位宽和深度与实际需要的eeprom的位宽和深度保持一致,数据总线可以直接对其进行读写访问;

40、eflash,用于存储数据以便掉电后可以读回;eflash的大小决定了eeprom的寿命;eflash越大,eeprom的可擦写次数越多;每当新的数据写入data sram的时候都要同步备份到eflash中,每当出现断电复位以后都要从eflash中搜寻有效的数据以及该数据的实际地址,然后写入data sram以及对应的tag sram;

41、tag sram,用于存储有效标记和映射地址;有效位表示当前数据是否有效,映射地址表示当前数据备份于eflash中的物理地址;每当新的数据写入data sram时都会更新tagsram。

42、在本发明的一个实施例中,sram和eflash中的数据存储格式:

43、eflash划分为数据区和替换区,数据区用来备份eeprom的数据,而替换区用于当数据区写满的时候整理数据;数据区和替换区都有多页组成,其中每页的首地址用于标记该页的属性,剩余地址用于存储数据。

44、本发明的上述技术方案相比现有技术具有以下优点:本发明所述的电路设计方法,使用sram和eflash来模拟eeprom解决了当工艺厂无法提供eeprom的ip,而芯片的应用必须要集成eeprom的问题。

45、通过使用sram以及eflash来模拟eeprom既解决了上述两个问题,同时硬件层面还具备一定的灵活性。例如在应用需要大容量eflash的时候,可以把这部分sram和eflash作为通用sram和通用eflash使用;在应用需要eeprom的时候,通过分区操作可以把这部分sram和eflash作为模拟eeprom专用。

本文地址:https://www.jishuxx.com/zhuanli/20240731/183946.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

校验子解码系统的制作方法

下一篇

返回列表