行进存储器和计算机系统的制作方法

- 国知局

- 2024-07-31 19:53:21

本发明涉及行进存储器(mm,marching memory)的新配置和使用mm的新配置的新计算机系统,其以较低的能量消耗和较高的速度运行。

背景技术:

1、在专利文献(ptl)1-3中,t.nakamura和m.j.flynn已经提出了一种由包括存储单元阵列的行进主存储器(mmm)实现的mm)计算机系统。在专利文献1-3中,使用“行进”这一术语,因为每个存储单元都存储字节大小或字大小的移动并行数据,例如,就像移动部队的排列矩阵形式一样,表征了mmm的操作。mmm与用于驱动mm计算机系统中的处理器的时钟信号同步地以向mmm的输出端“行进”的方式,逐步传输存储的字节大小或字大小的并行数据流。mmm主动且依次向处理器提供所存储的连续的并行数据流,使得处理器可以利用所存储的并行数据流执行算术和逻辑运算。

2、在如专利文献1-3中所述的mm计算机架构中,因为字节大小或字大小的并行数据与用于驱动处理器的时钟信号同步传输,所以不需要单独位级单元的随机访问操作。然后,可以消除常规冯-诺依曼计算机系统中处理器和传统存储器之间固有存在的冯-诺依曼瓶颈,因此,通过mm计算机架构可以实现具有非常低功耗的超高速操作。

3、图19示出了在专利文献3中引用的较早的mm中m*2n矩阵的第i行上的第j位级单元mij*。位级单元mij*包括第一nmos晶体管qij1*、nmos晶体管qij2*以及与nmos晶体管qij2*并联连接的电容器cij*。第一nmos晶体管qij1*具有通过第一延迟元件dij1*连接到时钟线lclk的漏电极和通过第二延迟元件dij2*连接到前一位级单元的输出端的栅电极。nmos晶体管qij2*具有连接到第一nmos晶体管qij1*的源极的漏极、连接到时钟线lclk的栅极和连接到接地电位的源极。在图19中,连接第一nmos晶体管qij1*的源极和nmos晶体管qij2*的漏极的输出节点nout*用作位级单元mij*的输出端,并且输出节点nout*将存储在电容器cij*中的信号传输到下一位级单元mi(j+1)*。

4、在专利文献3中所述的较早的mm以诸如1.1伏电平等较低电源电压操作的情况下,当将略大于第一nmos晶体管qij1*的阈值电压vth的栅极电位施加到第一nmos晶体管qij1*的栅极电极,以导通第一nmos晶体管qij1*时,因为与1.1伏电平的电源电压相比,第一nmos晶体管qij1*产生相对较大的电压降,所以施加到下一位级单元mi(j+1)*的第一nmos晶体管qi(j+1)1*的栅电极的栅电位大幅下降。

5、因此,如果电源电压和阈值电压vth之间的差很小,则第一nmos晶体管qij1*的源电极处的电位有可能低于假设施加到下一位级单元mi(j+1)*的第一nmos晶体管qi(j+1)1*的栅电极的栅极电位。因此,当通过在传播路径中串联连接的多级位级单元mij1*、mi(j+1)1*、mi(j+2)1*、……时,因为每个串联的位级单元mij1*、mi(j+1)1*、mi(j+2)1*、……的输出端的饱和程度低于其输入端,所以在第一nmos晶体管qij1*、qi(j+1)1*、qi(j+2)1*、……的源电极的电位逐渐衰减,虽然每级位级单元mij1*、mi(j+1)1*、mi(j+2)1*、……需要将信号电压恢复到最大值。即,位级单元的输出端的电位最终可能变得小于阈值电压vth。结果,存储的信息不能被传输到下一个位级单元。

6、引文列表

7、专利文献

8、专利文献1:us-8949650b2

9、专利文献2:us-9361957-b2

10、专利文献3:ep-2815403b1

技术实现思路

1、技术问题

2、鉴于上述问题,本发明的一个目的是提供一种行进存储器和一种使用行进存储器的行进存储器计算机系统,其有助于以较低的电源电压准确传输存储的信息。

3、问题解决方案

4、本发明的第一方面在于一种行进存储器,该行进存储器被配置为存储字节大小或字大小的并行数据或指令的流,用于以处理器的时钟频率同步地沿着该流的方向朝着计算机系统中的处理器传输并行数据或指令的流。行进存储器包括奇数列(以下称为“o列”)和偶数列(以下称为“e列”)的周期交替阵列。每个o列具有在矩阵中沿列方向排列的前级单元的序列,以将字节大小或字大小的一组移动信息反相并存储。每个e列具有沿着列方向排列的后级单元的序列,以将由相邻奇数列反相的一组移动信息重新进行反相并存储。

5、本发明的第二方面在于一种行进存储器,其适用于具有多个流水线存储器阵列块的随机存取存储器(random-access capable memory),被配置为存储字节大小或字大小的并行数据或指令的流,用于以处理器的时钟频率同步地沿着该流的方向朝着计算机系统中的处理器传输并行数据或指令的流。在此处,行进存储器具有由本发明的第一方面规定的结构。

6、本发明的第三方面在于一种计算机系统,该计算机系统包括由本发明的第一方面规定的处理器和行进存储器。

7、本发明的第四方面在于一种计算机系统,该计算机系统包括处理器和主存储器。主存储器包括具有多个流水线存储器阵列块的随机存取存储器,以及作为在随机存取存储器和处理器之间的路径上分配的接口的行进存储器。所述行进存储器存储字节大小或字大小的并行数据或指令的流,用于以驱动计算机系统中的处理器的时钟频率同步地沿着该流的方向传输并行数据或指令的流,并且所述行进存储器主动且依次向处理器提供来自多个存储器阵列块的数据流或指令流,使得所述处理器能够利用存储的并行数据或指令的流执行算术和逻辑操作。在此处,行进存储器具有由本发明的第一方面规定的结构。

8、本发明的第五方面在于一种计算机系统中,该计算机系统包括处理器和主存储器。主存储器包括具有多个流水线存储器阵列块的随机存取存储器以及由行进存储器实现的高速缓冲存储器。所述行进存储器存储字节大小或字大小的并行数据或指令的流,用于以驱动计算机系统中的处理器的时钟频率同步地沿着该流的方向传输并行数据或指令的流,并且所述行进存储器主动且依次向处理器提供来自多个存储器阵列块的并行数据或指令的流,使得所述处理器能够利用存储的并行数据或指令的流执行算术和逻辑操作。在此处,行进存储器具有由本发明的第一方面规定的结构。

技术特征:1.一种行进存储器,被配置为存储字节大小或字大小的并行数据或指令的流,用于以处理器的时钟频率来同步地沿着所述流的方向朝着计算机系统中的处理器传输所述并行数据或指令的流,所述行进存储器包括:

2.根据权利要求1所述的行进存储器,其中,每个所述前级单元包括:

3.根据权利要求2所述的行进存储器,其中,每个所述前级单元还包括被配置为存储所述经反相的信号的前级存储电容器。

4.根据权利要求1所述的行进存储器,其中,每个所述后级单元包括:

5.根据权利要求4所述的行进存储器,其中,每个所述后级单元还包括后级耦合元件,所述后级耦合元件被配置为控制从分配在与所述偶数列的输入侧相邻布置的所述奇数列中的一个中的相邻前级单元的输出端传输所述一组移动信息中的信号中的一个。

6.一种行进存储器,适用于具有多个流水线存储器阵列块的随机存取存储器,所述行进存储器被配置为存储字节大小或字大小的并行数据或指令的流,用于以处理器的时钟频率来同步地沿着所述流的方向朝着计算机系统中的处理器传输所述并行数据或指令的流,所述行进存储器包括:

7.一种计算机系统,包括:

8.一种计算机系统,包括:

9.一种计算机系统,包括:

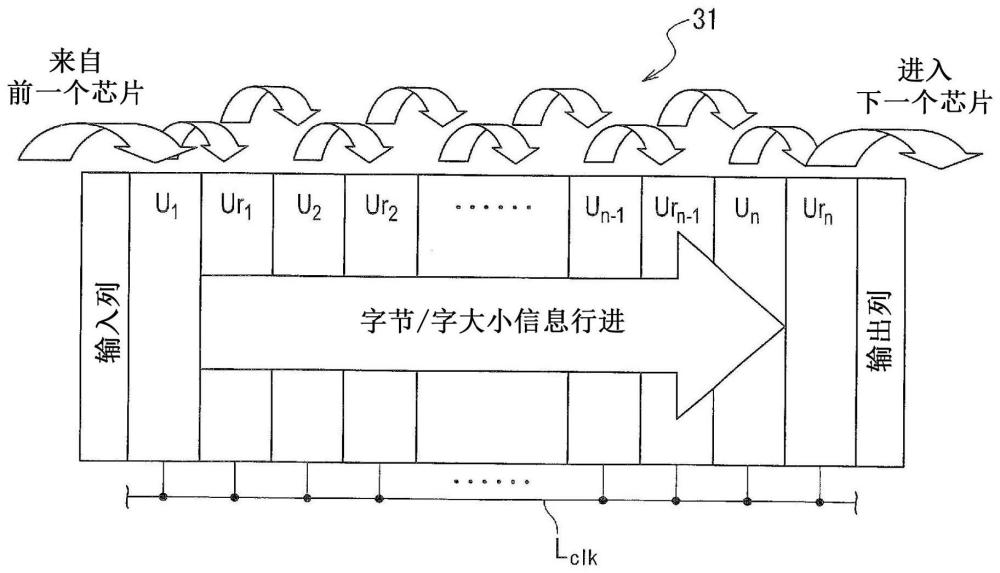

技术总结本发明公开了行进存储器和计算机系统。一种行进存储器(31)包括周期交替的奇数列(U<subgt;1</subgt;、U<subgt;2</subgt;、……、U<subgt;n‑1</subgt;、U<subgt;n</subgt;)和偶数列(Ur<subgt;1</subgt;、Ur<subgt;2</subgt;、……、Ur<subgt;n‑1</subgt;、Ur<subgt;n</subgt;)的阵列。每个奇数列(U<subgt;1</subgt;、U<subgt;2</subgt;、……、U<subgt;n‑1</subgt;、U<subgt;n</subgt;)具有沿列方向排列的前级单元的序列,以存储字节大小或字大小的一组移动信息。每个偶数列(Ur<subgt;1</subgt;、Ur<subgt;2</subgt;、……、Ur<subgt;n‑1</subgt;、Ur<subgt;n</subgt;)具有沿着列方向排列的后级单元的序列,以存储该组移动信息,使得可以同步、逐步地、沿着垂直于列方向的方向传输该组移动信息。技术研发人员:中村维男,迈克尔·J·弗林受保护的技术使用者:中村维男技术研发日:技术公布日:2024/5/9本文地址:https://www.jishuxx.com/zhuanli/20240731/184532.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表