具有带符号计算权重数据的紧凑存储的存储器内计算系统的制作方法

- 国知局

- 2024-07-31 19:58:38

实施例涉及存储器内计算电路,尤其涉及支持带符号的计算权重数据的紧凑存储以及多位格式的特征或系数数据的处理。

背景技术:

1、存储器内计算(imc)系统将信息存储在存储器阵列的位单元中并在位单元级执行计算。由imc系统执行的计算的一个示例是乘法和累加(mac)操作,其中输入数字阵列(x值,也称为特征或系数数据)与存储在存储器中的计算权重阵列(g值)相乘,并且将乘积加在一起以生成输出数字阵列(y值)。

2、

3、

4、通过在存储器中的位单元级执行这些计算,imc系统不需要在存储器设备和计算设备之间来回移动数据。因此,消除了与设备之间的数据传输带宽相关联的限制,并且可以以更低的功耗来执行计算。

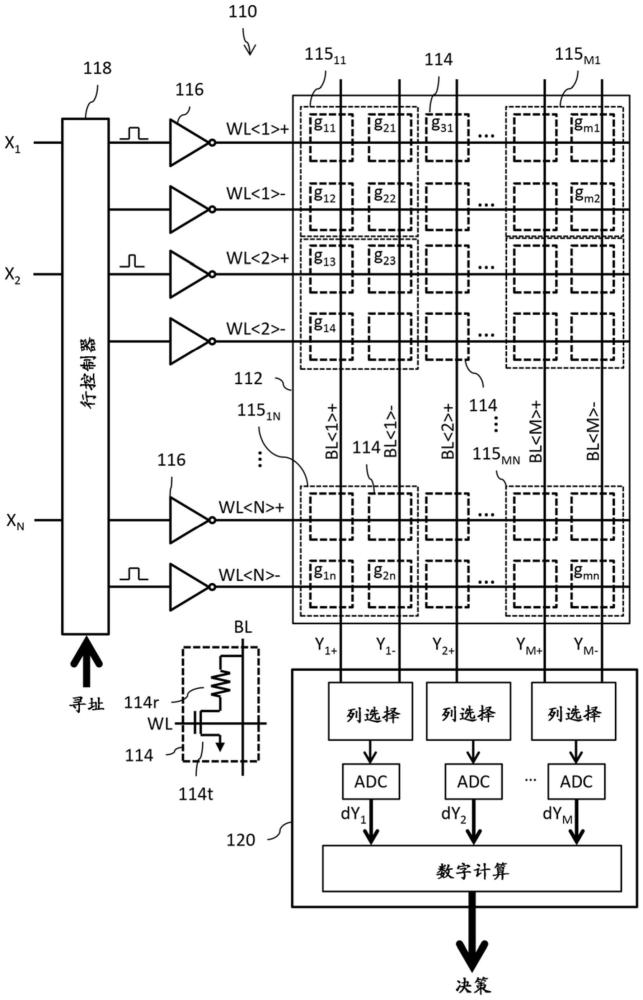

5、参考图1,图1示出了模拟存储器内计算电路10的示意图。电路10利用由多个以具有m列和n行的矩阵格式布置的存储单元14形成的存储器阵列12。每个存储器单元14被编程为存储与存储器内计算操作的计算权重(也称为内核数据)相关的数据位gab,其中a是从1到m的整数,并且b是从1到n的整数。计算权重的每一位具有例如由存储器单元14中的可编程跨导表示的逻辑“1”值或逻辑“0”值。

6、在存储器阵列12的实施例中,每一存储器单元14包括由作为开关元件操作的选择电路(mosfet晶体管、bjt晶体管、二极管装置等)14t和提供可编程跨导的可变电阻元件14r形成的相变存储器(pcm)单元。在mosfet晶体管用于选择电路14t的情况下,mosfet晶体管的控制节点(栅极)连接到字线wl。mosfet晶体管的源极-漏极路径与位线bl和参考节点(例如,源极线或地)之间的可变电阻元件14r串联连接。更具体地,mosfet晶体管的漏极连接到可变电阻元件14r的第一端子,mosfet晶体管的源极连接到参考节点,并且可变电阻元件14r的第二端子连接到位线bl。

7、如本领域技术人员所熟知的,pcm型存储器单元14被配置为使用相变材料(例如硫属化物)来存储数据,该相变材料能够根据传递到其的热量而在非晶相和晶相之间稳定地转变。非晶相和晶相呈现两个或更多个不同的电阻(对应于可变电阻元件14r),换句话说,两个或更多个不同的跨导,其用于区分可编程到存储器单元中的两个或更多个不同的逻辑状态。非晶相呈现相对较高的电阻(即,较低的跨导),并且因此当通过在选择电路14t的门(gate)处断言字线信号来选择时,在此状态下由编程的存储器单元从位线bl吸收的电流相对较小。相反,晶相呈现相对较低的电阻(即,较高的跨导),并且因此当通过在选择电路14t的门处断言字线信号来选择时,在此状态下编程的存储器单元从位线bl吸收的电流相对较大。

8、在用于两个不同逻辑状态的特定但非限制性示例的实施例中:非晶相可表示针对相关联的系数权重将存储器单元编程为逻辑“0”(或复位状态),并且结晶相可表示针对相关联的系数权重将存储器单元编程为逻辑“1”(或设置状态)。

9、应了解,其它存储器单元类型可备选地用于阵列12。例如,可以使用磁阻随机存取存储器(mram)单元或电阻随机存取存储器(rram)单元。存储器单元可替换地包括静态随机存取存储器(sram)单元。

10、每个存储单元14包括字线wl和位线bl。矩阵的公共行中的存储器单元14通过公共字线wl<b>彼此连接。矩阵的公共列中的存储单元14通过公共位线bl<a>彼此连接。

11、每个字线wl<b>由字线驱动器电路16利用由行控制器电路18生成的脉冲字线信号来驱动。字线驱动电路16可以被实现为cmos驱动电路(例如,形成逻辑反相器电路的串联的p沟道和n沟道mosfet晶体管对)。

12、行控制器电路18接收用于存储器内计算操作的寻址信号(address),并且响应于此执行选择字线wl<1>到wl<n>中的哪些字线将在模拟存储器内计算操作期间被同时并行访问(或激励actuated)的功能。行控制器电路18进一步接收用于存储器内计算操作的特征或系数数据xb,并且响应于此而针对每一相应的经激励字线wl<b>控制所生成的脉冲字线信号的宽度(即,接通时间ton)。该功能是根据所接收的特征或系数数据x的数字值对所施加的字线信号进行脉宽调制(pwm)控制的形式。

13、图1仅以示例方式说明响应于所接收的具有脉冲字线信号的地址而同时激活所有字线wl<1>,...,wl<n>,所述脉冲字线信号具有由对应系数数据x1,......,xn的数字值设置的脉冲宽度。当然,应了解,模拟存储器内计算操作可备选地利用少于存储器阵列的所有行的同时激励(通过寻址信号选择或通过给定系数数据xb的零值)。

14、在位线bl<a>上生成的模拟信号ya取决于存储在列的b=1到n存储器单元14中的计算权重gab的位的逻辑状态和施加到那些存储器单元14的字线wl<1>,......,wl<n>的脉冲字线信号的宽度。更具体地,应当理解,每个存储器单元14贡献与其成比例xb×gab的位线bl放电电流。因此,在图1所示的将字线信号16同时施加到字线wl<1>,......,wl<n>的示例中,在位线bl<1>上生成的模拟信号y1与由于x1×g11,x2×g12......,和xn×g1n引起的放电电流的总和成比例。

15、列处理电路20对m列的每个位线bl<a>上的模拟信号ya进行感测和采样,并使用模数转换器电路将模拟信号转换成相应的数字信号dya。尽管图1示出了为每列提供一个模数转换器(adc),但是应当理解,列处理电路20中的adc资源可以备选地由使用时分复用的多列共享。列处理电路20还可以包括数字信号处理电路,用于对数字信号dya执行数字计算和运算,以生成用于存储器内计算操作的决策输出。

16、尽管图1中未明确示出,但应了解,电路10进一步包含所属领域的技术人员已知的常规行解码、列解码和读写电路,其用于结合使用以将数据位(例如,计算权重数据)写入到存储器阵列12的存储器单元14并从存储器阵列12的存储器单元14读取数据位。该操作被称为常规的存储器访问模式,并且与上述模拟存储器内计算操作不同。

17、现在参考图2,图2示出了行控制器18的电路图。为每个字线wl<b>提供锁存电路52b以锁存系数数据xb的数字值的对应数字值。例如,该锁存操作可以取决于地址信号(address),该地址信号被解码以控制锁存电路52b锁存对应字线wl<b>的系数数据xb。为每个字线wl<b>提供控制电路50b。控制电路50b从锁存电路52b接收全局启动信号(start)和相关系数数据xb。如果锁存器值为零,则全局启动信号被阻断,并且没有字线信号被断言用于存储器中的模拟计算操作。否则,锁存电路52b将断言其输出信号startb,以控制在模拟存储器内计算操作期间断言的对应字线wl<b>。全局计数器电路54从存储器内计算操作开始时的零复位开始递增计数值(count)。每个字线wl<b>的比较电路56b连接到锁存电路52b,并将计数值count与系数数据xb的锁存数字值进行比较。当计数值count满足或超过锁存的数字值时,比较电路56b的输出被断言。组合逻辑电路58b对解码器电路50b和匹配电路56b的输出进行逻辑组合,以产生施加到字线wl<b>的驱动器电路16的脉冲字线信号。在一个实施例中,组合逻辑电路58b是逻辑与非门。

18、行控制器18内的电路的操作如下:在存储器内计算操作开始时,由锁存电路521至52n锁存系数数据x1至xn的数字值,并且复位全局计数器54。如果锁存的数据值是非零的,则解码器电路50b的startb信号输出被断言为逻辑高(响应于全局启动信号),并且与非门58b的输出被断言为逻辑高以提供字线信号脉冲的前缘。然后全局计数器54开始递增(增加incrementing)计数值。当递增计数值满足或超过由锁存电路52b锁存的系数数据xb的数字值时,比较电路56b的结束信号输出被断言为逻辑高,并且与非门58b的输出转变为逻辑低以提供字线信号脉冲的后缘。因此,所生成的脉冲字线信号的脉冲宽度(即,接通时间ton)取决于在存储器内计算操作期间用于递增计数值以达到系数数据xb的数字值所需的时间量。

19、现在参考图3,其示出了与包括详细描述的整体存储器内计算操作有关的电路10的操作的简化时序图。在时间t1,锁存控制信号被断言以使锁存电路521至52n锁存系数数据x1至xn的数字值,并且整个存储器内计算操作开始。我们在此假设上文所论述且图1中所示的示例,其中响应于所加载的非零系数数据而同时选择存储器单元14的所有行,并且响应于startb信号而以脉冲字线信号在时间t2处同时激活对应于特征或系数数据x1到xn的字线wl<1>到wl<n>。同样在时间t2,先前复位的计数值开始增加。在时间t3处,递增计数值满足或超过系数数据x1的数字值,并且字线wl<1>上的字线信号脉冲终止。在时间t4处,递增计数值满足或超过系数数据x3的数字值,并且字线wl<3>上的字线信号脉冲终止。在时间t5处,递增计数值满足或超过系数数据x2和xn的数字值,并且字线wl<2>和wl<n>上的字线信号脉冲终止。在时间t6,startb信号被解除断言,并且count值被复位。在时间t7,对位线bl<1>至bl<m>上的模拟信号y1至ym进行采样以进行模数转换,并且整个存储器内计算操作结束。

20、应当认识到,特征或系数数据的值可以是带符号的,并且计算权重数据的值也可以是带符号的。本领域中需要支持带符号的mac操作的性能。

技术实现思路

1、在实施例中,存储器内计算电路包括:一种存储器阵列,其包括以具有多行和多列的矩阵布置的多个存储器单元,其中存储器单元群组存储用于存储器内计算(imc)操作的计算权重,所述存储器内计算(imc)操作是用第一乘法和累加(mac)细化和第二mac细化执行的,存储器单元群组的每行包括耦合到存储器单元群组中的第一存储器单元的正字线和耦合到存储器单元群组中的第二存储器单元的负字线,并且存储器单元群组的每列包括耦合到存储器单元群组的第一和第二存储器单元的位线;行控制器电路,行控制器电路被配置为接收用于该imc操作的带符号的系数数据并且:a)在所述第一mac细化期间,当所述带符号的系数数据为正时,生成用于施加到所述正字线的脉冲字线信号,并且当所述带符号的系数数据为负时,生成用于施加到所述负字线的脉冲字线信号;以及b)在所述第二mac细化期间,当所述带符号的系数数据为正时,生成用于施加到所述负字线的脉冲字线信号,并且当所述带符号的系数数据为负时,生成用于施加到所述正字线的脉冲字线信号;以及列处理电路,其耦合到所述位线且被配置为:a)感测在第一mac细化期间在位线上生成的第一模拟信号;以及b)感测在第二mac细化期间在位线上生成的第二信号。

2、在实施例中,存储器内计算电路包括:一种存储器阵列,其包括以具有多行和多列的矩阵布置的多个存储器单元,其中存储器单元群组存储用于存储器内计算(imc)操作的计算权重,所述存储器内计算(imc)操作是用第一乘法和累加(mac)细化和第二mac细化来执行的,存储器单元群组的每行包含耦合到每一存储器单元群组中的第一和第二存储器单元的正字线和耦合到每一存储器单元群组中的第三和第四存储器单元的负字线,每列存储器单元群组包括耦合到每一存储器单元群组的第一和第三存储器单元的正位线和耦合到每一存储器单元群组的第二和第四存储器单元的负位线;行控制器电路,其被配置为接收用于imc操作的带符号的系数数据,并且当所述带符号的系数数据为正时,在所述第一和第二mac细化的每一者的期间生成用于施加到所述正字线的脉冲字线信号,并且当所述带符号的系数数据为负时,生成用于施加到所述负字线的脉冲字线信号;以及列处理电路,其耦合到所述正位线和所述负位线且被配置为:a)感测在所述第一mac细化期间在所述正位线上生成的第一模拟信号;以及b)感测在所述第二mac细化期间在所述负位线上生成的第二信号。

本文地址:https://www.jishuxx.com/zhuanli/20240731/184847.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表