用于静态随机存储器的测试结构的制作方法

- 国知局

- 2024-07-31 20:00:04

本公开的实施例主要涉及半导体领域,并且更具体地,涉及静态随机存储器的测试系统和测试方法。

背景技术:

1、sram (static random-acess memory) 由于具备读写速度快、工作稳定等特点,因此在便携式移动电子社设备、片上系统(systems on chip, soc)等设备中扮演了重要的角色。一般情况下,工艺方面造成良率损失的主要原因有以下一些情况:1)工艺上金属层出现短路;2)工艺上通孔(via)或接触孔(contact)出现短路或接触不良;3)晶圆一致性不好,某部分区域有一定良率,但其他区域无良率或良率很低;4) sram位单元(bitcell)区域由于小于常规规则,实际工艺裕度不够,出现短路情况;以及5)sram位单元器件在不同工艺角下,性能不同,有些工艺角下与预定目标范围偏差较大,导致良率较低。

2、定位sram中的接触孔造成的失效问题的一种常规方法是:通过器件性能参数的分布找到失效sram区域中具体的失效位置,然后采用聚焦离子束(fib)制样来制备样品并通过透射电子显微镜(tem)进行观察,在tem切片中来定位sram失效原因。然而,这对流片是具有破坏性,并且无法修复。此外,这种定位方法受限于tem制样质量与切片位置。定位sram失效方式被动,周期性较长且成效甚微。

技术实现思路

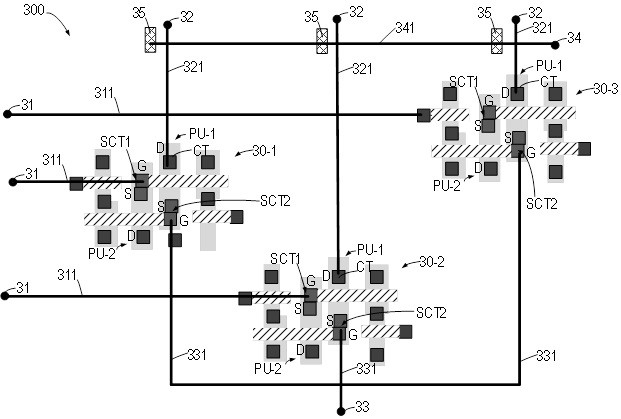

1、根据本公开的第一方面,提供了一种用于静态随机存储器的测试系统。该测试系统包括:多个待测存储单元,多个待测存储单元包括多个待测晶体管,多个待测晶体管中的每一者包括共享接触孔;以及测试结构,用于测量多个待测晶体管的多个共享接触孔,包括:第一焊盘集,包括多个第一焊盘,多个第一焊盘电连接至多个待测晶体管的多个栅极;第二焊盘集,包括多个第二焊盘,多个第二焊盘电连接至多个待测晶体管的多个漏极;第三焊盘,电连接至多个待测晶体管的多个源极;以及第四焊盘,电连接至多个待测晶体管的多个基极。

2、在一些实施例中,多个待测存储单元中的待测存储单元包括第一上拉晶体管和第二上拉晶体管,以及待测晶体管为第一上拉晶体管和第二上拉晶体管中的一者,共享接触孔包括将一者的栅极电连接至第一上拉晶体管和第二上拉晶体管中的另一者的源极的第一共享接触孔;以及测试结构被配置为测量第一共享接触孔。

3、在一些实施例中,第一焊盘集中的每个第一焊盘在第一共享接触孔处电连接至一者的栅极。在一些实施例中,第二焊盘集中的每个第二焊盘电连接至一者的漏极。在一些实施例中,待测存储单元还包括将一者的源极电连接至第一上拉晶体管和第二上拉晶体管中的另一者的栅极的第二共享接触孔;以及第三焊盘在第二共享接触孔处电连接至一者的源极。

4、在一些实施例中,测试结构还包括:多个第一金属线,沿着第一方向延伸且被配置为将第一焊盘集中的多个第一焊盘分别电连接至多个待测晶体管的多个栅极;以及多个第二金属线,沿着与第一方向不同的第二方向延伸且被配置为将第二焊盘集中的多个第二焊盘分别电连接至多个待测晶体管的多个漏极。

5、在一些实施例中,测试系统还包括:多个第三金属线,被配置为将第三焊盘分别电连接至多个待测晶体管的多个源极;以及第四金属线,被配置为将第四焊盘分别电连接至多个待测晶体管的多个基极,其中多个待测晶体管的多个基极沿着同一条线排列。

6、在一些实施例中,用于多个待测晶体管的多个共享接触孔中的至少一些的尺寸在不同的两个方向中的至少一个方向上增大或减小。在一些实施例中,用于多个待测晶体管的多个共享接触孔中的至少一些在不同的两个方向上中的至少一个方向上发生偏移。在一些实施例中,用于多个待测晶体管的多个共享接触孔中的至少一些所在的有源区的宽度增大或减小。

7、根据本公开的第一方面,提供一种使用根据测试系统来测试静态随机存储器的方法。该方法包括:在第一焊盘集的第一数目的第一焊盘上施加目标电压,第一数目的第一焊盘被电连接至第一数目的待测晶体管的栅极;在第一数目的待测晶体管的漏极处,测量漏极电流;确定目标电压和漏极电流之间的关系;以及基于所确定的关系,确定待测晶体管的待测共享接触孔的性能。

8、在一些实施例中,第一数目的待测晶体管的第一数目共享接触孔中的至少一些的尺寸在不同的两个方向中的至少一个方向上增大或减小。在一些实施例中,第一数目的待测晶体管的第一数目共享接触孔中的至少一些在不同的两个方向上中的至少一个方向上发生偏移。在一些实施例中,第一数目的待测晶体管的第一数目共享接触孔中的至少一些所在的有源区的宽度增大或减小。在一些实施例中,该方法还包括根据所确定的待测共享接触孔的性能,调整用于制造共享接触孔的工艺参数。

9、在根据本公开的测试系统和测试方法中,该测试结构无需切片,对流片没有破坏性,仅需要布置一些焊盘和金属线即可,能够缩短测试时间,使得测试过程更加简单。此外,通过使得源极端和基极端分别共用一个焊盘接口,能够很大程度上节省测试结构的面积。独立地设计用于栅极和漏极的焊盘,可以随意的来选择待测的器件,灵活。根据实际的制程需求,,继续添加需要测试的晶体管,每增加一个测试对象,只会增加2个焊盘,测试对象越多,越发节省测试面积,也就是说仅需要增加用于每个待测晶体管的栅极和漏极的焊盘。

10、应当理解,技术实现要素:部分中所描述的内容并非旨在限定本公开的实施例的关键或重要特征,亦非用于限制本公开的范围。本公开的其它特征将通过以下的描述变得容易理解。

技术特征:1.一种用于静态随机存储器的测试系统,包括:

2.根据权利要求1所述的测试系统,其中所述多个待测存储单元中的待测存储单元包括第一上拉晶体管和第二上拉晶体管,以及

3.根据权利要求2所述的测试系统,其中:

4.根据权利要求2所述的测试系统,其中:

5.根据权利要求2所述的测试系统,其中所述待测存储单元还包括将所述一者的源极电连接至所述第一上拉晶体管和所述第二上拉晶体管中的另一者的栅极的第二共享接触孔;以及

6.根据权利要求1所述的测试系统,其中所述测试结构还包括:

7.根据权利要求1所述的测试系统,还包括:

8.根据权利要求1所述的测试系统,其中用于所述多个待测晶体管的多个共享接触孔中的至少一些的尺寸在不同的两个方向中的至少一个方向上增大或减小。

9.根据权利要求1所述的测试系统,其中用于所述多个待测晶体管的多个共享接触孔中的至少一些在不同的两个方向上中的至少一个方向上发生偏移。

10.根据权利要求1所述的测试系统,其中用于所述多个待测晶体管的多个共享接触孔中的至少一些所在的有源区的宽度增大或减小。

11.一种使用根据权利要求1所述的测试系统来测试静态随机存储器的方法,包括:

12.根据权利要求11所述的方法,其中所述第一数目的待测晶体管的第一数目共享接触孔中的至少一些的尺寸在不同的两个方向中的至少一个方向上增大或减小。

13.根据权利要求11所述的方法,其中所述第一数目的待测晶体管的第一数目共享接触孔中的至少一些在不同的两个方向上中的至少一个方向上发生偏移。

14.根据权利要求11所述的方法,其中所述第一数目的待测晶体管的第一数目共享接触孔中的至少一些所在的有源区的宽度增大或减小。

15.根据权利要求12至14中任一项所述的方法,还包括根据所确定的所述待测共享接触孔的性能,调整用于制造所述共享接触孔的工艺参数。

技术总结本公开的示例实施例涉及一种用于静态随机存储器的测试结构。多个待测存储单元包括多个待测晶体管,多个待测晶体管中的每一者包括共享接触孔。该测试结构用于测量多个待测晶体管的多个共享接触孔,包括:第一焊盘集,包括多个第一焊盘,多个第一焊盘电连接至多个待测晶体管的多个栅极;第二焊盘集,包括多个第二焊盘,多个第二焊盘电连接至多个待测晶体管的多个漏极;第三焊盘,电连接至多个待测晶体管的多个源极;以及第四焊盘,电连接至多个待测晶体管的多个基极。根据本公开的测试系统无需切片、操作简单省时且能够节省SRAM测试结构的面积。技术研发人员:请求不公布姓名,请求不公布姓名受保护的技术使用者:全芯智造技术有限公司技术研发日:技术公布日:2024/6/5本文地址:https://www.jishuxx.com/zhuanli/20240731/184955.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。