可进行SRAM操作的电擦除非易失性半导体存储装置的制作方法

- 国知局

- 2024-07-31 20:01:19

本技术实施例涉及半导体,特别涉及一种可进行sram操作的电擦除非易失性半导体存储装置,能够进行易失性ram操作和ram数据的非易失性存储。

背景技术:

1、如《日经技术在线》(nikkei technology online special,3月,2014年)特刊所示,静态随机存取存储器(static random access memory,sram)可实现高速随机存取和低功耗,如以下示例所示,它的应用领域非常广泛,包括网络工作设备、通信基础设施设备、测量仪器、成像系统以及工业设备和游戏机。必要时,还可使用电池备份sram,在系统关闭后,用额外的电池来维持sram中的数据。不过,在这种情况下,由于电池老化,sram的数据保存时间被限制在三年左右。目前,随机存储器(random access memory,ram)操作的非易失性静态存储器(non-volatile sram,nvsram)已经被应用于智能电表、可编程逻辑控制器(programmable logic controller,plc)、工厂自动化(factory automation,fa)设备、信息技术(information technology,it)设备、办公自动化(office automation,oa)设备、汽车和可穿戴设备中,内存容量可高达16mbit。在上述设备的系统中,该nvsram可通过标准sram控制信号和控制时序,以与传统sram相同的方式运行。电源关闭或发生断电时,nvsram芯片可检测到电源电压下降,并将芯片中sram单元中的数据存储到非易失性存储单元中(称为存储操作)。此外,当接通电源或从断电中恢复时,nvsram芯片非易失性存储单元中的数据可返回sram单元(称为回读操作),如此主机系统可在断电中断时使用非易失性中保存的数据。这样做的好处是,开机后可以使用关机时中断点的非易失性数据恢复处理。

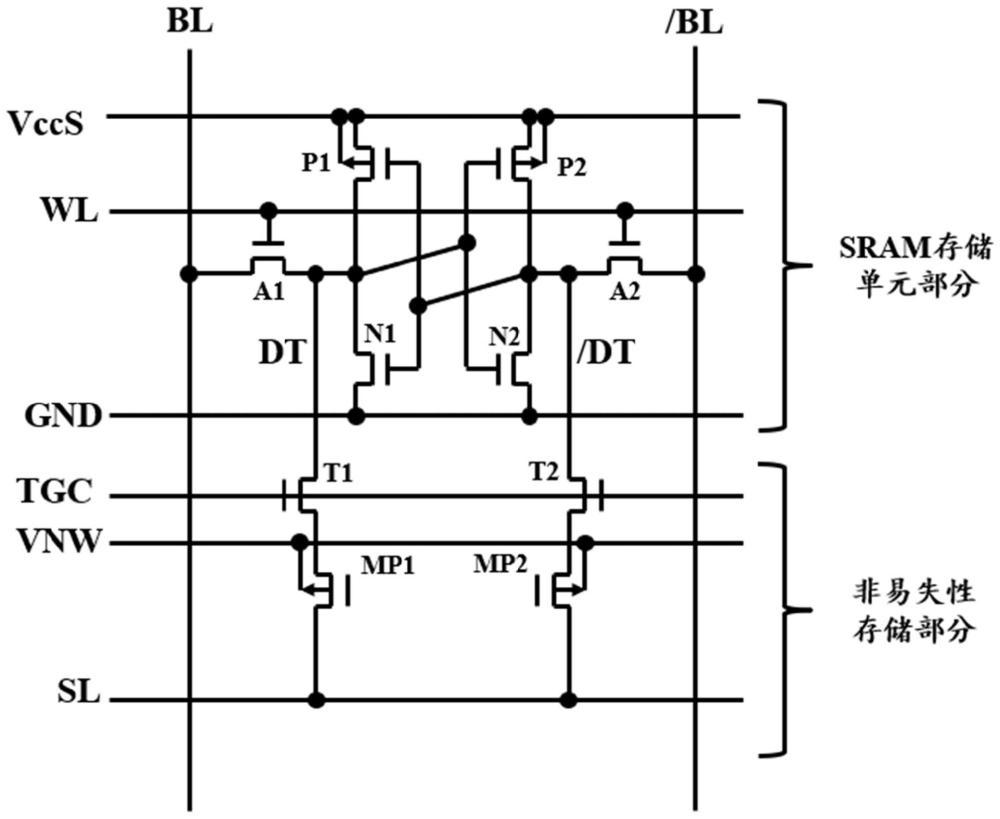

2、图1显示了专利文献1(us5065362a)和非专利文献1[nonvolatile sram(nvsram)basis,ravi prakash,white paper,cypress semiconductor corp,2016]中所示的传统现有技术中nvsram存储单元的电路图。现有技术中nvsram的存储单元由sram存储单元部分和非易失性存储部分组成。sram存储单元部分的配置与已知的sram存储单元相同,在本示例中,它包括一个标准配置cmos(complementary metal oxide semiconductor)触发器(由晶体管p1、晶体管n1、晶体管p2和晶体管n2构成)和两个接入晶体管(晶体管a1和晶体管a2),即典型的6个晶体管的配置。非易失性存储部分由两组三个元件(串联的晶体管t1、晶体管m1和晶体管t3以及串联的晶体管t2、晶体管m2和晶体管t4,以下简称t1-m1-t3和t2-m2-t4)组成,每组在非易失性存储晶体管m1和m2的两端分别串联一个晶体管。t1-m1-t3和t2-m2-t4分别位于sram存储单元部分的存储节点dt和电源vcc之间以及sram存储单元部分的存储节点/dt和电源vcc之间。图1还显示了用于操作nvsram存储单元的控制信号和电源。其中,vcc表示从外部施加到nvsram存储单元的电源电压,vccs表示从nvsram中的vcc产生并只供应给sram存储单元部分的电源。与已知的sram相同,gnd是接地电位,bl是位线,/bl是与其反相数据相对应的反相位线,wl是sram存储单元部分中的字线。sram存储单元部分的存储节点是dt和/或dt。非易失性存储部分的“recall”和“store”分别是“回读操作”期间和“存储操作”期间的控制信号,vpe表示在对非易失性存储部分的非易失性存储晶体管(m1和m2)进行擦除操作和编程操作时所使用的擦除/编程电源。在现有技术中,vccs和vpe由外部电源vcc产生,并由nvsram芯片中的已知电路(图中未示出)控制。

3、图2显示了现有技术中nvsram存储单元的运行示例,显示了nvsram存储单元每次运行时各电源电压和各控制信号随时间变化的情况(时序图)。虽然这是现有技术的一个操作示例,但由于nvsram存储单元电路配置不同,该操作并不一定与专利文献1中描述的操作细节一致。图3显示的是非易失性存储晶体管m1和m2的栅极阈值电压(vth)与下面的操作描述相对应。

4、nvsram存储单元操作可大致分为以下三个部分:

5、(1)recall操作(回读操作)

6、接通电源时,将存储在非易失性存储部分的非易失性数据传输到sram存储单元部分;

7、(2)sram操作(静态存储操作)

8、与传统的sram相同;

9、(3)store操作(存储操作)

10、当电源断开时,将sram存储单元部分中的数据复制到非易失性存储部分以进行备份。

11、由于sram存储单元部分的配置与现有技术中的sram相同,因此省略了上述(2)中的sram操作。下面将对每种操作进行说明。

12、现有技术nvsram存储单元的recall操作将根据专利文献1进行说明。据此,非易失性存储晶体管m1和m2是氧化硅氮化物半导体(silicon oxide nitride semiconductor,snos)结构的n型沟道非易失性存储晶体管。图3显示了非易失性存储晶体管的vth状态与数据“1”或“0”之间的关系。如果数据为“1”,则m1处于擦除状态,其vth为负值,m2处于编程状态,其vth为正值;如果数据为“0”,则m1处于编程状态,其vth为正值,m2处于擦除状态,其vth为负值。此外,正常运行时,vcc和vccs设置为5v。以下将以nvsram存储单元的非易失性存储部分的初始数据为“0”时的操作进行说明。首先,打开nvsram存储单元的电源vcc,nvsram存储单元中的电路开始充电。在t1时刻,电压达到可进行电路操作的vcc,图中所示的每个信号被固定在l(gnd)或h(vcc)。此时,sram存储单元部分的电源vccs保持在接地电位。因此,sram存储单元部分的bl、/bl、dt和/dt根据t1时刻之前的状态可能会有剩余电荷。从t2时刻到t3时刻期间,wl设置为h,上述节点(电路节点)放电并设置为l。在t4时刻,当recall=h时,非易失性存储部分的非易失性存储晶体管m1和m2通过t1和t2由vcc充电。此时,由于vpe=l,在擦除状态下vth为负的m2处于导通状态,而在编程状态下vth为正的m1处于关断状态。因此,t4的漏极通过m2向vcc充电,t3没有充电,其漏极在放电状态下保持低电平。接下来,在t5时刻,store=h,t3和t4接通,sram存储单元部分的电源vccs上升。t3和t4处于打开状态,但/dt通过t2-m2-t4充电,dt未充电,因为t1-m1-t3中的m1处于关闭状态。之后,当vccs升至高于sram存储单元部分的工作电压,sram存储单元部分的p2和n1接通,p1和n2关断时,dt设置为l,/dt设置为h,m1和m2各自的存储状态(m1=编程状态,m2=擦除状态)被传输至sram存储单元部分,dl=l以及/dl=h作为数据“0”传输至sram存储单元部分以完成回读操作。如此,在sram存储单元部分中设置的非易失性存储部分中存储的数据“0”就可以启动后续的sram操作。

13、接下来将介绍现有技术nvsram存储单元的存储操作。除上述回读操作外,在sram操作期间还设置了recall=l以及store=h。通过检测电源vcc中的电压下降启动存储操作。在图2中的t8时刻,检测到电压下降到预定电压,wl=l,随后bl和/bl放电并设置为l。此时,sram存储单元部分的节点dt和/dt的电压保持不变(在本例中,dt=l和/dt=h)。接下来,在t9时刻至t10时刻期间,对vpe施加负高压(例如-15v)。正电荷被注入到紧靠非易失性存储晶体管m1和m2的栅极下方的氮化物层中,m1和m2的vth都为负值(擦除操作)。

14、接下来,在t11时刻至t12时刻期间,向vpe施加正高压(例如+15v),程序运行开始。由于recall=l以及store=h,t1和t2因为recall=l应该关断,t4因为store=h应该接通,但因为/dt=h和t2因为/dt=h而关断,所以t4关断。因此,m2的源极和漏极成为浮动电位,m2的沟道电压因与栅极电压vpe的耦合(电容耦合)而升高,无法获得编程操作所需的电位差。因此,m2无法编程,仍处于擦除状态。另一方面,m1连接时t1处于关断状态,但由于store=h和dt=l,因此t3接通,m1的通道设置为l=gnd。因此,由于m1的沟道电位即使在施加vpe时也保持为gnd,负电荷被注入到非易失性存储晶体管m1栅极正下方的氮化物层中,其vth变为正值,只有m1处于编程状态(编程操作)。因此,m2处于擦除状态,m1处于编程状态,这与上述回读操作期间非易失性存储部分的存储状态数据“0”相同。通过这种方式,sram存储单元部分的数据“0”被传输到非易失性存储部分中,这样即使电源vccs随着vcc电源的下降而下降导致sram存储单元部分中的数据消失,非易失性存储晶体管m1和m2仍能继续保留该数据。

15、如上所述,现有技术的nvsram存储单元由总共12个元件组成,包括6个元件组成的sram存储单元部分以及6个元件组成的非易失性存储部分。非易失性存储部分具有氮化硅半导体(silicon oxide nitride oxide semiconductor,sonos)、金属氮化物半导体(metal nitride oxide semiconductor,mnos)、氮化硅半导体(silicon oxide nitridesemiconductor,snos)或浮栅晶体管作为非易失性存储晶体管。因此,它不能像传统sram存储单元那样,使用构成逻辑电路的互补式金属绝缘体半导体(metal insulatorsemiconductor,mis)晶体管的栅极和栅极绝缘膜结构来制造,也不能使用用于逻辑电路的传统互补mis晶体管。在逻辑电路用互补mis晶体管的传统制造工艺中,必须增加非易失性存储晶体管的制造工艺(例如,氮化膜的形成和加工过程,或双层多晶硅栅极的形成和加工过程)。

16、专利文献2(jp-a-2006-66529)公开了一种具有单层多晶硅结构的非易失性存储单元的现有技术,该存储单元可在用于逻辑电路的互补mis晶体管的常规制造工艺中制造。下面将参照附图进行说明。图4显示了一种单层多晶硅结构的非易失性存储单元的横截面结构,该结构可在用于逻辑电路的互补mis晶体管的生产过程中制造。在图4中,n型阱区24(平均磷浓度为2×10e17cm-3)和p型阱区23(平均硼浓度为3×10e17cm-3)形成于p型硅衬底21(电阻率为10ωcm)的表面区域。在n型阱区24中,n型杂质区33(参考图4)和p型杂质区28被深度为300nm的器件分离氧化膜22电隔离。选择晶体管st的源极29、漏极30、栅极绝缘膜25和选择栅极26均形成于p型阱区23中,并由深度为300nm的器件分离氧化膜22电隔离。在p型杂质区28和源极29之间,有覆盖n型阱区24和p型阱区23的栅极绝缘膜25,栅极绝缘膜25的上方有一个浮动栅极27。n型阱区24和浮动栅极27之间的重叠区域用作耦合电容c2,而p型阱区23和浮动栅极27之间的重叠区域用作存储晶体管mt的沟道32。因此,编程操作期间,n型阱区24与编程字线pwl的电位连接,并控制浮动栅极27的电位。此外,在读取操作期间,n型阱区24连接到源极线vss。在编程操作中,施加在n型阱区24上的正电压与施加在与编程位线pbl相连的p型杂质区28上的负电压之间的电位差被施加到p型杂质区28的结点上。由带间隧道现象(btbt,band to band tunneling)产生的热电子31被注入浮动栅极27,通过与n型阱区24的静电耦合,浮动栅极27被提升到正电位,电子被积聚。

17、图5显示了一种非易失性存储单元的等效电路图,该存储单元采用单层多晶硅结构,可使用用于逻辑电路的互补mis晶体管制造工艺来制造。在图5中,具有栅极电容c1的存储晶体管mt的浮动栅极与耦合电容c2相连接,源极与电荷注入区的结电容cj相连,存储晶体管mt的漏极与选择晶体管st相连,选择晶体管st的栅极连接读取字线rwl。选择晶体管st的漏极连接到读取位线rbl,电荷注入区连接到编程位线pbl,耦合电容c2连接到编程字线pwl。耦合电容c2的电容值被设计为等于存储晶体管mt的栅极电容和电荷注入区域的结电容cj的总和,与浮动栅极的静电耦合比约为0.5。

18、如图6所示的单层多晶硅结构的非易失性存储单元的平面结构,这种存储单元可以使用用于逻辑电路的互补mis晶体管制造工艺来制造。在图6中,有源区41横跨n型阱区34和p型阱区。在有源区41内布置有选择晶体管的漏极30、选择栅极(图中未示出)和源极29以及p型杂质区33。在源极29和p型杂质区33之间布置有一个浮动栅极(图中未示出),漏极30通过一个接触孔44连接到由第一金属膜46构成的读取位线rbl线45,第一金属膜46通过连接孔47连接到由第二金属膜构成的编程位线pbl线48。在读取数据时,n型阱区34充当编程字线和用于读取的共源线。

19、图7显示了现有技术中标准cmos工艺(单层多晶硅结构)制造的非易失性存储单元的工作电压条件。在编程操作(program)中,向编程字线pwl施加正电压(如3.3v,即电源电压),然后向编程位线pbl施加负电压(如-2v)。如此,由btbt产生的热电子被注入至浮动栅极。在此编程操作中,编程位线pbl上的电流约为100na,写入时间约为10μs,写入后存储晶体管的阈值电压约为5v。

20、在读取操作(read)中,向读取位线rbl施加约1v的电压,然后向选择晶体管的栅极rwl施加3.3v的电压(电源电压),存储晶体管接通。这是通过判断存储晶体管是处于导通或非导通状态来实现的。

21、有几种方法可以擦除具有单层多晶硅结构的非易失性存储单元,这种存储单元可以使用现有技术中用于逻辑电路的互补mis晶体管制造工艺来制造。第一次擦除操作(erase(1))是通过向编程位线pbl和编程字线pwl施加5v的正电压,并通过f-n隧道电流将电子从浮动栅极发射到p型杂质区来完成的。擦除时间约为200ms,擦除后存储晶体管的阈值电压约为0.5v。在第二次擦除操作(erase(2))中,向编程位线pbl和选择栅极rwl施加6v电压,以打开选择晶体管并将源极29充电至5.5v的电位。电子通过f-n隧道电流从浮动栅极发射到源极。擦除时间约为100ms,擦除后存储晶体管的阈值电压约为0.3v。

22、图8a至图8d显示了具有单层多晶硅结构的非易失性存储单元的制造工艺的各个步骤对应的截面结构,该存储单元可在现有技术中用于逻辑电路的互补mis晶体管的制造工艺中制造。每个截面图对应图6所示的平面结构中cc’所指示的方向。

23、图8a所示的制造工艺步骤中,通过如下方法在p型硅衬底121(电阻率10ωcm)表面的所需区域形成平面化浅沟槽隔离区124、一个n型阱区122和一个p型阱区123。通过干法刻蚀形成开口,采用化学气相沉积(以下简称cvd)法形成氧化硅膜,采用化学机械抛光(以下简称cmp)法形成深度300nm的平面化浅沟槽隔离区(以下简称sti)。然后通过热氧化法生长出厚度为10nm的表面氧化膜140。通过离子注入法(能量为1mev/注入剂量为1×10e13cm-2、能量为500kev/注入剂量为3×10e12cm-2和能量为150kev/注入剂量为1×10e12cm-2)植入p(磷)离子,以形成n型阱区122。通过离子注入法(能量为500kev/注入剂量为1×10e13cm-2、能量为150kev/注入剂量为3×10e12cm-2和能量为50kev/注入剂量为1×10e12cm-2)植入b(硼)离子,以形成p型阱区123。

24、在图8b所示的制造工艺步骤中包括以下工序。通过湿蚀刻法去除表面氧化膜后,用热氧化法生长出厚度为7nm的栅极氧化膜125,然后通过离子注入法将加速能量为10kev的p离子(注入量为4×10e15cm-2)注入到通过cvd法沉积的厚度为200nm的多晶硅薄膜中。注入后,用光刻法和干法蚀刻法处理薄膜,形成浮动栅极126和选择栅极127,然后用光刻法进行掩膜,再用离子注入法进行处理。p型杂质区128是通过注入加速能量为10kev的bf2(二氟化硼)离子(注入量为1.5×10e15cm-2)形成的,采用光刻法对光刻胶掩膜141进行图案化,并植入加速能量为10kev的as(砷)离子142(注入量为1.5×10e15cm-2)以形成选择晶体管的源极130和漏极129。

25、接下来图8c所示的制造工艺步骤中包括以下工序。用灰化法去除并清洗光刻胶掩膜141后,通过cvd法沉积形成厚度为80nm的氧化膜侧隔板131,并用通过回刻蚀法进行处理。仅向p型杂质区128注入加速能量为20kev的bf2离子(注入量为2×10e15cm-2),然后仅向源极130和漏极注入加速能量为30kev的as(砷)离子(注入量为2×10e15cm-2)。在氮气环境中进行于1000℃下进行10秒钟的高温热处理,在浮置栅极126和选择栅极127以及暴露的衬底表面上生长厚度为50nm的硅化钴薄膜132和硅化钴薄膜133,通过cvd法沉积氧化硅薄膜,形成厚度为800nm的接触夹层薄膜134,并通过cmp方法进行平坦化处理。通过光刻和干蚀刻开出孔径为0.3μm的接触孔,通过cvd法沉积和cmp法进行平坦化处理嵌入钨插片135。

26、图8d制造工艺步骤中,采用溅射法、光刻法和干法蚀刻法沉积厚度为500nm的铝制成的第一层金属互联层136和第一层金属互联层137,采用cvd法沉积氧化硅薄膜,采用cmp法平面化形成厚度为800nm的第一中间膜138。通过光刻和干蚀刻技术打开一个孔径为0.3μm的通孔,嵌入一个通过cvd沉积并通过cmp平面化的钨插片139。通过溅射法、光刻法和干法蚀刻法形成厚度为500nm的铝制第二金属布线143。该现有技术的标准cmos工艺(单层多晶硅结构)展示了完成非易失性存储单元主要部分的制造工艺,该非易失性存储单元可使用本现有技术的标准cmos工艺(单层多晶硅结构)制造。

技术实现思路

1、本技术一些实施例提供一种可进行sram操作的电擦除非易失性半导体存储装置,至少能够进行ram操作和ram数据的非易失性存储,降低非易失性半导体存储装置的制造成本的同时可以提高集成密度。

2、本技术实施例一方面提供了一种可进行sram操作的电擦除非易失性半导体存储装置,包括:存储单元,存储单元包括形成于半导体衬底表面的单层多晶硅栅互补mis晶体管;存储单元由sram存储单元部分和非易失性存储部分组成,sram存储单元部分由6个半导体元件组成,非易失性存储部分由4个半导体元件组成;sram存储单元部分包括一个cmos触发器,cmos触发器由n型沟道晶体管和p型沟道晶体管构成;cmos触发器具有互补的正相存储节点和反相存储节点,正相存储节点通过第一n型沟道晶体管与位线连接,反相存储节点通过第二n型沟道晶体管与反相位线连接;cmos触发器连接sram存储单元的电源电压vcc以及接地电压vss;第一n型沟道晶体管的栅极以及第二n型沟道晶体管的栅极连接字线;非易失性存储部分包括两组元件,每组元件包括2个半导体元件,其中,每组元件包括由n型沟道晶体管构成的传输栅晶体管以及由p型沟道晶体管构成的存储晶体管;传输栅晶体管和存储晶体管串联连接;不同传输栅晶体管的漏极分别对应连接sram存储单元部分的正相存储节点和反相存储节点;传输栅晶体管的栅极与第一控制信号相连;传输栅晶体管的源极与存储晶体管的漏极相连;存储晶体管的栅极设置为电气浮置;存储晶体管的源极与第二控制信号相连;存储晶体管的阱电极与第一阱电位相连;其中,存储单元包括10个半导体元件。

3、在一些实施例中,在存储单元的非易失性存储部分对存储晶体管进行擦除操作和编程操作的方法包括:在存储单元的非易失性存储部分对存储晶体管进行擦除操作期间:将连接到传输栅晶体管的栅极的第一控制信号设置为接地电压vss,从而关闭传输栅晶体管;向连接到存储晶体管的阱电极的第一阱电位施加等于或高于电源电压vcc且等于或高于编程操作时的阱电位的高电压;将存储晶体管的源极充电至电源电压vcc后,存储晶体管的源极电气浮置;在存储单元的非易失性存储部分对存储晶体管进行编程操作期间:将连接到传输栅晶体管的栅极的第一控制信号设置为电源电压vcc,从而导通传输栅晶体管;向连接到存储晶体管的阱电极的第一阱电位施加等于或高于电源电压vcc且等于或低于编程操作时的阱电位的高电压;将存储晶体管的源极充电至电源电压vcc后,存储晶体管的源极电气浮置。

4、在一些实施例中,在构成存储单元的半导体元件的排布中,存储单元在阱区中的排列方法包括:在构成sram存储单元部分的6个半导体元件中,有2个p型沟道晶体管元件被置于第一n型阱区中;分别在第一n型阱区的两侧置第一p型阱区以及第二p型阱区;在第一p型阱区和第二p型阱区中,分别对应设置2个构成sram存储单元部分的6个半导体元件中的n型沟道晶体管元件,在第一p型阱区和第二p型阱区中,分别对应设置1个非易失性存储部分的n型沟道晶体管元件;分别在第一p型阱区以及第二p型阱区的外侧对应设置第二n型阱区和第三n型阱区;在第二n型阱区和第三n型阱区中,分别对应设置1个非易失性存储部分的p型沟道晶体管元件。

5、本技术实施例另一方面还提供了一种可进行sram操作的电擦除非易失性半导体存储装置,包括:存储单元,存储单元包括形成于半导体衬底表面的单层多晶硅栅互补mis晶体管;存储单元包括sram存储单元部分和非易失性存储部分,sram存储单元部分由6个半导体元件组成,非易失性存储部分由6个半导体元件组成;sram存储单元部分包括一个cmos触发器,cmos触发器由n型沟道晶体管和p型沟道晶体管构成;cmos触发器具有互补的正相存储节点和反相存储节点,正相存储节点通过第一n型沟道晶体管与位线连接,反相存储节点通过第二n型沟道晶体管与反相位线连接;cmos触发器连接sram存储单元的电源电压vcc以及接地电压vss;第一n型沟道晶体管的栅极以及第二n型沟道晶体管的栅极连接字线;非易失性存储部分包括两组元件,每组元件包括3个半导体元件,其中,每组元件中的3个半导体元件分别为,由n型沟道晶体管构成的传输栅晶体管、由p型沟道晶体管构成的存储晶体管、由p型沟道晶体管构成的电容器;传输栅晶体管和存储晶体管串联连接;不同传输栅晶体管的漏极分别对应连接sram存储单元部分的正相存储节点和反相存储节点;传输栅晶体管的栅极与第一控制信号相连;传输栅晶体管的源极与存储晶体管的漏极相连;存储晶体管的栅极与电容器的栅极相连,且设置为电气浮置;存储晶体管的源极与第二控制信号相连;存储晶体管的阱电极与第一阱电位相连;电容器的源极、漏极以及阱电极均与第三控制信号相连;其中,存储单元包括12个半导体元件。

6、在一些实施例中,在存储单元的非易失性存储部分对存储晶体管进行擦除操作和编程操作的方法包括:在对存储单元的非易失性存储部分的存储晶体管进行擦除操作期间:将连接到传输栅晶体管的栅极的第一控制信号设置为接地电压vss,从而关闭传输栅晶体管;向连接到存储晶体管的阱电极的第一阱电位施加等于或高于电源电压vcc且等于或高于编程操作时的阱电位的高电压;将连接到非易失性存储部分中的电容器的第三控制信号设置为电源电压vcc;将存储晶体管的源极充电至电源电压vcc后,存储晶体管的源极电气浮置;通过将连接到非易失性存储部分的电容器的第三控制信号从电源电压vcc转换到接地电压vss,执行擦除操作;在存储单元的非易失性存储部分对存储晶体管进行编程操作期间:将连接到传输栅晶体管的栅极的第一控制信号设置为电源电压vcc,从而导通传输栅晶体管;向连接到存储晶体管的阱电极的第一阱电位施加等于或高于电源电压vcc且等于或低于编程操作时的阱电位的高电压;将连接到非易失性存储部分的电容器的第三控制信号设置为接地电压vss;将存储晶体管的源极充电至电源电压vcc后,存储晶体管的源极电气浮置;通过将连接到非易失性存储部分的电容器的第三控制信号从接地电压vss转换到电源电压vcc,执行编程操作。

7、在一些实施例中,在构成存储单元的半导体元件的排布中,存储单元在阱区中的排列方法包括:在构成sram存储单元部分的6个半导体元件中,有2个p型沟道晶体管元件被置于第一n型阱区中;分别在第一n型阱区的两侧设置第一p型阱区以及第二p型阱区;在第一p型阱区和第二p型阱区中,分别对应设置2个构成sram存储单元部分的6个半导体元件中的n型沟道晶体管元件;分别在第一p型阱区以及第二p型阱区的外侧对应设置第二n型阱区和第三n型阱区;在第二n型阱区和第三n型阱区中,分别对应设置1个非易失性存储部分的p型沟道晶体管元件;分别在第二n型阱区和第三n型阱区的外侧对应设置第三p型阱区和第四p型阱区;在第三p型阱区和第四p型阱区中,分别对应设置1个非易失性存储部分的n型沟道晶体管元件;分别在第三p型阱区和第四p型阱区的外侧对应设置第四n型阱区和第五n型阱区;在第四n型阱区和第五n型阱区中,分别对应设置1个非易失性存储部分的由p型沟道晶体管构成的电容器。

8、本技术实施例提供的技术方案至少具有以下优点:

9、在本技术实施例提供的nvsram存储单元中,非易失性存储部分不是由包括两个非易失性存储晶体管元件在内的6个元件组成,而是由包括2个非易失性存储晶体管元件在内的4个元件组成,由两组串联的非易失性存储晶体管和n型沟道晶体管组成。与传统的sram存储单元一样,构成非易失性存储部分的非易失性存储晶体管和n型沟道晶体管在制造时采用了单层多晶硅栅极和互补mis晶体管的栅极电介质结构。此外,非易失性存储部分的非易失性存储晶体管和n型沟道晶体管是以构成逻辑电路的互补mis晶体管的单层多晶硅栅极和栅极电介质结构制造。所以,不需要为现有技术或传统的nvsram存储单元的制造追加sonos、mnos、snos和浮动栅结构的制造工序,能够降低制造成本。另外,本技术实施例的nvsram存储单元中的元件全部由同一制造工序的单层多晶硅栅极的互补mis晶体管构成,因此与需要追加加工工序的现有技术的nvsram存储单元相比,能够实现高集成化。此外,在进行存储操作时,非易失性存储部分的非易失性存储晶体管的擦除操作和编程操作在所有非易失性存储部分同时集体进行,从而可以避免干扰问题。

本文地址:https://www.jishuxx.com/zhuanli/20240731/185063.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表