基于高层次综合的QC-LDPC编码器、通讯设备及存储产品

- 国知局

- 2024-08-02 15:11:38

本技术属于编码器设计相关,更具体地,涉及一种基于高层次综合的qc-ldpc编码器、通讯设备及存储产品。

背景技术:

1、在信息传输与交换期间,通常会产生各种错误,导致原始误码率较高,而准循环低密度奇偶校验码(quasi-cyslic low-density parity-check codes,qc-ldpc)技术可以提高数据的可靠性。在qc-ldpc中,编码过程使用一个生成矩阵(g矩阵)来进行编码,通过使原始数据与生成矩阵相乘,可以生成校验位,得到编码后的数据。同时,还有一个对应的校验矩阵,用来检测错误和进行解码。qc-ldpc由于添加了额外的校验位,使得整个数据具有纠错能力,提高数据传输的准确性和可靠性。

2、高层次综合(high level synthesis,hls)是一个自动化的设计过程,它将逻辑行为的算法描述编译成相应的fpga寄存器传输级别(register transfer level,rtl)的硬件实现。基于hls的自动化硬件开发提供了更高的生产力和灵活性,被广泛用于大规模和/或新的功能场景,如机器学习、图形计算和特定领域加速器。

3、现有的基于hls 的qc-ldpc编码器的编码采用的是移位寄存器的编码结构,这样的设计结构虽然符合直观上的qc-ldpc计算过程,但是基于移位寄存器的编码器需要存储生成矩阵,例如中国专利申请cn117375633a-《一种基于高层次综合的qc-ldpc编码器》中公开了一种qc-ldpc编码器结构设计,一方面,其需要设计移位寄存器来实现生成矩阵的存储、移位和计算,硬件消耗大,另一方面,其每个时刻只能实现一个比特位的计算,计算速率低。

4、基于此,亟需设计一种基于高层次综合的qc-ldpc编码器,以降低硬件消耗并提高编码速率。

技术实现思路

1、针对现有技术的以上缺陷或改进需求,本技术提供了一种基于高层次综合的qc-ldpc编码器、通讯设备及存储产品,其目的在于降低硬件消耗并提高编码速率。

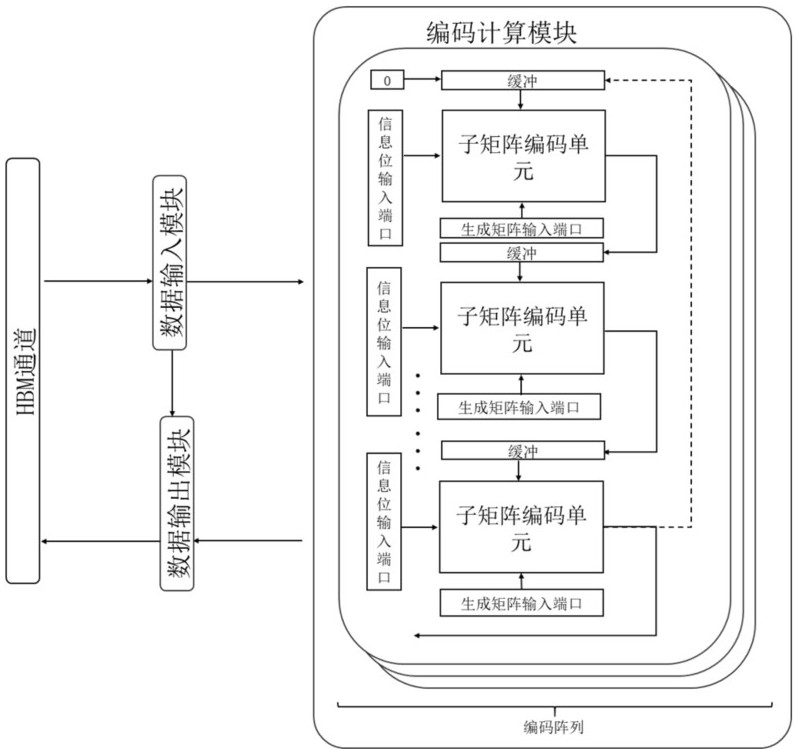

2、为实现上述目的,按照本技术的一个方面,提供了一种基于高层次综合的qc-ldpc编码器,其包括数据输入模块、编码计算模块和数据输出模块;所述数据输入模块用于读入待编码信息,所述编码计算模块用于对所述待编码信息进行编码计算,得到校验信息,所述数据输出模块用于将待编码信息和校验信息整合后输出;

3、所述编码计算模块包括编码阵列,每个所述编码阵列具有h*w个子矩阵编码组件,h、w分别为所述编码阵列的行数与列数,不同列用于对待编码信息中的不同信息区间进行编码计算;

4、每一列中的h个所述子矩阵编码组件结构相同且首尾串联形成环状结构,每个所述子矩阵编码组件包括:

5、信息位输入端口,用于获取对应信息区间中的信息位片段{a1,……,an};

6、生成矩阵输入端口,用于获取qc-ldpc编码器中的生成矩阵片段{b1,……,bn};

7、缓冲,用于获取前一子矩阵编码组件的输出结果{h1,……,hn};

8、子矩阵编码单元,用于各信息位ai和各生成矩阵元素bj进行逻辑与计算,得到n*n维结果矩阵[cij],i为信息位的索引,i =1, ……,n,j为矩阵元素的索引,j =1, ……,n,n为信息位片段的长度,将结果矩阵[cij]中自对角元素位置按照行的方向循环位移k-1位所对应的n个元素与缓冲中的第k元素hk进行异或运算得到第k输出结果并存为下一子矩阵编码组件中的缓冲的第k元素;k为缓冲元素的索引,k=1,……,n;

9、每一列中的h个所述子矩阵编码组件的信息位输入端口用于持续获取对应信息区间的不同信息位片段,将获取对应信息区间最后一组信息位片段的子矩阵编码组件的输出结果作为对应信息区间的校验信息。

10、在其中一个实施例中,所述编码计算模块包括多个所述编码阵列,所述数据输入模块用于读入不同码字的待编码信息,不同码字的待编码信息经过不同的所述编码阵列进行编码计算,所述数据输出模块用于将不同待编码信息和对应校验信息整合后输出不同的编码信息。

11、在其中一个实施例中,所述编码器具有多个数据输入模块、多个编码计算模块和多个数据输出模块,每个编码计算模块对应一个数据输入模块和数据输出模块。

12、在其中一个实施例中,每一列中的子矩阵编码组件的数量h、每个子矩阵编码组件中的信息位输入端口输入的信息位片段的长度n和每个环状结构处理的信息区间的长度l之间满足:l/(h*n)=整数。

13、在其中一个实施例中,编码阵列中各列同步处理相同长度信息区间的编码计算。

14、在其中一个实施例中,所述qc-ldpc编码器还包括初始化模块,用于在启动所述编码计算模块时赋予每个环状结构中的第一个子矩阵编码组件的缓冲数据为0。

15、在其中一个实施例中,所述数据输入模块和所述数据输出模块均通过axi接口与hbm通道通信连接。

16、在其中一个实施例中,所述子矩阵编码单元通过fpga内部的查找表实现:由n2个与门构成的n*n维与门阵列和n个异或门,n*n维与门阵列用于执行n个信息位ai和n个生成矩阵元素bj的逻辑与计算,得到n*n维结果矩阵[cij],n个异或门分别执行n组不同的异或运算得到n个输出结果。

17、按照本技术的另一方面,提供了一种通讯设备,其包括如上任一项所述的基于高层次综合的qc-ldpc编码器。

18、按照本技术的又一方面,提供了 一种存储产品,其包括如上任一项所述的基于高层次综合的qc-ldpc编码器。

19、总体而言,通过本技术所构思的以上技术方案与现有技术相比,本技术具有以下有益效果:

20、1. 本技术提供的一种基于高层次综合的qc-ldpc编码器,设计了编码阵列,每一列由h个子矩阵编码组件首位相接形成环状结构,每个子矩阵编码组件中设计有子矩阵编码单元,每个子矩阵编码单元能够直接实现n个不同的信息位与对应生成矩阵的逻辑运算,并通过首位相接的设计实现前组信息位的运算结果与后一组信息位的运算结果的异或运算,因此不需要设计移位寄存器来实现生成矩阵的存储和移位,减小硬件消耗。而且,本技术中每个子矩阵编码单元能够并行处理多个信息位的逻辑运算且不同子矩阵编码单元能够并行运行,由此可以大大提高编码速率。因此,利用本技术提供的基于高层次综合的qc-ldpc编码器,可以降低硬件消耗并提高编码速率;

21、2. 在一实施例中,每一列中的子矩阵编码组件的数量h、每个子矩阵编码组件中的信息位输入端口输入的信息位片段的长度n和每个环状结构处理的信息区间的长度l之间满足:l/(h*n)=整数。如此,可以使得校验信息固定从最后一个子矩阵编码组件中输出,可以不必定位查询从哪个子矩阵编码组件输出校验信息;

22、3. 在一实施例中,子矩阵编码单元具有多个编码阵列,各编码阵列之间并行运行,如此,可以进一步提高编码速率;

23、4. 在一实施例中,编码器具有多个子矩阵编码单元,各子矩阵编码单元之间并行运行,如此,可以进一步提高编码速率。

本文地址:https://www.jishuxx.com/zhuanli/20240801/245233.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表