用于数据掩码的硬件加速的系统和方法与流程

- 国知局

- 2024-08-02 15:16:34

背景技术:

1、现场可编程门阵列(fpga)是包括逻辑块阵列以及那些逻辑块之间的可重新配置互连的硬件设备。在(或者,以前的)产品中,这些逻辑块可以被称为自适应逻辑模块(alm),而在产品中,这些逻辑块可以被称为可配置逻辑块(clb)。每个逻辑块可以包括可编程逻辑,诸如用于执行从输入到输出的可配置逻辑映射的一个或多个查找表(lut)、用于将输入值相加的加法器、用于临时保存数据的寄存器等。使用配置文件对fpga编程或配置来设置互连(或互连“结构”)以将不同的逻辑块接线在一起,从而将fpga配置为执行由配置文件(有时称为“位文件”)指定的特定功能。

2、与由通用处理器执行的软件实现相比,fpga带来在低级别(例如,在电路级别)实现计算的更高性能和更低功耗的益处。这类似于使用诸如专用协处理器的专用集成电路(asic)的益处,专用协处理器为诸如图形处理单元(gpu)或神经加速器,其分别用以加速特定于计算机图形和人工神经网络的操作。然而,asic的设计和制造是具有高的前期固定成本的漫长而昂贵的过程。

3、因此,fpga的一些应用包括,例如,最终可能在asic中实现的硬件设计的原型,以及在设计和制造asic可能(例如,由于计算的低数量或高度专业化)不合理的情况下的计算的硬件加速。此外,fpga还提供了底层硬件(在“现场”)的重新配置的灵活性,而无需锁定到固定硬件配置中,就像在asic的情况下,其中逻辑直接在制造时间在电路的布局中实现,并且因此具有很少甚至没有的可重新配置性。一些云计算提供商提供对包括连接的fpga的硬件实例(例如,服务器)的访问,从而允许用户定制fpga以执行计算操作的硬件加速。

4、关于这些和其他考虑因素已经给出了示例。另外,虽然已经讨论了相对具体的问题,但是应当理解,示例不应限于解决背景技术中识别的具体问题。

技术实现思路

1、提供本技术实现要素:从而以简化形式介绍一系列概念,这些概念将在下面的详细描述部分中进一步描述。本发明内容不旨在识别所要求保护的主题的关键特征或基本特征,其也不旨在帮助确定所要求保护的主题的范围。

2、本技术的各方面涉及数据掩码的硬件加速,其是机器学习的领域中通常执行的操作。作为一个示例,经常应用于自然语言处理的机器学习模型中的自回归变换器(transformer)模型将掩码应用于输入数据,以便确保变换器模型学习仅基于序列中较早出现的标记并且不基于序列中较晚出现的标记对标记的序列中的给定标记做出预测。对数据应用掩码以通过隐藏(例如清零)在训练过程期间不应考虑的值来强制执行此自回归约束。

3、因此,根据本技术的各个方面的数据掩码的硬件加速改进了包括数据掩码操作的机器学习模型训练过程的性能。性能的改进涉及计算时间(例如,处理器时间)的减少、数据存储和带宽(例如,存储器使用和通过通信总线传送的数据)的减少、能源消耗的减少,并且在一些示例中,减少了在现场可编程门阵列(fpga)上的某些实现中使用的物理硬件量。

4、一个或多个方面的细节在附图和下面的描述中阐述。通过阅读以下详细描述和审查相关联的附图,其他特征和优点将是显而易见的。应理解,以下详细描述仅是解释性的并且不是对所要求保护的本发明的限制。

技术特征:1.一种现场可编程门阵列fpga,包括连接多个逻辑块的可配置互连结构,所述可配置互连结构和所述逻辑块被配置为实现数据掩码电路,所述数据掩码电路被配置为:

2.根据权利要求1所述的fpga,其中所述可配置互连结构和所述逻辑块还被配置为实现掩码生成电路,所述掩码生成电路被配置为基于所述输入数据的对应的索引来生成所述掩码值。

3.根据权利要求2所述的fpga,其中所述可配置互连结构和所述逻辑块还被配置为实现掩码选择多路复用器,所述掩码选择多路复用器被配置为输出所述掩码值以控制所述掩码多路复用器,

4.根据权利要求2所述的fpga,其中所述掩码生成电路被配置为根据三角掩码模式来生成所述掩码值。

5.根据权利要求2所述的fpga,其中所述掩码生成电路被配置为根据被选自以下至少一项的掩码模式来生成所述掩码值:

6.根据权利要求5所述的fpga,其中所述掩码生成电路被配置为接收一个或多个掩码参数,以及

7.根据权利要求1所述的fpga,其中所述数据掩码电路的所述可配置互连结构和所述逻辑块还被配置为将所述所掩码的数据提供给softmax函数,

8.根据权利要求1所述的fpga,其中所述fpga被连接到计算机系统,所述计算机系统被配置为基于多个训练数据来训练机器学习模型,以及

9.一种计算机存储介质,所述计算机存储介质存储配置文件,所述配置文件指定包括可配置互连结构和多个逻辑块的现场可编程门阵列fpga的配置,其中基于所述配置文件被配置的fpga包括被由所述可配置互连结构连接的实现数据掩码电路的逻辑块,所述数据掩码电路被配置为:

10.根据权利要求9所述的计算机存储介质,其中所述配置文件还指定所述fpga的所述可配置互连结构和所述逻辑块的所述配置以实现掩码生成电路,所述掩码生成电路被配置为基于所述输入数据的对应的索引来生成所述掩码值。

11.根据权利要求10所述的计算机存储介质,其中所述配置文件还指定所述fpga的所述可配置互连结构和所述逻辑块的所述配置以实现掩码选择多路复用器,所述掩码选择多路复用器被配置为输出所述掩码值以控制所述掩码多路复用器,

12.根据权利要求10所述的计算机存储介质,其中所述配置文件还指定所述fpga的所述可配置互连结构和所述逻辑块的所述配置以将所述掩码生成电路配置为根据三角掩码模式来生成所述掩码值。

13.根据权利要求10所述的计算机存储介质,其中所述配置文件还指定所述fpga的所述可配置互连结构和所述逻辑块的所述配置以将所述掩码生成电路配置为根据被选自以下至少一项的掩码模式来生成所述掩码值:

14.根据权利要求13所述的计算机存储介质,其中所述配置文件还指定所述fpga的所述可配置互连结构和所述逻辑块的所述配置以将所述掩码生成电路配置为接收一个或多个掩码参数以及使掩码生成电路基于所述一个或多个掩码参数来选择所述掩码模式。

15.根据权利要求9所述的计算机存储介质,其中所述配置文件还指定所述fpga的所述可配置互连结构和所述逻辑块的所述配置以将所述数据掩码电路配置为将所述所掩码的数据提供给softmax函数,

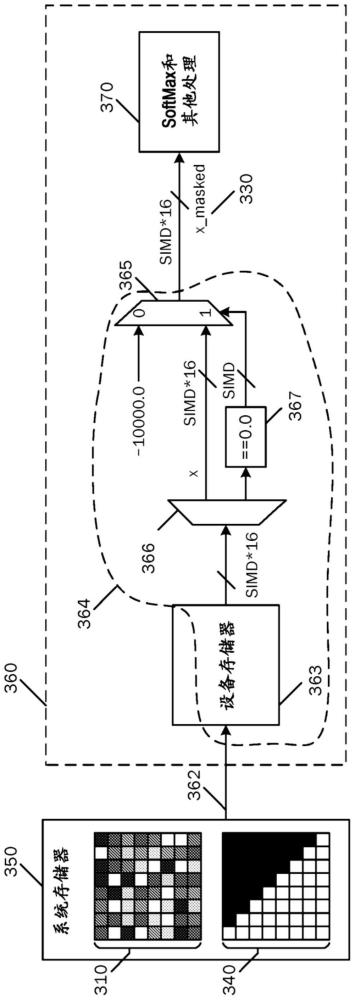

技术总结一种现场可编程门阵列FPGA,包括连接多个逻辑块的可配置互连结构,该可配置互连结构和逻辑块被配置为实现数据掩码电路,该数据掩码电路被配置为:接收输入数据(362),该输入数据包括输入数据在多个索引处的数据值;使用掩码多路复用器(365)在数据值中的数据值和替代值之间进行选择以生成所掩码的数据(330),该掩码多路复用器由在与输入数据的索引相对应的索引处的多个掩码值(SIMD)中的掩码值控制;以及输出所掩码的数据。在一些示例中,该可配置互连结构和逻辑块还被配置为实现被配置为生成掩码值的掩码生成电路。在一些示例中,掩码值是从外部存储器接收的。技术研发人员:奚锦文,刘明罡,E·S·钟受保护的技术使用者:微软技术许可有限责任公司技术研发日:技术公布日:2024/7/15本文地址:https://www.jishuxx.com/zhuanli/20240801/245484.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表