以金属为控制栅极的NorFlash制造方法与流程

- 国知局

- 2024-08-02 15:42:18

本发明涉及半导体,特别是涉及一种以金属为控制栅极的nor flash制造方法。

背景技术:

1、nor型etox闪存存储器(以下简称nor flash)具有高读取速度,高可靠性,以及具备芯片内执行能力,已经成为目前应用最为广泛的非易失性存储器之一。随着制造技术的进步以及市场上对大容量、高密度、低功耗nor flash的需求增加,nor flash已经由大规模量产的65nm/55nm技术节点逐步向40nm技术节点的研发与量产过度。但是在更低节点的norflash开发过程中,闪存单元之间的干扰效应显著增强,工艺窗口明显减小等问题频繁出现。因此标准工艺流程的40nm技术节点的nor flash被业界普遍认为已经接近其物理极限,难以在更低节点上继续开发。

2、为解决上述问题,需要提出一种新型的以金属为控制栅极的nor flash制造方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种以金属为控制栅极的nor flash制造方法,用于解决现有技术中在更低节点的nor flash开发过程中,闪存单元之间的干扰效应显著增强,工艺窗口明显减小等问题频繁出现的问题。

2、为实现上述目的及其他相关目的,本发明提供一种以金属为控制栅极的norflash制造方法,包括:

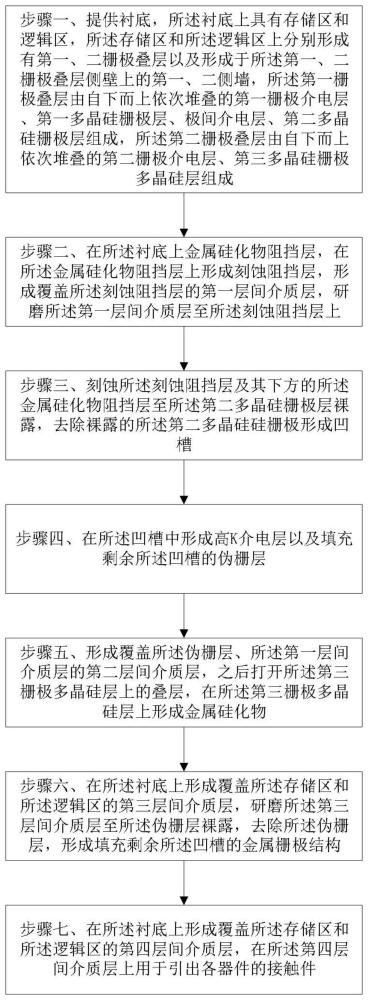

3、步骤一、提供衬底,所述衬底上具有存储区和逻辑区,所述存储区和所述逻辑区上分别形成有第一、二栅极叠层以及形成于所述第一、二栅极叠层侧壁上的第一、二侧墙,所述第一栅极叠层由自下而上依次堆叠的第一栅极介电层、第一多晶硅栅极层、极间介电层、第二多晶硅栅极层组成,所述第二栅极叠层由自下而上依次堆叠的第二栅极介电层、第三多晶硅栅极层组成;

4、步骤二、在所述衬底上金属硅化物阻挡层,在所述金属硅化物阻挡层上形成刻蚀停止层,形成覆盖所述刻蚀停止层的第一层间介质层,研磨所述第一层间介质层至所述刻蚀停止层上;

5、步骤三、刻蚀所述刻蚀停止层及其下方的所述金属硅化物阻挡层至所述第二多晶硅栅极层裸露,去除裸露的所述第二多晶硅硅栅极形成凹槽;

6、步骤四、在所述凹槽中形成高k介电层以及填充剩余所述凹槽的伪栅层;

7、步骤五、形成覆盖所述伪栅层、所述第一层间介质层的第二层间介质层,之后打开所述第三多晶硅栅极层上的叠层,在所述第三多晶硅栅极层上形成金属硅化物;

8、步骤六、在所述衬底上形成覆盖所述存储区和所述逻辑区的第三层间介质层,研磨所述第三层间介质层至所述伪栅层裸露,去除所述伪栅层,形成填充剩余所述凹槽的金属栅极结构;

9、步骤七、在所述衬底上形成覆盖所述存储区和所述逻辑区的第四层间介质层,在所述第四层间介质层上用于引出各器件的接触件。

10、优选地,步骤一中的所述衬底为硅衬底。

11、优选地,步骤一中的所述极间介电层为ono层,其由自下而上依次堆叠的第一氧化层、氮化层、第二氧化层。

12、优选地,步骤二中的所述金属硅化物阻挡层的材料包括富硅氧化物、sio2、sion和si3n4中的至少一种。

13、优选地,步骤二中的所述刻蚀停止层的材料为氮化硅。

14、优选地,步骤三中利用干法回刻蚀的方法刻蚀所述刻蚀停止层及其下方的所述金属硅化物阻挡层。

15、优选地,步骤三中利用湿法刻蚀的方法去除所述第二多晶硅硅栅极。

16、优选地,步骤四中的所述在所述凹槽中形成高k栅极结构以及填充剩余所述凹槽的伪栅层的方法包括:沉积所述高k介电层;研磨所述高k介电层至所述第一层间介质层上;沉积作为所述伪栅层的多晶硅层;研磨所述多晶硅层至所述第一层间介质层上;进行退火工艺。

17、优选地,步骤四中的所述退火工艺的温度范围为500-1500℃,时间范围为0-30min。

18、优选地,步骤五中的所述打开所述第三多晶硅栅极层上的叠层的方法包括:利用光刻定义出所述存储区的刻蚀区域;利用干法刻蚀的方法刻蚀裸露的所述第二层间介质层及其下方的所述第一层间介质层、所述刻蚀停止层、所述金属硅化物阻挡层。

19、优选地,步骤六中利用湿法刻蚀的方法去除所述伪栅层。

20、优选地,步骤七中的所述接触件的形成方法包括:利用光刻刻蚀形成接触孔;在所述接触孔底部形成接触孔金属硅化物;形成填充所述接触孔的金属层。

21、优选地,步骤七在ticl气氛下形成所述接触孔金属硅化物。

22、如上所述,本发明的以金属为控制栅极的nor flash制造方法,具有以下有益效果:

23、本发明可实现具有金属控制栅的存储单元的新型nor flash;工艺流程具有额外流片成本较低,对器件影响程度小,和现有工艺流程兼容性好等优点。

技术特征:1.一种以金属为控制栅极的nor flash制造方法,其特征在于,至少包括:

2.根据权利要求1所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤一中的所述衬底为硅衬底。

3.根据权利要求1所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤一中的所述极间介电层为ono层,其由自下而上依次堆叠的第一氧化层、氮化层、第二氧化层。

4.根据权利要求1所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤二中的所述金属硅化物阻挡层的材料包括富硅氧化物、sio2、sion和si3n4中的至少一种。

5.根据权利要求1所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤二中的所述刻蚀停止层的材料为氮化硅。

6.根据权利要求1所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤三中利用干法回刻蚀的方法刻蚀所述刻蚀停止层及其下方的所述金属硅化物阻挡层。

7.根据权利要求1所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤三中利用湿法刻蚀的方法去除所述第二多晶硅硅栅极。

8.根据权利要求1所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤四中的所述在所述凹槽中形成高k栅极结构以及填充剩余所述凹槽的伪栅层的方法包括:沉积所述高k介电层;研磨所述高k介电层至所述第一层间介质层上;沉积作为所述伪栅层的多晶硅层;研磨所述多晶硅层至所述第一层间介质层上;进行退火工艺。

9.根据权利要求7所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤四中的所述退火工艺的温度范围为500-1500℃,时间范围为0-30min。

10.根据权利要求1所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤五中的所述打开所述第三多晶硅栅极层上的叠层的方法包括:利用光刻定义出所述存储区的刻蚀区域;利用干法刻蚀的方法刻蚀裸露的所述第二层间介质层及其下方的所述第一层间介质层、所述刻蚀停止层、所述金属硅化物阻挡层。

11.根据权利要求1所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤六中利用湿法刻蚀的方法去除所述伪栅层。

12.根据权利要求1所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤七中的所述接触件的形成方法包括:利用光刻刻蚀形成接触孔;在所述接触孔底部形成接触孔金属硅化物;形成填充所述接触孔的金属层。

13.根据权利要求12所述的以金属为控制栅极的nor flash制造方法,其特征在于:步骤七在ticl气氛下形成所述接触孔金属硅化物。

技术总结本发明提供一种以金属为控制栅极的Nor Flash制造方法,提供衬底,衬底上具有存储区和逻辑区,存储区和逻辑区上分别形成有第一、二栅极叠层以及形成于第一、二栅极叠层侧壁上的第一、二侧墙;在衬底上金属硅化物阻挡层,在金属硅化物阻挡层上形成刻蚀停止层,形成覆盖刻蚀停止层的第一层间介质层,研磨第一层间介质层至刻蚀停止层上;刻蚀刻蚀停止层及其下方的金属硅化物阻挡层至第二多晶硅栅极层裸露,去除裸露的第二多晶硅硅栅极形成凹槽;在凹槽中形成高K介电层以及填充剩余凹槽的伪栅层;形成覆盖伪栅层、第一层间介质层的第二层间介质层,之后打开第三多晶硅栅极层上的叠层。本发明可实现具有金属控制栅的存储单元的新型Nor Flash。技术研发人员:王奇伟,舒宇飞,姚邵康受保护的技术使用者:上海华力集成电路制造有限公司技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240801/247358.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表