一种基于温和等离子体技术实现厚层碲化钼固定深度相变的方法

- 国知局

- 2024-08-02 15:42:25

本发明涉及一种基于温和等离子体技术来实现厚层碲化钼固定相变深度的方法,属于半导体器件领域。

背景技术:

1、二碲化钼(mote2)作为过渡金属硫属化合物(tmdcs)的一种,自其被发现以来就引起了大量的关注和广泛的研究。而mote2最令人感兴趣的就是它的相变研究,研究证明了mote2共有半导体相、金属相及从半导体相转变到金属相时的半金属相三种状态。

2、目前报道的很多成果是基于水平结构的1t′-2h-1t′mote2实现的,电极接触区域使用1t′相结构,能够极大地降低接触电阻,从而降低器件功耗。但是影响器件性能的另一重要因素是界面,不同的相变深度会造成不同程度的1t′-2h相的界面错位,从而形成较高的势垒,影响载流子的输运。然而目前尚未有成熟工艺能够精确调控多层tmdcs材料的相变深度。理论计算表明,在单层2h-1t′mote2中,界面处不同的键角会导致器件呈现出肖特基或欧姆两种不同的接触性能。而对于多层样品,随着相变深度的增加,异相界面的能垒会逐渐增大,对接触性能的影响会增大。因此,相变深度的精准调控是平衡1t′-2h-1t′器件接触电阻和异相界面的关键因素。

3、目前报道的改变tmdcs相的手段主要有cvd法、掺杂法、分子插层法、应力法、激光灼烧法和电场诱导法,但是这些方法均难实现多层mote2的固定深度相变。

4、专利文件cn108389779b公开了一种基于温和氢气等离子体的半金属相碲化钼的制备方法,该方法采用使用温和氢气等离子体相变碲化钼的方案,然而其只能实现不同层数的碲化钼完全相变,不能实现厚层碲化钼任意深度的相变。

技术实现思路

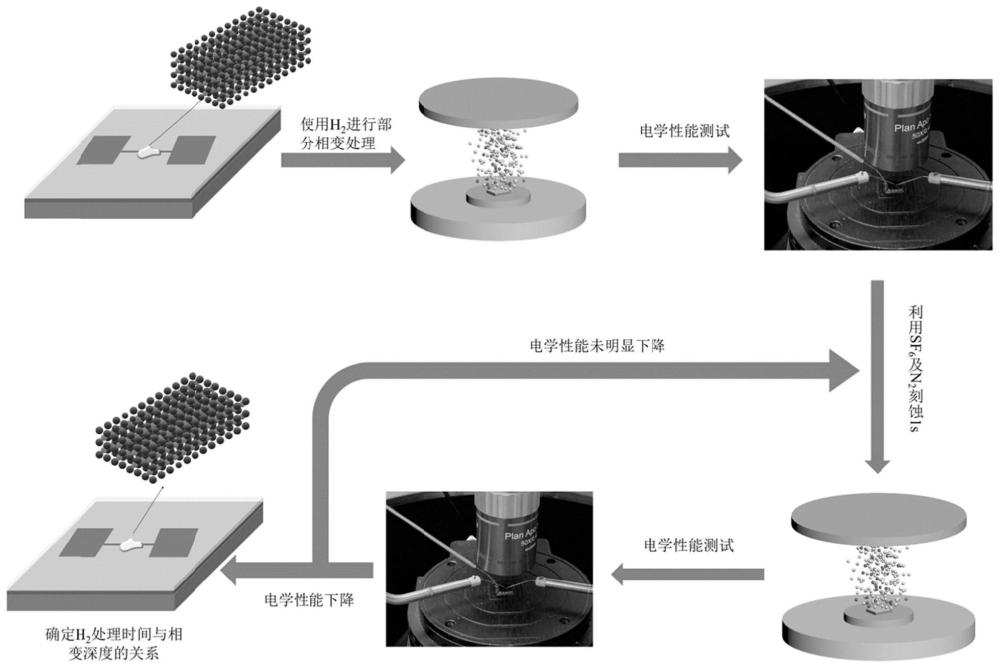

1、为解决以上问题,本发明通过对2h相mote2进行部分相变,使其成为上层为1t′相,下层为2h相的同质异相结构。然后对其进行刻蚀处理,刻蚀掉1t′相mote2,对刻蚀前后的mote2进行afm测试,计算其高度差,也就得到了刻蚀掉1t′相mote2的层数,从而通过刻蚀的方法确定了相变深度。特别之处在于使用了一种底部电极结构,使mote2样品在电极上方,从而避免等离子体处理过程中样品被电极处遮挡部分处理不到,提高结果的准确性,并提供了一种使用了温和等离子体刻蚀的方法来确定相变深度。本方法操作简单,可重复性强,并且实验结果比较准确。

2、本发明的第一个目的是提供一种基于温和等离子体技术实现厚层碲化钼固定深度相变的方法,包括如下步骤:

3、(1)将光刻胶旋涂在衬底表面并进行烘烤,在衬底表面光刻出器件结构图形,得到完成光刻工艺的衬底;

4、(2)将步骤(1)中完成光刻工艺的衬底进行刻蚀处理,得到刻蚀后的衬底;

5、(3)将步骤(2)中刻蚀后的衬底置蒸镀电极,去除光刻胶,得到底部电极结构;

6、(4)将厚层的mote2材料,转移至步骤(3)中的底部电极结构,得到带有mote2底部电极结构;

7、(5)将步骤(4)中得到的带有mote2底部电极结构退火,修复mote2材料缺陷,得到mote2器件;

8、(6)将步骤(5)得到的mote2器件利用h2等离子体对mote2进行相变处理,根据厚层碲化钼相变的深度与相变处理时间的关系确定厚层碲化钼相变的深度,得到上层为1t′相,下层为2h相的同质异相结构的mote2器件。

9、在一种实施方式中,步骤(1)所述的衬底在使用前需要进行清洗,清洗方式为:将衬底放入丙酮中,在20~25khz下超声清洗5分钟,之后将衬底放入乙醇中,在20~25khz下超声清洗5分钟,然后用去离子水冲洗衬底,用氮气枪将衬底吹干后放在加热台上在280~320℃下烘烤10分钟。

10、在一种实施方式中,步骤(1)所述的衬底为带有300nm氧化层的硅基衬底。

11、在一种实施方式中,步骤(1)所述的光刻胶型号为az5214e。

12、在一种实施方式中,步骤(1)所述的光刻采用掩膜光刻机。

13、在一种实施方式中,步骤(1)所述的旋涂为在580~620rpm下旋涂9~10s,在2970~3030rpm下旋涂25~35s。

14、在一种实施方式中,步骤(1)所述的烘烤为在90~100℃下烘烤1~1.5min。

15、在一种实施方式中,步骤(2)所述的刻蚀为:

16、将衬底放入温和等离子体反应腔中,利用sf6及n2混合气体对曝光出的电极结构区域原有的sio2层进行刻蚀处理,所述的sf6的纯度为5n,n2的纯度为5n,sf6和n2气体的流量比为13~17:6~8sccm;刻蚀的参数为:在250~350w射频功率,反射功率控制在60w以内,等离子体反应腔体压强保持在9~11pa的条件下,反应时间60~90s;

17、在一种实施方式中,步骤(3)所述的蒸镀电极包括2.5nm的镍电极及30nm的金电极,蒸镀机保持在真空条件5×10-3pa以下,启动电子束蒸镀设备,蒸镀速率为0.20~0.3a/s,时间约为2min;蒸镀机保持在真空条件5×10-4pa以下,启动金属热蒸发设备,蒸镀速率为0.20~0.3a/s,时间约15~25min,得到电极总厚度为32.5nm;

18、在一种实施方式中,步骤(4)所述的转移是利用机械剥离技术得到厚层的mote2材料,并利用pdms干法转移技术将其转移至步骤(4)中蒸镀好的底部电极结构上。

19、在一种实施方式中,步骤(4)所述的干法转移技术具体操作为:利用双面胶将底部电极衬底固定在光镜平台上,移动平台,将电极结构置于视野中央;将带有mote2材料的pdms置于转移平台上,在光镜下将pdms上的mote2材料与底部电极沟道处相贴合,移走pdms,mote2材料保留在电极上,此时得到了mote2底部电极结构。

20、在一种实施方式中,步骤(5)所述的退火工艺具体的参数为:20~40min内将退火炉升温至140~160℃,然后保持2小时,期间保持退火炉处于真空状态;冷却后取出衬底。

21、在一种实施方式中,步骤(6)所述的h2的纯度为5n,气体流量为18~22sccm。

22、在一种实施方式中,步骤(6)所述的等离子体具体参数设置为:在50~80w射频功率,反射功率控制在2w以内,等离子体反应腔内压强为5~8pa的条件下,处理0.5~20min。

23、在一种实施方式中,h2反应时间与相变深度的关系式为y=0.37×x0.58,x代表处理时间,单位为秒,y代表刻蚀深度,单位为纳米。

24、一种基于温和等离子体刻蚀技术来确定厚层碲化钼相变处理深度的方法,包括如下步骤:

25、(1)采用上述的基于温和等离子体技术实现厚层碲化钼固定深度相变的方法对厚层碲化钼进行相变处理,其中,底部电极结构制作完成后对其进行拉曼表征;

26、(2)测试反应后的同质异相结构的mote2器件的电学性能并对其进行拉曼表征,然后对其进行afm测试,得到同质异相结构mote2器件的总高度;

27、(3)将经过afm测试的mote2器件放入等离子反应腔中,对mote2器件进行刻蚀处理,测试刻蚀后的mote2器件的电学性能并进行拉曼表征;

28、(4)重复步骤(3),直到电学数据及拉曼表征出mote2器件为本征态,进行afm测试,计算mote2器件刻蚀前后的高度差,得到mote2的相变深度。

29、在一种实施方式中,步骤(3)所述的对mote2器件进行刻蚀处理的具体参数为:在18~22w射频功率,反射功率控制在0.8~1.2w左右,等离子体反应腔体压强保持在8~12pa的条件下。

30、在一种实施方式中,步骤(4)所述的计算mote2刻蚀前后的高度差为:对步骤(3)中得到的2h相的mote2器件进行afm测试后,得到剩余的mote2器件的高度,将此高度与步骤(2)所述的得到的afm结果进行对比,得到被刻蚀掉的1t′相mote2器件的高度,从而计算出mote2器件相变的层数,也即通过温和等离子体刻蚀技术确定了厚层碲化钼的相变深度。

31、本发明有益效果是:

32、(1)本发明提供了一种制作底部电极的方法,不同于现有技术将mote2直接转移到衬底上,本发明先在衬底表面光刻出器件结构图形,刻蚀,得到底部电极结构,再使用干法转移技术将mote2转移到底部上;本发明制备的底部电极结构避免了等离子体处理过程中样品被电极处遮挡而导致等离子处理不均匀的情况,相变结果也会更加明显,能够更加准确得得出mote2相变深度与时间的关系。

33、(2)本发明通过对经过相变处理的mote2进行刻蚀,然后对刻蚀前后的mote2进行afm测试,能够计算出mote2任意相变的深度,解决了现有技术在mote2进行部分相变时无法得知mote2的相变深度的难题。

34、(3)本发明通过对经过温和等离子体技术进行相变的厚层碲化钼的相变深度和相变时间的研究,得到了温和等离子体技术相变处理时厚层碲化钼的相变深度和相变时间的关系,通过这个关系可以实现厚层碲化钼固定深度的相变。

本文地址:https://www.jishuxx.com/zhuanli/20240801/247371.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表