一种面向脉动阵列的稀疏矩阵编码方法及装置

- 国知局

- 2024-08-02 15:43:00

本发明涉及矩阵计算的硬件加速,具体涉及一种面向脉动阵列的稀疏矩阵编码方法及装置。

背景技术:

1、在存储和计算效率方面,目前缺乏与脉动阵列深度兼容的稀疏矩阵表示格式。一般存储矩阵的方法是使用二维数组,其优点是每个元素都可以随机访问,因此便于实现对矩阵的各种操作。对于稀疏矩阵,它通常具有很大的维数,有时大到整个矩阵(零元素)占用了大部分内存。二维数组的存储方法不仅浪费了大量的存储单元来存储零元素,而且在操作中浪费了大量的时间来进行零元素的无效操作。因此,有必要考虑稀疏矩阵的压缩存储(只存储非零元素)。目前,稀疏矩阵的存储格式有coo、csr/csc、ell、rlc、dia等。这些格式以不同的方式提取稀疏矩阵的非零元素,适用于不同的场景。虽然稀疏矩阵可以在存储中有效地表示,但它们在脉动阵列中可能不能有效地执行。虽然csr格式在高稀疏性下减少了存储和带宽消耗,但它不能直接用于计算。它不仅需要解码,还需要重新组织数据(旋转和倾斜)以匹配脉动数据流。此外,在计算过程中还存在计算效率不高的问题:无法避免重组数据后新出现的整列的零值乘法。根据观察,在高稀疏性的情况下,零列乘法的出现可能超过总计算的50%。因此,如何设计新的稀疏数据表示格式,并结合脉动阵列的特点进行优化以提高稀疏数据的执行效率,已成为一项亟待解决的关键技术问题。

技术实现思路

1、本发明要解决的技术问题:针对现有技术的上述问题,提供一种面向脉动阵列的稀疏矩阵编码方法及装置,本发明旨在实现一种新稀疏矩阵编码方法,使其紧密贴合脉动阵列的运行时数据流,以结合脉动阵列的特点进行优化以提高稀疏数据的执行效率。

2、为了解决上述技术问题,本发明采用的技术方案为:

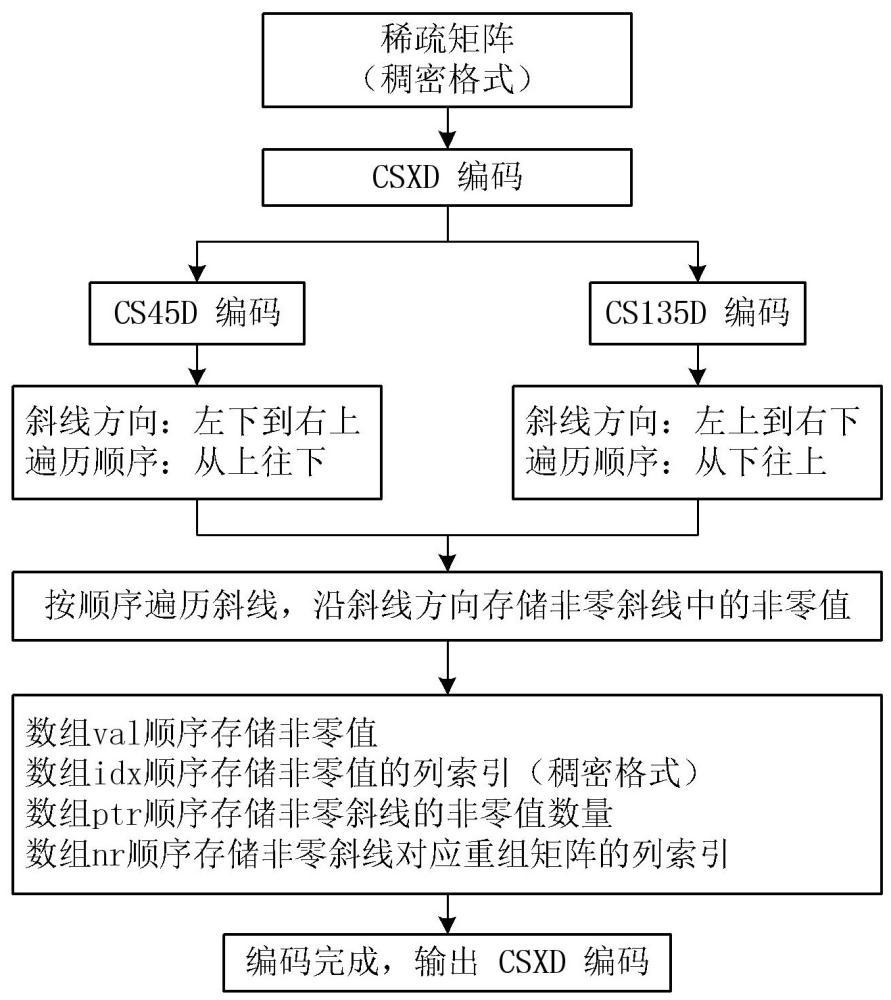

3、一种面向脉动阵列的稀疏矩阵编码方法,包括:

4、s101,按照指定的方向遍历稀疏矩阵的斜线,沿斜线方向存储非零斜线中的非零值;

5、s102,将存储的非零值使用数组val、数组idx、数组nr和数组ptr进行编码,其中数组val用于顺序存储非零值,数组idx用于顺序存储非零值在稀疏矩阵中的列索引,数组ptr用于顺序存储非零斜线的非零值数量,数组nr用于顺序存储非零斜线对应重组矩阵的列索引。

6、可选地,所述数组ptr的长度为非零斜线的数量加1,且数组ptr中的第一个值为0,任意第i+1个值ptr[i+1]减去第i个值ptr[i]得到的结果为第i个非零斜线中的非零值的数量。

7、可选地,所述将存储的非零值使用数组val、数组idx、数组nr和数组ptr进行编码时,还包括在需要将输入的稀疏矩阵进行切片时,采用一个额外的数组tile来记录每个切片tile中非零斜线的数量,且将数组nr中任意第i个值nr[i]减去第i个值nr[i-1]得到的结果配置为存储第i个切片tile中非零斜线的数量,且所述数组nr中任意第i个值nr[i]减去第i个值nr[i-1]得到的结果小于预设的流速阈值maxflow。

8、可选地,步骤s101中指定的方向是指从上往下或者从下往上。

9、可选地,步骤s101中的斜线方向是指从左下到右上或左上到右下。

10、可选地,步骤s101之前还包括通过解析稀疏矩阵的计算指令或者读取预设的寄存器来获取指定的方向、斜线方向两者中至少一种的配置值。

11、此外,本发明还提供一种稀疏矩阵计算装置,包括:

12、预处理模块,用于从片外存储中获取稀疏矩阵,并采用所述的面向脉动阵列的稀疏矩阵编码方法将输入的稀疏矩阵进行编码并输出到片上单元;

13、片上单元,用于对编码得到的编码结果解码为符合脉动阵列规模的数据并基于脉动阵列进行矩阵计算;

14、后处理模块,用于将矩阵计算结果转换为稠密格式的稀疏矩阵输出到片外存储中。

15、可选地,所述片上单元包括:

16、片上缓冲,用于为预处理模块、后处理模块和片上单元之间的数据交互提供缓冲;

17、解码器,用于将编码结果解码生成符合脉动阵列规模的数据;

18、脉动阵列单元,用于针对得到的符合脉动阵列规模的数据进行矩阵计算,包括用于控制数据加载、存储和路由的阵列控制模块和脉动阵列,所述脉动阵列由多个处理单元pe通过垂直和水平方向互连构成。

19、可选地,所述解码器为由寄存器、多路复用器和移位器组成,所述寄存器用于存储输入的数组val、数组idx、数组nr和数组ptr,数组val、数组idx中的值按照相同的位置划分为多组(idx,val),所述多路复用器的数量为非零值的数量,多路复用器的控制端受数组ptr的对应位置的值控制,多路复用器的一路输入为对应的一组(idx,val)、另一路输入为0,每一个多路复用器的输出端连接有一个移位器;所述解码器与脉动阵列单元构成四阶段的流水线,第一阶段为解码器通过寄存器分别读取所述编码结果中的数组nr和数组ptr,第二阶段为解码器通过寄存器分别读取所述编码结果中的数组val和数组idx;第三阶段为解码器通过多路复用器根据数组ptr决定每个组(idx,val)是否有效,移位器根据数组idx的值对有效的数组val的值进行移位并存储生成符合脉动阵列规模的数据;第四阶段为脉动阵列单元针对生成符合脉动阵列规模的数据进行矩阵计算。

20、可选地,所述脉动阵列单元中多个处理单元pe共享阵列控制模块中的片上全局缓冲区,所述脉动阵列单元中包含有某一列脉动阵列构成的快速通道,所述快速通道中的每一个处理单元pe均连接有一个多路复用器,且该处理单元pe的输入端通过对应的多路复用器与片上全局缓冲区中的输入缓冲相连以用于获取相邻的处理单元pe以及非相邻的处理单元pe的输出作为该处理单元pe的输入,且解码结果中的数组nr的值作为多路复用器的控制信号,以使得多路复用器根据所需的流速选择相应处理单元pe的输出作为该处理单元pe的输入。

21、和现有技术相比,本发明主要具有下述优点:本发明方法包括按照指定的方向遍历稀疏矩阵的斜线,沿斜线方向存储非零斜线中的非零值并使用数组val、数组idx、数组nr和数组ptr进行编码,数组val用于顺序存储非零值,数组idx用于顺序存储非零值在稀疏矩阵中的列索引,数组ptr用于顺序存储非零斜线的非零值数量,数组nr用于顺序存储非零斜线对应重组矩阵的列索引,通过上述稀疏矩阵编码方法,能够紧密贴合脉动阵列的运行时数据流,从而能够结合脉动阵列的特点进行优化以提高脉动阵列上稀疏矩阵的存储和计算效率。

技术特征:1.一种面向脉动阵列的稀疏矩阵编码方法,其特征在于,包括:

2.根据权利要求1所述的面向脉动阵列的稀疏矩阵编码方法,其特征在于,所述数组ptr的长度为非零斜线的数量加1,且数组ptr中的第一个值为0,任意第i+1个值ptr[i+1]减去第i个值ptr[i]得到的结果为第i个非零斜线中的非零值的数量。

3.根据权利要求2所述的面向脉动阵列的稀疏矩阵编码方法,其特征在于,所述将存储的非零值使用数组val、数组idx、数组nr和数组ptr进行编码时,还包括在需要将输入的稀疏矩阵进行切片时,采用一个额外的数组tile来记录每个切片tile中非零斜线的数量,且将数组nr中任意第i个值nr[i]减去第i个值nr[i-1]得到的结果配置为存储第i个切片tile中非零斜线的数量,且所述数组nr中任意第i个值nr[i]减去第i个值nr[i-1]得到的结果小于预设的流速阈值maxflow。

4.根据权利要求1所述的面向脉动阵列的稀疏矩阵编码方法,其特征在于,步骤s101中指定的方向是指从上往下或者从下往上。

5.根据权利要求1所述的面向脉动阵列的稀疏矩阵编码方法,其特征在于,步骤s101中的斜线方向是指从左下到右上或左上到右下。

6.根据权利要求1所述的面向脉动阵列的稀疏矩阵编码方法,其特征在于,步骤s101之前还包括通过解析稀疏矩阵的计算指令或者读取预设的寄存器来获取指定的方向、斜线方向两者中至少一种的配置值。

7.一种稀疏矩阵计算装置,其特征在于,包括:

8.根据权利要求7所述的稀疏矩阵计算装置,其特征在于,所述片上单元包括:

9.根据权利要求8所述的稀疏矩阵计算装置,其特征在于,所述解码器为由寄存器、多路复用器和移位器组成,所述寄存器用于存储输入的数组val、数组idx、数组nr和数组ptr,数组val、数组idx中的值按照相同的位置划分为多组(idx,val),所述多路复用器的数量为非零值的数量,多路复用器的控制端受数组ptr的对应位置的值控制,多路复用器的一路输入为对应的一组(idx,val)、另一路输入为0,每一个多路复用器的输出端连接有一个移位器;所述解码器与脉动阵列单元构成四阶段的流水线,第一阶段为解码器通过寄存器分别读取所述编码结果中的数组nr和数组ptr,第二阶段为解码器通过寄存器分别读取所述编码结果中的数组val和数组idx;第三阶段为解码器通过多路复用器根据数组ptr决定每个组(idx,val)是否有效,移位器根据数组idx的值对有效的数组val的值进行移位并存储生成符合脉动阵列规模的数据;第四阶段为脉动阵列单元针对生成符合脉动阵列规模的数据进行矩阵计算。

10.根据权利要求9所述的稀疏矩阵计算装置,其特征在于,所述脉动阵列单元中多个处理单元pe共享阵列控制模块中的片上全局缓冲区,所述脉动阵列单元中包含有某一列脉动阵列构成的快速通道,所述快速通道中的每一个处理单元pe均连接有一个多路复用器,且该处理单元pe的输入端通过对应的多路复用器与片上全局缓冲区中的输入缓冲相连以用于获取相邻的处理单元pe以及非相邻的处理单元pe的输出作为该处理单元pe的输入,且解码结果中的数组nr的值作为多路复用器的控制信号,以使得多路复用器根据所需的流速选择相应处理单元pe的输出作为该处理单元pe的输入。

技术总结本发明公开了一种面向脉动阵列的稀疏矩阵编码方法及装置,本发明方法包括按照指定的方向遍历稀疏矩阵的斜线,沿斜线方向存储非零斜线中的非零值并使用数组val、数组idx、数组nr和数组ptr进行编码,数组val用于顺序存储非零值,数组idx用于顺序存储非零值在稀疏矩阵中的列索引,数组ptr用于顺序存储非零斜线的非零值数量,数组nr用于顺序存储非零斜线对应重组矩阵的列索引;本发明装置包括预处理模块、片上单元和后处理模块,预处理模块用于采用本发明方法对稀疏矩阵编码。本发明旨在实现一种新稀疏矩阵编码方法,使其紧密贴合脉动阵列的运行时数据流,以结合脉动阵列的特点进行优化以提高稀疏数据的执行效率。技术研发人员:文梅,汤珉琎,彭奔康,李重行,杨靖奎,沈俊忠受保护的技术使用者:中国人民解放军国防科技大学技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240801/247446.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表