一种3T结构电荷俘获型闪存存储器及其制造方法

- 国知局

- 2024-08-22 14:20:27

本发明属于高端储存器,具体涉及一种3t结构电荷俘获型闪存存储器及其制造方法。

背景技术:

1、过去数十年间,随着消费电子产品如手机、笔记本电脑、平板电脑和电子游戏等的普及,人们对非易失性存储器(nvm)的需求日益攀升。同时,nvm现在被广泛应用于工业和汽车环境中,这对nvm在各种极端温度环境下的数据保持能力和可靠性提出了更高的要求。在各种非易失性存储器中,闪存存储器由于具有存储密度高、容量大、成本低、存取速度快等优点,已经成为驱动整个半导体存储器产业的主要动力。

2、闪存存储器按照存储单元的结构来划分,主要有浮栅型(floating gate,fg)闪存存储器和电荷俘获型(charge-trap,ct)闪存存储器两种。浮栅型存储器是现代半导体存储器的基础,包括两个氧化物绝缘层,中间夹一层浮栅层。中间的浮栅层(floating gate)作为存储层,一般使用多晶硅。通过栅源偏置电压,浮栅型存储器向浮栅中注入或者从浮栅中拉出电荷,控制器件阈值电压的改变,从而达到存储信息0和1的目的。传统的浮栅型存储器面临多重挑战:多晶硅层的厚度不易减薄,无法随器件的宽度和沟道长度等比例缩小,器件呈“瘦高形”,相邻器件间的串扰现象严重;器件隧穿氧化层的厚度降低到2~3nm时,漏电增加;隧穿氧化层中单一的漏电路径也会使整个浮栅中存储的所有电荷泄露,导致存储的数据丢失。为了克服浮栅型存储器的各种问题,电荷俘获性存储器,也称sonos型存储器应运而,其结构为硅-氧化物隧穿层-氮化物存储层-氧化物阻挡层-多晶硅(silicon/oxide/nitride/oxide/poly-silicon,sonos)。其结构与浮栅型存储器类似,但最大的不同是存储层为不导电的si3n4。si3n4介质层呈非晶态,能产生许多独立的陷阱,电荷被俘获在其中不会产生横向流动,即使局部出现了泄露,也不会导致整个存储层的电荷流失,保持特性得到了大大提高。另外,氮化硅层的厚度可以做到10nm以下,这也有效的减弱了浮栅型器件“瘦高”形貌带来的单元之间耦合电容增加、干扰增强的问题,更有利于器件尺寸的进一步缩小。

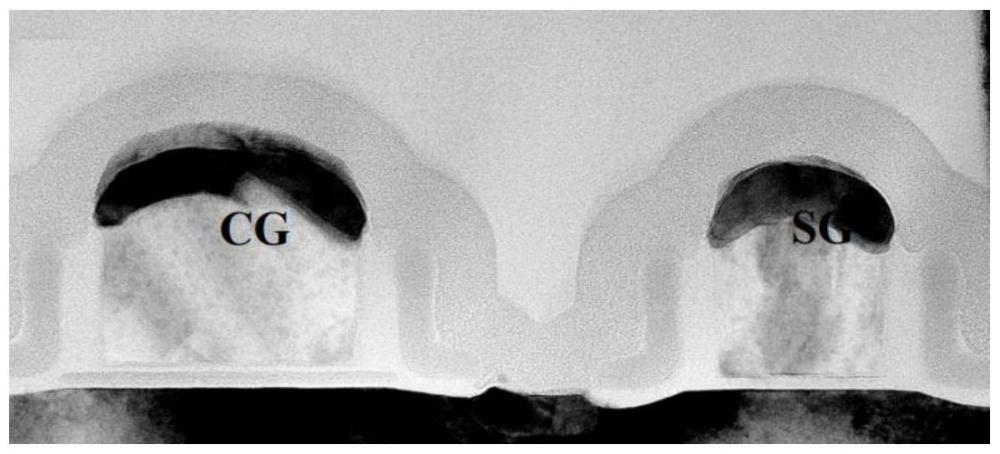

3、现有的浮栅型闪存存储器和sonos型闪存存储器依旧存在工艺尺寸无法缩小、单元面积大、写入功耗大及阵列面积开销大的问题,无法实现gb容量以上的高密度集成。如图1是传统2t结构电荷俘获型闪存存储单元结构剖面图,存在单元面积大、擦写效率低的问题;图2是1.5t分裂栅结构电荷俘获型闪存存储单元结构剖面图,相较2t结构能有效降低单元面积,但是选择栅(sg)和存储栅(cg)之间间距太近,对中间的sio2隔离层厚度要求高,且顶部金属硅化物(salicide)短路风险大。

技术实现思路

1、本发明的目的是为了解决现有技术中存在的问题,提供一种非易失性的新型3t结构电荷俘获型闪存存储器及其制造方法,可以实现高密度、低短路风险的代码存储。

2、第一方面,本发明提供新型3t结构电荷俘获型闪存存储器,该存储器的存储单元类似于两个1.5t分裂栅共享选通栅电极,并关于中间的选通栅电极镜像对称组合;具体包括

3、衬底(1);

4、源极区(2)、漏极区(3),其分别内嵌在所述衬底(1)的两侧内,并顶部暴露;

5、一个选通栅(4)sg,其布设在所述衬底(1)上方;

6、两个存储栅(5)cg,其均布设在衬底(1)上方,且分别位于在所述选通栅(4)sg的两侧;

7、两个侧墙(6),其分别布设在两个存储栅(5)cg的外侧;

8、两个第一阻挡氧化层(7),其分别布设在所述两个侧墙(6)各自与所述存储栅(5)cg间位置;

9、其中,每个存储栅(5)cg与所述选通栅(4)sg间设有一个隔离介质层(8),所述隔离介质层(8)为两层结构,分别是氮化硅层(81)和氧化硅层(82),所述氮化硅层(81)靠近所述选通栅(4)sg,所述氧化硅层(82)靠近所述存储栅(5)cg;

10、每个存储栅(5)cg的顶部均布设有隔离氧化物层(9)、第一金属硅化物层(10),所述隔离氧化物层(9)靠近选通栅(4)sg。

11、其中一种实施方式,所述选通栅(4)sg与衬底(1)间设有栅氧化层(11)。

12、其中一种实施方式,所述存储栅(5)cg与衬底(1)间设有存储介质层(12),所述存储介质层(12)自存储栅(5)cg向衬底(1)方向依次包括第二阻挡氧化层(121)、电荷俘获层(122)、隧穿氧化层(123)。

13、其中一种实施方式,所述侧墙(6)与衬底(1)间设有衬底氧化层(14)。

14、其中一种实施方式,所述源极区(2)的暴露区域、漏极区(3)的暴露区域、选通栅(4)sg的顶部均布设第二金属硅化物层(13)。

15、其中一种实施方式,所述隔离氧化物层(9)的顶部与所述选通栅(4)sg的顶部持平。

16、其中一种实施方式,所述隔离介质层(8)的顶部与所述选通栅(4)sg的顶部持平。

17、其中一种实施方式,所述隔离氧化物层(9)的厚度大于第一金属硅化物层(10)的厚度。

18、其中一种实施方式,所述氮化硅层(81)的厚度介于60-80埃,氧化硅层(82)的厚度介于80-100埃。

19、其中一种实施方式,所述隧穿氧化层(123)的厚度介于30-40埃,电荷俘获层(122)的厚度介于90-110埃,第二阻挡氧化层(121)的厚度介于50-60埃。

20、其中一种实施方式,所述存储栅(5)的高度介于620-680埃,宽度介于550-650埃;选通栅(4)的高度介于1000-1100埃,宽度介于1150-1250埃。

21、其中一种实施方式,隔离氧化物层(9)的高度介于400-500埃。

22、第二方面,本发明提供了一种新型3t结构电荷俘获型闪存存储器的制造方法,包括下列步骤:

23、步骤一:在衬底上先后生成ono层、poly1层和隔离介质层(8),其中ono层为三层结构,从下到上依次为隧穿氧化层(123)、电荷俘获层(122)、第二阻挡氧化层(121);

24、步骤二:刻蚀多余的ono层、poly1层和隔离介质层(8),制备得到两个存储栅(5),两个存储栅(5)间位置刻蚀停止在隧穿氧化层(123);

25、步骤三:先后淀积氧化硅层(82)、氮化硅层(81)构成隔离氧化物层(9),并通过刻蚀处理使得隔离介质层(8)仅保留在存储栅(5)的左右两侧壁;

26、步骤四:通过氧化处理在存储栅(5)间生成氧化硅层,作为选通栅的栅氧层(11);

27、步骤五:淀积poly2层,并进行刻蚀处理,刻蚀停止在poly2层和隔离氧化物层(9)等高;

28、步骤六:通过刻蚀处理使得poly2层仅保留位于存储栅(5)间的选通栅(4)部分,并将隔离氧化物层(9)刻蚀一部分,露出部分poly1,在源极区(2)、漏极区(3)完成ldd(lightly doped drain,轻掺杂漏电极区)注入;

29、步骤七:淀积氮化硅并通过刻蚀处理生成侧墙(6),在源极区(2)、漏极区(3)完成离子注入;

30、步骤八:在存储栅(5)露出poly1部分生成第一金属硅化物层(10),选通栅(4)、源极区(2)、漏极区(3)上生成第二金属硅化物层(13),完成后续互联工艺。

31、相较于1.5t分裂栅结构,本发明提出的存储器拥有如下优点:

32、1)通过共享选通栅电极在一个闪存存储器单元中实现两个存储晶体管,大大降低每个存储位的等效面积,获得更低的成本和更高的集成密度;

33、2)设计了两层结构的隔离介质层,分别是第一层隔离介质层和第二层隔离介质层。第一层隔离介质层为氮化硅层,主要起到保护第二层隔离介质层的作用;第二层隔离介质层为氧化硅层,主要起电学隔离的作用。隔离介质层的厚度会对器件性能起到很大的影响,厚度过厚会影响降低选通栅电极的栅控能力,使得下方沟道不完全开启,影响器件的导通效果;厚度过薄则会在选通栅电极和存储栅间产生较大漏电风险。因此隔离介质层的厚度必须适中、可控且不会在制造过程中被影响。在实际制造过程中,如果仅有第二层隔离介质层,那么该介质层会在hf酸洗和高温氧化中被破坏,厚度不可控,器件短路风险增大。本发明中,将第一层隔离介质层和第二层隔离介质层组合使用,第二层隔离介质层为氮化硅材料,在hf酸洗过程中反应速率很慢,能有效保护第一层隔离介质层不被腐蚀;高温氧化过程中,氮化硅可以起到隔绝氧气的作用,保护第一层隔离介质层不被氧化,保证隔离介质层的厚度基本不变。

34、3)在存储栅上增加隔离氧化物层,将存储栅和选通栅上的金属硅化物层分隔开来,解决了传统1.5t分裂栅结构器件栅与栅之间的短路问题,增加了器件的可靠性。

本文地址:https://www.jishuxx.com/zhuanli/20240822/278206.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。