筛选栅介质层可靠性的良率测试方法与流程

- 国知局

- 2024-09-05 14:51:30

本发明涉及半导体,特别是涉及一种筛选栅介质层可靠性的良率测试方法。

背景技术:

1、对于双栅工艺的制造,先要完成高压氧化膜的生长,然后利用光刻胶对高压区进行保护,用湿法刻蚀完成低压区氧化膜的去除,此时由于光刻胶收缩或者劣化,极易发生翘曲,导致高压器件栅氧的侧边被酸液侧掏,栅氧变薄,影响到器件性能或者可靠性;

2、高压电容为pump电路中的核心器件之一,当其栅介质层例如栅氧被侧掏变薄后,其tddb(经时绝缘击穿,time dependent dielectric breakdown)性能及能承受的最大电压下降,栅氧厚度变薄到一定程度后在高压下极易发生击穿。

3、但栅介质层侧掏变薄的风险die经正常良率测试无法完全筛除。

4、为解决上述问题,需要提出一种新型的筛选栅介质层可靠性的良率测试方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种筛选栅介质层可靠性的良率测试方法,用于解决现有技术中但栅介质层侧掏变薄的风险die经正常良率测试无法完全筛除的问题。

2、为实现上述目的及其他相关目的,本发明提供一种筛选栅介质层可靠性的良率测试方法,包括:

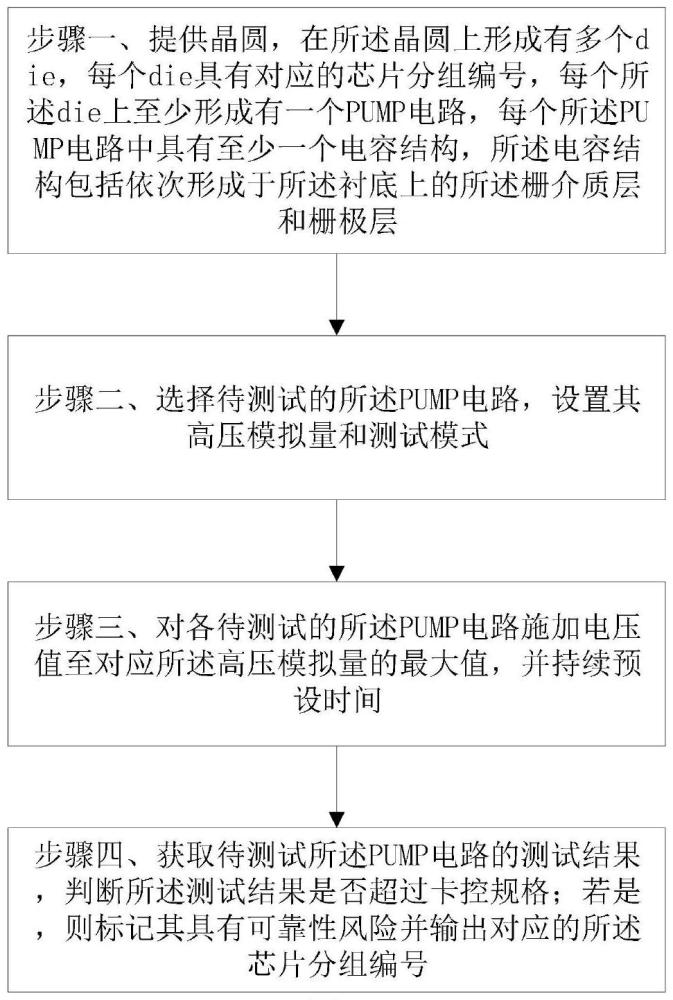

3、步骤一、提供晶圆,在所述晶圆上形成有多个die,每个die具有对应的芯片分组编号,每个所述die上至少形成有一个pump电路,每个所述pump电路中具有至少一个电容结构,所述电容结构包括依次形成于所述衬底上的所述栅介质层和栅极层;

4、步骤二、选择待测试的所述pump电路,设置其高压模拟量和测试模式;

5、步骤三、对各待测试的所述pump电路施加电压值至对应所述高压模拟量的最大值,并持续预设时间;

6、步骤四、获取待测试所述pump电路的测试结果,判断所述测试结果是否超过卡控规格;若是,则标记其具有可靠性风险并输出对应的所述芯片分组编号。

7、优选地,步骤一中的所述die的制造工艺包括双栅工艺。

8、优选地,步骤一中的所述栅介质层的形成方法包括:在所述晶圆上形成目标器件区的栅介质层;在所述栅介质层上形成光刻胶层;光刻打开所述光刻胶层以定义出所述栅介质层的去除区域;刻蚀去除裸露的所述栅介质层。

9、优选地,步骤一中的所述晶圆上包括高压器件区和低压器件区,所述目标器件区为高压器件区。

10、优选地,步骤一中的所述刻蚀的方法为湿法刻蚀。

11、优选地,步骤一中的所述栅介质层的材料为二氧化硅。

12、优选地,步骤一中的所述栅极层的材料多晶硅。

13、优选地,步骤二中的所述高压模拟量包括字线电压和位线电压。

14、优选地,步骤二中的所述高压模拟量为5.5~8v。

15、优选地,步骤三中的所述预设时间为5至10s。

16、优选地,步骤四中根据所述高压模拟量是否发生漂移或所述die功能是否异常来判断所述测试结果是否超过卡控规格。

17、优选地,所述方法还包括步骤五、对所有的所述die进行功能测试,判断其功能是否异常,若是,则标记功能异常的所述die具有可靠性风险并输出对应的所述芯片分组编号。

18、如上所述,本发明的筛选栅介质层可靠性的良率测试方法,具有以下有益效果:

19、本发明能够筛选出栅介质层侧掏变薄导致的风险die,解决了经正常cp测试无法完全筛除风险die的问题。

技术特征:1.一种筛选栅介质层可靠性的良率测试方法,其特征在于,至少包括:

2.根据权利要求1所述的筛选栅介质层可靠性的良率测试方法,其特征在于:步骤一中的所述die的制造工艺包括双栅工艺。

3.根据权利要求1或2所述的筛选栅介质层可靠性的良率测试方法,其特征在于:步骤一中的所述栅介质层的形成方法包括:在所述晶圆上形成目标器件区的栅介质层;在所述栅介质层上形成光刻胶层;光刻打开所述光刻胶层以定义出所述栅介质层的去除区域;刻蚀去除裸露的所述栅介质层。

4.根据权利要求3所述的筛选栅介质层可靠性的良率测试方法,其特征在于:步骤一中的所述晶圆上包括高压器件区和低压器件区,所述目标器件区为高压器件区。

5.根据权利要求3所述的筛选栅介质层可靠性的良率测试方法,其特征在于:步骤一中的所述刻蚀的方法为湿法刻蚀。

6.根据权利要求1所述的筛选栅介质层可靠性的良率测试方法,其特征在于:步骤一中的所述栅介质层的材料为二氧化硅。

7.根据权利要求1所述的筛选栅介质层可靠性的良率测试方法,其特征在于:步骤一中的所述栅极层的材料多晶硅。

8.根据权利要求1所述的筛选栅介质层可靠性的良率测试方法,其特征在于:步骤二中的所述高压模拟量包括字线电压和位线电压。

9.根据权利要求1所述的筛选栅介质层可靠性的良率测试方法,其特征在于:步骤二中的所述高压模拟量为5.5~8v。

10.根据权利要求1所述的筛选栅介质层可靠性的良率测试方法,其特征在于:步骤三中的所述预设时间为5至10s。

11.根据权利要求1所述的筛选栅介质层可靠性的良率测试方法,其特征在于:步骤四中根据所述高压模拟量是否发生漂移或所述die功能是否异常来判断所述测试结果是否超过卡控规格。

12.根据权利要求1所述的筛选栅介质层可靠性的良率测试方法,其特征在于:所述方法还包括步骤五、对所有的所述die进行功能测试,判断其功能是否异常,若是,则标记功能异常的所述die具有可靠性风险并输出对应的所述芯片分组编号。

技术总结本发明提供一种筛选栅介质层可靠性的良率测试方法,提供晶圆,在晶圆上形成有多个die,每个die具有对应的芯片分组编号,每个die上至少形成有一个PUMP电路,每个PUMP电路中具有至少一个电容结构,电容结构包括依次形成于衬底上的栅介质层和栅极层;选择待测试的PUMP电路,设置其高压模拟量和测试模式;对各待测试的PUMP电路施加电压值至对应高压模拟量的最大值,并持续预设时间;获取待测试PUMP电路的测试结果,判断测试结果是否超过卡控规格;若是,则标记其具有可靠性风险并输出对应的芯片分组编号。本发明能够筛选出栅介质层侧掏变薄导致的风险die,解决了经正常CP测试无法完全筛除风险die的问题。技术研发人员:陈灿,周桂喜,吴苑,冯叶受保护的技术使用者:华虹半导体(无锡)有限公司技术研发日:技术公布日:2024/9/2本文地址:https://www.jishuxx.com/zhuanli/20240905/288509.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。