具有超结沟槽栅的MOSFET器件及其制造方法与流程

- 国知局

- 2024-09-05 14:49:51

本发明涉及半导体,特别是涉及一种具有超结沟槽栅的mosfet器件及其制造方法。

背景技术:

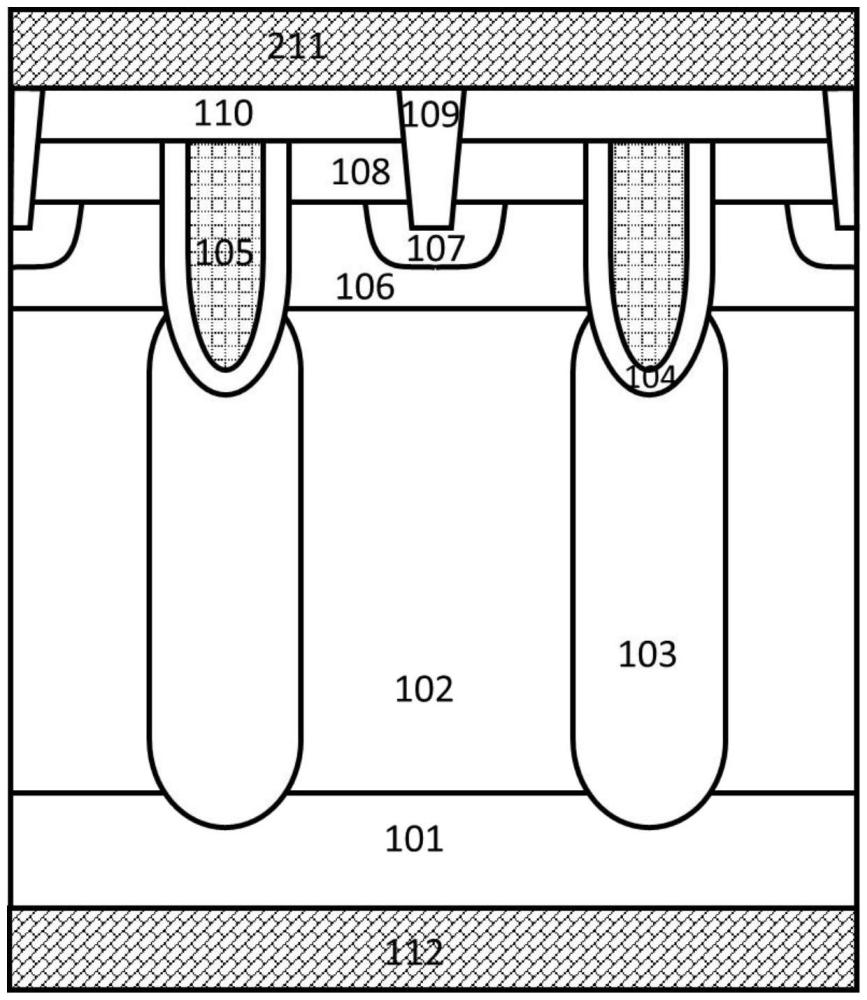

1、沟槽栅mosfet器件广泛用于功率转换电路,常用于功率开关器件。沟槽栅的导通电阻rsp和击穿电压bv是其重要的参数指标之一,获得更高的击穿电压,更低的沟槽栅的导通电阻可以提高产品的竞争力。为了改善中高压(50~200v)沟槽栅的导通电阻,通过注入实现的超结-沟槽栅概念被提了出来,如图1所示。

2、其中,各附图标记的含义包括:101为高掺杂n型衬底,102为n型外延层/n型漂移区(5e15~1e17cm^-3),103为辅助n型漂移区耗尽的p型注入区(p-pillar,ppl),104为栅介质层,105为栅极多晶硅,106为p型体区,107为p型重掺杂注入,108为n型重掺杂注入,109为接触孔,110为层间绝缘介质层,211为源端-体区端金属层,112为漏端金属层。

3、以n沟道沟槽栅为例,为了改善超结-沟槽栅器件的特性,用于辅助漂移区耗尽的p-pillar103的底端会尽可能的靠近高掺杂的衬底101以使得可耗尽的n型漂移区长。

4、但是通过注入形成的p-pillar,由于boron(硼离子)注入能量的限制,使得boron能量大于3500kev的工艺条件受到了限制,特别对于击穿电压>80v以上的要求(epi厚度>5um),boron注入能量需大于2500kev才能使得103的底端尽可能的靠近高掺杂的衬底101,但是高能量的boron注入给工艺集成带来极大的难度。

5、为解决上述问题,需要提出一种新型的具有超结沟槽栅的mosfet器件及其制造方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种具有超结沟槽栅的mosfet器件及其制造方法,用于解决现有技术中通过注入形成的辅助n型漂移区耗尽的p型注入区,由于boron(硼离子)注入能量的限制,使得boron能量大于3500kev的工艺条件受到了限制,高能量的boron注入给工艺集成带来极大的难度的问题。

2、为实现上述目的及其他相关目的,本发明提供一种具有超结沟槽栅的mosfet器件,包括:

3、在第一导电类型的衬底上外延形成的第二导电类型的外延层;

4、在所述外延层表面形成的第二导电类型的体区;

5、在所述体区顶部形成有栅沟槽,所述栅沟槽从所述外延层的上表面向下延伸穿过所述体区,在所述栅沟槽的底部形成有第一导电类型的柱体区,其中,所述柱体区的上端包裹所述栅沟槽的底部,所述柱体区的下端与所述衬底相接触;

6、在所述栅沟槽表面形成有栅介质层;剩余所述栅沟槽中填充有栅极多晶硅层;

7、在所述栅沟槽两侧的所述体区上方形成有源端重掺杂区,在所述栅极多晶硅层上形成有绝缘介质层,在所述源端重掺杂区上形成有接触孔,在所述接触孔下方的所述体区上形成有重掺杂区;

8、填充所述接触孔的导电金属,源端、体区端金属层以及漏端金属层。

9、优选地,所述第一导电类型为n型;所述第二导电类型为p型。

10、优选地,所述第一导电类型为p型;所述第二导电类型为n型。

11、优选地,所述外延层的掺杂浓度为5e15~1e17cm^-3。

12、优选地,所述柱体区由磷离子进行离子注入形成。

13、优选地,所述柱体区由多次磷离子的离子注入形成。

14、优选地,所述磷离子的注入剂量为1e12~1e13cm^-2,注入能量为50~5000kev。

15、优选地,所述栅介质层的材料为二氧化硅。

16、本发明还提供一种上述具有超结沟槽栅的mosfet器件的制造方法,包括:

17、步骤一、在第一导电类型的衬底上外延形成第二导电类型的外延层;

18、步骤二、利用离子注入的方法在所述外延层表面形成第二导电类型的体区,之后对所述体区进行热扩散推进;

19、步骤三、在所述体区顶部形成栅沟槽,所述栅沟槽从所述外延层的上表面向下延伸穿过所述体区,在所述栅沟槽表面形成离子注入保护层,利用离子注入在所述栅沟槽的底部形成第一导电类型的柱体区,其中,所述柱体区的上端包裹所述栅沟槽的底部,所述柱体区的下端与所述衬底相接触;

20、步骤四、去除所述离子注入保护层,在所述栅沟槽形成栅介质层;形成填充剩余所述栅沟槽的栅极多晶硅层;

21、步骤五、在所述栅沟槽两侧的所述体区上方形成源端重掺杂区,在所述栅极多晶硅层上形成绝缘介质层,在所述源端重掺杂区上形成接触孔,在所述接触孔下方的所述体区上进行重掺杂注入,经热扩散形成重掺杂区,同时激活所述重掺杂注入的杂质注入;

22、步骤六、形成填充所述接触孔的导电金属,之后形成源端、体区端金属层以及漏端金属层。

23、优选地,步骤一中的所述第一导电类型为n型;所述第二导电类型为p型。

24、优选地,步骤一中的所述第一导电类型为p型;所述第二导电类型为n型。

25、优选地,步骤一中的所述外延层的掺杂浓度为5e15~1e17cm^-3。

26、优选地,步骤三的所述在所述n型漂移区顶部形成栅沟槽的方法包括:在所述体区上形成自下而上依次堆叠的刻蚀停止层、硬掩膜层和光刻胶层;光刻打开所述光刻胶层以定义出所述栅沟槽的形成位置,之后利用刻蚀的方法在所述硬掩膜层上形成开口至所述刻蚀停止层上;去除所述光刻胶层,以所述硬掩膜层为掩膜刻蚀所述开口底部的所述刻蚀停止层、所述衬底以形成所述栅沟槽。

27、优选地,步骤三中的所述刻蚀停止层的材料为氮化硅。

28、优选地,步骤三中的所述硬掩膜层的材料为二氧化硅。

29、优选地,步骤三中在保留所述硬掩膜层、所述刻蚀停止层的情况下,利用热氧化的方法形成牺牲氧化层,通过热氧化修复所述栅沟槽刻蚀形成的缺陷,所述牺牲氧化层作为离子注入保护层。

30、优选地,步骤三中利用磷离子进行离子注入,在所述栅沟槽的底部形成n型的所述柱体区。

31、优选地,步骤三中的所述柱体区由多次离子注入形成。

32、优选地,步骤三中的所述磷离子的注入剂量为1e12~1e13cm^-2,注入能量为50~5000kev。

33、优选地,步骤四中以保留的所述硬掩膜层为离子注入的掩膜,以所述牺牲氧化层为所述离子注入保护层,利用自对准注入形成所述柱体区。

34、优选地,步骤四中在同一湿法刻蚀中去除所述牺牲氧化层和所述硬掩膜层,之后去除所述刻蚀停止层。

35、优选地,步骤四中的所述栅介质层的材料为二氧化硅。

36、优选地,步骤四中的所述栅介质层的形成方法包括:利用低温热氧化的方法形成第一栅氧化硅层;沉积teos氧化硅层作为第二栅氧化层,之后进行快速退火对teos氧化硅层进行致密化。

37、优选地,步骤四中的所述低温热氧化的温度为800至930摄氏度,处理时间小于30分钟。

38、优选地,步骤四中的所述第一栅氧化硅层的厚度为100至400埃。

39、优选地,步骤五中的所述接触孔采用光刻、刻蚀的方法形成。

40、优选地,步骤五中通过光刻、刻蚀形成所述接触孔后剩余的光刻胶进行带胶注入,形成所述源端重掺杂区。

41、如上所述,本发明的具有超结沟槽栅的mosfet器件及其制造方法,具有以下有益效果:

42、本发明降低了超结沟槽栅mosfet器件的制造工艺难度。

本文地址:https://www.jishuxx.com/zhuanli/20240905/288366.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。