高吞吐量扫描架构的制作方法

- 国知局

- 2024-09-14 14:43:01

本说明书涉及扫描架构和用于使用扫描架构的技术。

背景技术:

1、移动计算装置(诸如智能电话、个人数字助理、电子平板电脑、膝上型电脑等等)全部都依靠按设计运作的电路。由于制造过程中的缺陷,一些集成电路不按设计运作。可以执行制造或生产测试来验证电路被正确地制造并识别有故障的电路。由于通常必须对数千或甚至数百万个芯片或芯片组执行这些测试,因此耗费大量功率和处理资源来执行这些测试。因此,在测试过程中的任何低效都会引入呈浪费的功率和处理资源的形式的重大损失。测试和质量保证所需的时间也可能造成生产线的瓶颈。

技术实现思路

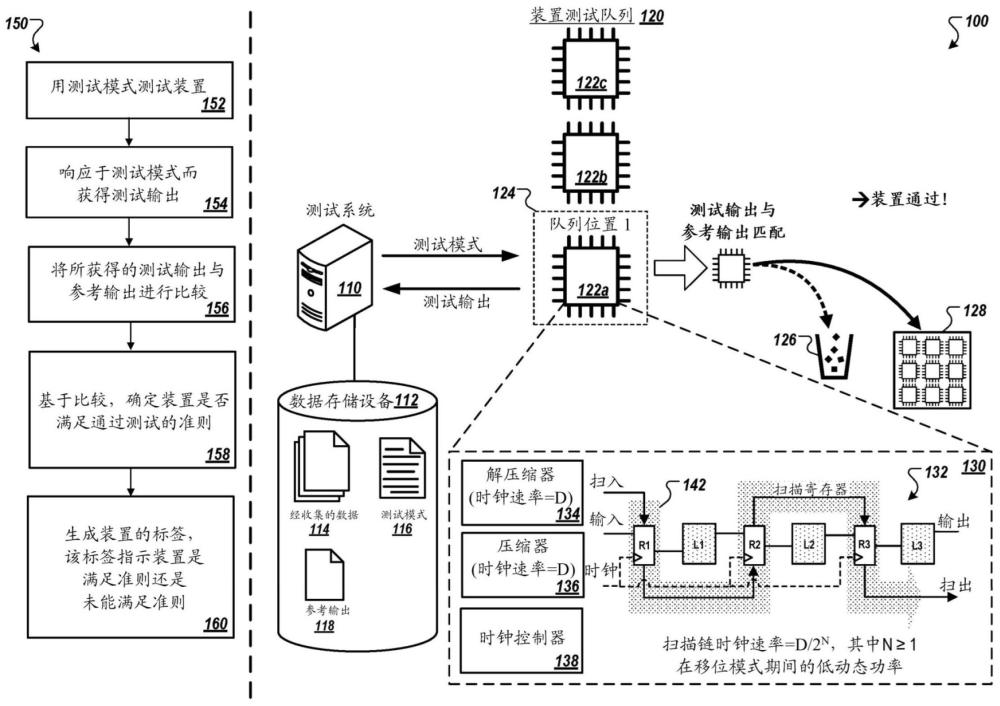

1、本说明书描述了用于测试数字装置的高吞吐量扫描架构的技术。所述技术对在制造结束时执行集成电路的质量保证和测试是特别有用的。扫描架构可以在电子装置(诸如计算机处理器)上实现并被用来确定电子装置是在正确地运作还是有缺陷。

2、扫描架构可以包括多个扫描链,所述多个扫描链各自包括多个系列锁存器。例如,高吞吐量扫描架构的每个扫描链可以包括组成第一系列的第一系列锁存器和组成第二系列的第二系列锁存器。第一系列锁存器和第二系列锁存器可以并发地(例如,并行地)操作,其中每个系列锁存器存储来自扫入数据信号的交替值(alternating value)。因此,第一系列和第二系列寄存来自由测试系统提供的测试模式的不同的值集。例如,这两个系列锁存器可以耦合到输入线,所述输入线将测试模式作为值序列提供。每个系列锁存器可以被安排成存储在序列中出现的每隔一个值,使得它们就哪个系列锁存器存储下一个值进行交替。延迟元件可以用于一个系列锁存器,因此提供偏移,使得两个系列锁存器各自存储输入测试模式的不同部分。换句话说,第一系列锁存器存储第一输入值,第二系列锁存器存储第二输入值,第一系列锁存器存储第三输入值,第二系列锁存器存储第四输入值,依此类推。以这种方式,在扫入阶段中在两个系列锁存器间分布测试模式序列。

3、稍后,在执行测试之后,在扫出阶段中由两个系列锁存器输出两个系列锁存器中的值,并且使来自两个系列锁存器的值穿插或交织在一起以形成扫出阶段的输出序列。例如,选择器可以通过依次从不同系列锁存器取得值,对于所述序列中的每个附加输出值在两个系列值之间切换来构成输出序列。换句话说,输出序列可以是来自第一系列锁存器的第一值、来自第二系列锁存器的第一值、来自第一系列锁存器的第二值、来自第二系列锁存器的第二值等等。以这种方式,(1)在扫入时,扫描链的输入序列被分散在不同系列锁存器之间,其中值以交替方式存储在不同系列锁存器中,并且(2)在扫出时,通过使不同系列锁存器的输出交织来形成输出序列。

4、所述系列锁存器可以以比扫描架构的其他组件更低的频率进行操作。例如,第一系列锁存器和第二系列锁存器可以在测试或移位模式期间以时钟速率进行操作,所述时钟速率是扫入数据信号的数据速率的一半。在这种模式中,两个系列锁存器都可以通过存储诸如从扫入数据信号获得的那些的值(例如,在扫入或移入时接收值)并以经分频的时钟速率释放值(例如,在扫出或移出期间输出)进行操作。

5、在电子装置的测试期间,测试系统可以选择测试模式以作为输入提供给扫描架构。测试模式可以包括一个或多个位流,所述一个或多个位流被用来将数据加载到扫描架构中的扫描链的锁存器中。测试模式还可以包括测试程序或者是测试程序的部分,所述测试程序提供扫描链的输入和输入的定时参数。例如,在对装置执行测试中,测试系统可以选择用于在装置上加载扫描链的锁存器的测试模式和要用于执行测试的程序。程序可以指定用于扫描链的锁存器的扫描使能(se)输入——例如,以使扫描链中的所述系列锁存器在移位模式与功能或捕获模式之间切换——和用于提供输入的定时。在提供测试模式作为输入并启用捕获或功能模式达一个或多个时钟循环之后,测试系统可以将所述系列锁存器切换回移位模式以移出经存储的值。经移出的值可以表示测试输出,测试系统可以将所述测试输出与参考输出进行比较以确定电子装置是在正确地运作还是有缺陷。例如,如果测试输出与参考输出不匹配,则测试系统可以确定电子装置是有缺陷的或要求进一步分析。

6、在一个一般方面,一种电子装置包括:时钟系统,所述时钟系统提供多个时钟信号,所述多个时钟信号包括处于第一频率的第一时钟信号和处于第二频率的第二时钟信号,所述第二频率小于所述第一频率;解压缩器,所述解压缩器被配置为接收所述第一时钟信号并基于所述第一时钟信号的所述第一频率以第一数据速率提供扫入输入值;扫描链,所述扫描链包括两个不同的锁存器集,所述两个不同的锁存器集被提供作为使用所述第二时钟信号进行操作的第一系列锁存器和第二系列锁存器,所述扫描链被配置为(i)在所述第一系列锁存器与所述第二锁存器系列之间分布所述扫入输入值,以及(ii)将来自所述第一系列锁存器和所述第二系列锁存器的值组合以提供扫出输出值;以及压缩器,所述压缩器被配置为接收所述第一时钟信号并从所述扫描链获得所述扫出输出值。

7、在另一个一般方面,一种电子装置包括:时钟控制器,所述时钟控制器提供多个时钟信号,所述多个时钟信号包括处于第一频率的第一时钟信号和处于第二频率的第二时钟信号,所述第二频率小于所述第一频率;解压缩器,所述解压缩器被配置为接收所述第一时钟信号并提供具有值集的第一数据信号,其中所述解压缩器被配置为基于所述第一时钟信号的所述第一频率以第一数据速率输出所述第一数据信号的值;扫描链,所述扫描链包括两个不同的锁存器集,所述两个不同的锁存器集被提供作为第一系列锁存器和第二系列锁存器,其中所述第一系列锁存器和所述第二系列锁存器两者都被配置为接收所述第一数据信号但从所述第一数据信号捕获不同的值子集,其中第一系列锁存器和所述第二系列锁存器两者都接收所述第二时钟信号并基于所述第二时钟信号的所述第二频率以第二数据速率从所述第一数据信号捕获值,并且其中所述扫描链被配置为通过将所述第一系列锁存器的输出与所述第二系列锁存器的输出组合来生成第二数据信号;以及压缩器,所述压缩器被配置为接收所述第一时钟信号并从所述扫描链获得所述第二数据信号,其中所述压缩器被配置为使用所述第一时钟信号根据所述第一频率以所述第一数据速率从所述扫描链获得所述第二数据信号。

8、实现方式可以包括以下特征中的一个或多个。例如,在一些实现方式中,从所述第一数据信号提取所述值集的所述不同的值子集包括:对于所述值集中的每个值,就两个系列锁存器中的哪个系列锁存器捕获所述值进行交替。

9、在一些实现方式中,从所述第一数据信号提取所述值集的所述不同的值子集包括:由所述第一系列锁存器捕获所述第一数据信号的每隔一个值;以及由所述第二系列锁存器捕获所述第一数据信号的未被所述第二系列锁存器捕获的其他值。

10、在一些实现方式中,生成所述第二数据信号包括使所述第一系列锁存器的所述输出与所述第二系列锁存器的所述输出交织。

11、在一些实现方式中,所述电子装置包括复用器,所述复用器被配置为接收所述第一系列锁存器的所述输出、所述第二系列锁存器的所述输出和所述第一时钟信号,其中生成所述第二数据信号包括控制所述复用器在以所述第一时钟信号的所述第一频率对所述第一系列锁存器的所述输出进行采样和对所述第二系列锁存器的所述输出进行采样之间交替。

12、在一些实现方式中,所述扫描链包括所述系列锁存器中的一个系列锁存器中的元件,所述元件在所述第一系列锁存器能够从所述第一数据信号捕获值的时间与所述第二系列锁存器能够从所述第一数据信号捕获值的时间之间引入定时差异。

13、在一些实现方式中,所述定时差异等同于所述第一时钟信号的一个循环。

14、在一些实现方式中,所述元件是锁定锁存器,并且所述第一系列锁存器和所述第二系列锁存器中的其他锁存器是触发器。

15、在一些实现方式中,所述元件是所述第一系列锁存器中的第一锁存器,使得由所述第一系列锁存器捕获的任何值在所述第一系列锁存器中的任何其他锁存器之前被加载到所述元件中或被传递通过所述元件,或者所述元件是所述第二系列锁存器中的第一锁存器,使得由所述第二系列锁存器捕获的任何值在所述第二系列锁存器中的任何其他锁存器之前被加载到所述元件中或被传递通过所述元件。

16、在一些实现方式中,所述元件是第一类型的触发器,并且所述第一系列锁存器和所述第二系列锁存器中的所述其他锁存器是第二类型的触发器。

17、在一些实现方式中,所述第一类型的所述触发器是具有主旁路的主从触发器;并且所述第二类型的所述触发器是没有主旁路的主从触发器。

18、在一些实现方式中,所述元件在所述第一系列锁存器与所述第二系列锁存器之间引入定时偏移;并且所述扫描链包括第二元件,所述第二元件消除在所述第一系列锁存器与所述第二系列锁存器之间的所述定时偏移。

19、在一些实现方式中,所述元件和所述第二元件两者都是所述第一系列锁存器的部分;或者所述元件和所述第二元件两者都是所述第二系列锁存器的部分。

20、在一些实现方式中,所述第二元件是所述第一系列锁存器中的最后一个锁存器,使得由所述第一系列锁存器捕获的任何值在到达所述第二元件之前必须传递通过所述第一系列锁存器中的所述其他锁存器中的每一个;或者所述第二元件是所述第二系列锁存器中的最后一个锁存器,使得由所述第二系列锁存器捕获的任何值在到达所述第二元件之前必须传递通过所述第二系列锁存器中的所述其他锁存器中的每一个。

21、在一些实现方式中,所述第二频率是所述第一频率的分频,使得所述第二频率等于所述第一频率除以二的大于零的整数次的乘方。

22、在一些实现方式中,所述整数是一;并且所述第二频率是所述第一频率的一半。

23、在一些实现方式中,所述整数是二;并且所述第二频率是所述第一频率的四分之一。

24、在一些实现方式中,所述时钟控制器包括频率分频器,所述频率分频器接收所述第一时钟信号并基于所述第一时钟信号来输出所述第二时钟信号。

25、在一些实现方式中,所述频率分频器是可编程频率分频器,所述可编程频率分频器被配置为以取决于所述可编程频率分频器的经编程的状态的频率输出可变时钟信号;并且所述第二时钟信号是可变时钟信号,所述可变时钟信号具有基于所述可编程频率分频器的所述经编程的状态的所述第二频率。

26、在一些实现方式中,所述解压缩器响应于所述电子装置接收启用所述电子装置的移位模式的一个或多个输入而提供所述第一数据信号。

27、在一些实现方式中,所述电子装置接收禁用所述电子装置的所述移位模式的一个或多个第二输入;并且所述扫描链被配置为响应于所述电子装置接收重启用所述电子装置的所述移位模式的一个或多个第三输入而生成所述第二数据信号。

28、在另一个一般方面,一种电子装置包括:时钟控制器,所述时钟控制器提供多个时钟信号,所述多个时钟信号包括处于第一频率的第一时钟信号、处于第二频率的第二时钟信号和处于第三频率的第三时钟信号,所述第二频率小于所述第一频率,所述第三频率小于所述第一频率和所述第二频率;解压缩器,所述解压缩器接收所述第一时钟信号并提供具有值集的第一数据信号,其中所述解压缩器被配置为基于所述第一时钟信号的所述第一频率以第一数据速率输出所述第一数据信号的值;扫描链,所述扫描链包括四组不同的锁存器,所述四组不同的锁存器被提供作为第一组锁存器、第二组锁存器、第三组锁存器和第四组锁存器,其中所述四组不同的锁存器中的每一组锁存器具有第一系列锁存器和第二系列锁存器,其中所述第一组锁存器的所述第一系列锁存器和所述第二系列锁存器两者都被配置为:接收所述第一数据信号但从所述第一数据信号捕获不同的值子集;以及接收所述第二时钟信号并基于所述第二时钟信号的所述第二频率以第二数据速率从所述第一数据信号捕获值;其中所述第二组锁存器的所述第一系列锁存器和所述第二系列锁存器两者都被配置为:接收所述第一组锁存器的所述第二系列锁存器的输出;以及接收所述第三时钟信号并基于所述第三时钟信号的所述第三频率以第三数据速率从所述第一组锁存器的所述第二系列锁存器的所述输出捕获值;其中所述第三组锁存器的所述第一系列锁存器和所述第二系列锁存器两者都被配置为:接收所述第一组锁存器的所述第一系列锁存器的输出;以及接收所述第三时钟信号并基于所述第三时钟信号的所述第三频率以第三数据速率从所述第一组锁存器的所述第一系列锁存器的所述输出捕获值;并且其中所述第四组锁存器的所述第一系列锁存器和所述第二系列锁存器两者都被配置为:接收第二数据信号,所述第二数据信号含有所述第二组锁存器的输出和所述第三组锁存器的输出;以及接收所述第二时钟信号并基于所述第二时钟信号的所述第二频率以第二数据速率从所述第二数据信号捕获值;其中所述扫描链被配置为通过将所述第四组锁存器的所述第一系列锁存器的输出与所述第四组锁存器的所述第二系列锁存器的输出组合来生成第三数据信号;以及压缩器,所述压缩器接收所述第一时钟信号并从所述扫描链获得所述第三数据信号,其中所述压缩器被配置为使用所述第一时钟信号根据所述第一频率以所述第一数据速率从所述扫描链获得所述第三数据信号。

29、在另一个一般方面,一种方法包括:接收表示特定数据模式的值集;使用所述值集中的值的至少部分来生成第一数据信号,其中所述第一数据信号具有第一频率;使用第一系列锁存器和第二系列锁存器来从所述第一数据信号提取值的所述至少部分的交替值,其中所述第一系列锁存器和所述第二系列锁存器以第二频率提取所述交替值,所述第二频率是所述第一频率的分数;以及将所述第一系列锁存器的输出与所述第二系列锁存器的输出组合以生成第二数据信号,其中所述第二数据信号具有所述第一频率。

30、这些方面的其他实施例包括被配置为执行方法的动作的对应的系统和设备。

31、本说明书中描述的主题可以在特定实施例中实现,以便实现以下优点中的一个或多个。例如,所描述的扫描架构可以实现改进的动态功耗。这个益处是至少部分地通过扫描架构中采用的扫描链和时钟网络的设计来实现的。通过使用包括两个或更多个系列锁存器的扫描链并通过降低所述系列锁存器进行操作的频率(例如,锁存器存储和释放位的频率),降低了扫描架构在处于测试模式(例如,与功能模式相反的移位模式)时使用的动态功率。

32、由扫描架构提供的动态功率节省是至少通过在时钟网络中使用的动态功率的降低和在扫描架构的扫描链的锁存器中使用的动态功率的降低来实现的。首先,扫描架构中的所述系列锁存器进行操作的频率可以是扫描架构的其他组件进行操作的频率的分频。因此,时钟网络的动态功率被大幅地分频。其次,由于扫描架构中的扫描链的锁存器以一个或多个经分频的频率进行操作,因此降低了在锁存器内部使用的时钟相关动态功率。

33、在每个扫描链中使用多个系列锁存器中,扫描架构可以在不增加测试时间的情况下实现降低的动态功率。更详细地,使用以作为扫描架构的其他组件进行操作的频率的分频的频率进行操作的多个系列锁存器抵消了原本因降低锁存器进行操作的频率而预期将发生的测试时间的任何增加或显著增加。这是因为传入数据信号的位在扫描链的两个或更多个系列锁存器之间进行分频。例如,如果扫描架构中的锁存器以时钟控制器的未分频的时钟速率的一半进行操作,则扫描架构可以通过使用各自包括两个系列锁存器的扫描链继续以未分频的时钟速率产生输出数据信号。因此,扫描架构提供了在不增加或显著地增加测试时间的情况下降低动态功率从而提高测试效率的附加益处。

本文地址:https://www.jishuxx.com/zhuanli/20240914/295627.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。