数据锁存电路、半导体装置及半导体存储装置的制作方法

- 国知局

- 2024-09-14 14:50:50

本实施方式涉及一种数据锁存电路、半导体装置及半导体存储装置。

背景技术:

1、作为半导体存储装置的一种,已知有nand(not-and,与非)型存储器。

技术实现思路

1、本发明提供一种能够削减电路面积的数据锁存电路、半导体装置及半导体存储装置。

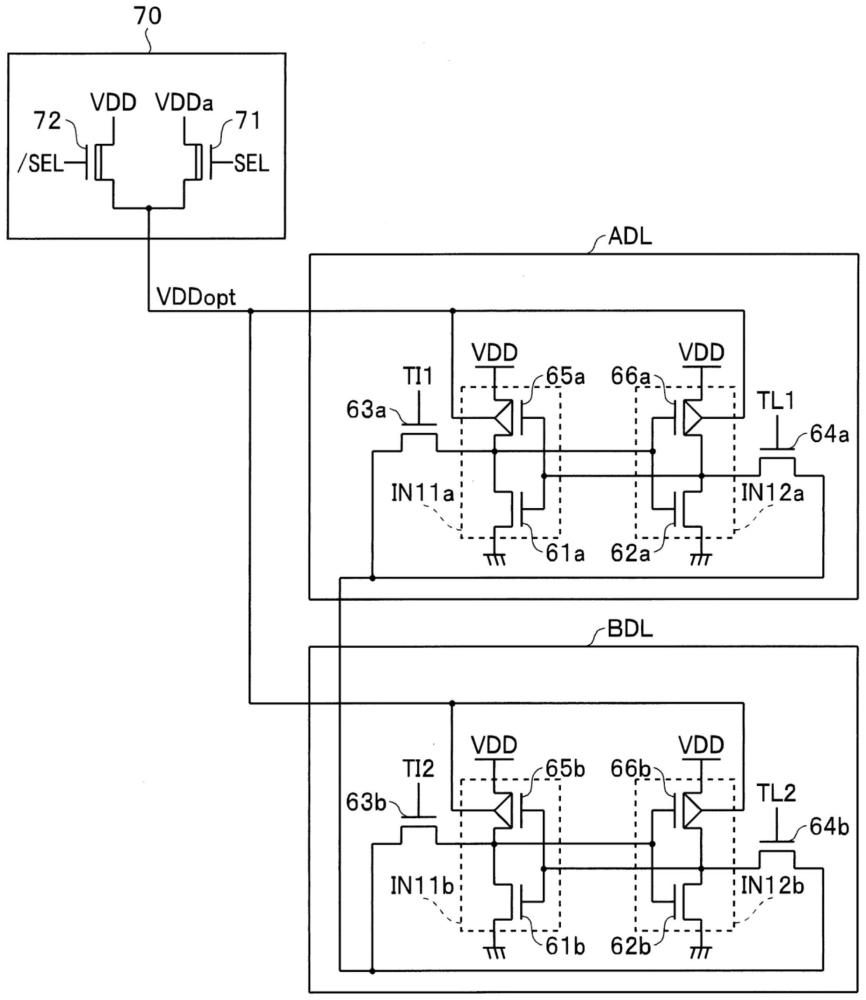

2、本实施方式的数据锁存电路具有第1电路及第2电路。第1电路,其中第1导电型的第1晶体管和与第1导电型不同的第2导电型的第2晶体管串联连接,且所述第1电路能够保存第1逻辑值。第2电路,其中第1导电型的第3晶体管和第2导电型的第4晶体管串联连接,且所述第2电路能够保存第1逻辑值反转所得的第2逻辑值。数据锁存电路能够对第1晶体管及第3晶体管的背栅极施加第1电压及与第1电压不同的第2电压中的任一种,且能够对第1晶体管及第3晶体管的源极施加第3电压。

技术特征:1.一种数据锁存电路,具有:

2.根据权利要求1所述的数据锁存电路,其中

3.一种数据锁存电路,具有:

4.根据权利要求3所述的数据锁存电路,其中

5.根据权利要求1至4中任一项所述的数据锁存电路,其中所述第1电压与所述第3电压为相同电位。

6.一种半导体装置,具有:

7.根据权利要求6所述的半导体装置,其中

8.根据权利要求6所述的半导体装置,其中

9.根据权利要求6所述的半导体装置,其

10.根据权利要求6所述的半导体装置,其

11.根据权利要求6所述的半导体装置,其

12.一种半导体存储装置,具备:

技术总结本发明提供一种能够削减电路面积的数据锁存电路、半导体装置及半导体存储装置。本实施方式的数据锁存电路具有第1电路及第2电路。第1电路,其中第1导电型的第1晶体管和与第1导电型不同的第2导电型的第2晶体管串联连接,且所述第1电路能够保存第1逻辑值。第2电路,其中第1导电型的第3晶体管和第2导电型的第4晶体管串联连接,且所述第2电路能够保存第1逻辑值反转所得的第2逻辑值。数据锁存电路能够对第1晶体管及第3晶体管的背栅极施加第1电压及与第1电压不同的第2电压中的任一种,且能够对第1晶体管及第3晶体管的源极施加第3电压。技术研发人员:渡邉稔史,樱井清史,东辻哲平,小崎琢弥,狐塚英二受保护的技术使用者:铠侠股份有限公司技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/296141.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表