用于调度块请求的存储设备和方法与流程

- 国知局

- 2024-09-14 14:53:58

与本公开的示例实施例一致的系统、装置和方法涉及存储器访问,并且具体地,涉及用于调度来自块设备的存储器请求的存储设备和方法。

背景技术:

1、现代企业和数据中心的工作负载,包括最新引人注目的大型语言模型(llm),都在冲击存储器墙(即带宽墙和容量墙)。为了解决这些问题,正在考虑新的以存储器为中心的计算体系结构,诸如计算快速链路(cxl)标准。引入cxl标准是为了在主机设备和其他设备之间提供高速连接。cxl协议建立在外围组件互连快速(pcie或pci-e)标准之上,其是用于将主机设备连接到一个或多个块设备和/或外围设备的串行扩展总线标准。主机设备可以包括执行需要大量存储器资源的各种应用的中央处理单元(cpu)。块设备可以包括存储设备(例如,硬盘设备(hdd)、固态驱动器(ssd)等,并且外围设备可以包括但不限于其他处理器(例如,图形处理单元(gpu)、神经处理单元(npu)等)、加速器、智能网络接口控制器(nic)。

2、在本背景技术部分中公开的信息在实现本申请的实施例之前已经为发明人所知,或者是在实现本文描述的实施例的过程中获得的技术信息。因此,它可能包含不构成公众已知的现有技术的信息。

技术实现思路

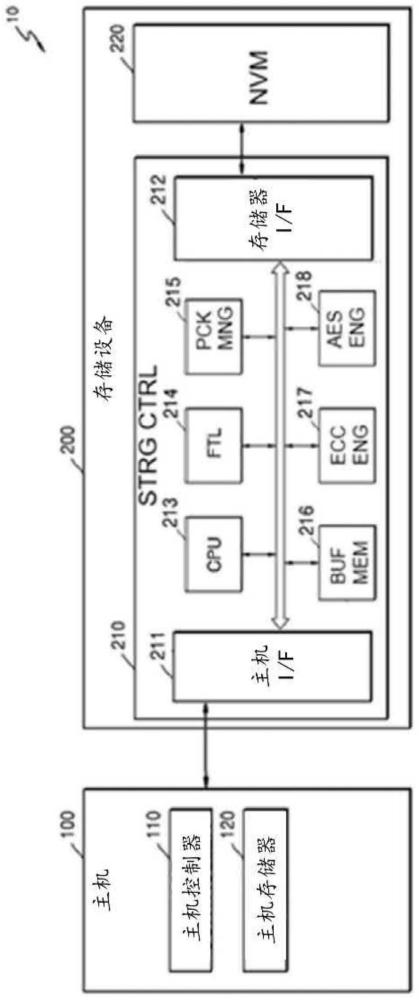

1、通常,主机设备(以下称为“主机”)通过存储器控制器访问存储在块设备中的数据。图1a是示出根据现有技术的主机、存储器控制器和块设备(例如,ssd)之间的操作的图。如图1a所示,存储器控制器30a通过主机接口15a从主机10a接收存储器请求,并将存储器请求放入队列31a中。存储器控制器30a中的存储器高速缓存32a可以接收队列31a中排队的存储器请求,并将队列中与接收的存储器请求相对应的逻辑块地址(lba)输出到块请求生成器33a。在此,存储器高速缓存32a可以是动态随机存取存储器(dram)。块请求生成器33a可以通过块接口16a向块设备20a发送块请求,以从块设备20a获取数据块并将获取的数据块存储在存储器高速缓存32a中。随后,存储器高速缓存32a通过高速缓存线将高速缓存的数据输出到存储器响应生成器34a,并且存储器响应生成器346a通过主机接口15a将获取的数据发送到主机10a。

2、然而,在存储器控制器30a中操作存储器高速缓存32a是复杂的、繁琐的,并且在高速缓存条目的有效管理方面引起各种开销,并且需要额外的算法,诸如逐出算法、预取算法等。此外,dram和类似dram组件增加了成本。因此,高速缓存存储器和高速缓存数据的成本影响计算机系统的整体性能和成本。

3、为了解决存储器高速缓存存储器32a和使用图1a所示的存储器高速缓存32a的存储器控制器30a的缺点,如图1b所示,提供了一种主机存储器系统和用于在主机-存储器系统中服务顺序存储器访问的方法。根据图1b所示的比较系统,主机-存储器系统可以包括主机10b、存储器控制器30b和块设备20b。图1b所示的比较系统可以是基于cxl标准执行存储器访问的系统。存储器控制器30b通过主机接口15b接收来自主机10b的存储器请求(c1,…,cn),并将请求放置在队列31b中。存储器请求(c1,…,cn)可以是cxl请求。存储器控制器30b中的块请求生成器33b逐个地接收排队的存储器请求。例如,块请求生成器33b接收与存储器请求c1相对应的主机物理地址(hpa)。块请求生成器33b将hpa转换为逻辑块地址(lba),并通过块接口16b将基于lba的块请求发送到块设备20b,以从块设备20b获取数据块。从块设备20b获取的数据块被存储在内部缓冲器32b中。随后,响应生成器34b从内部缓冲器32b接收数据块,并使用数据块生成用于存储器请求c1的存储器响应c1。图1b中所示的比较系统的优点之一是其在没有内部高速缓存的情况下操作。然而,存储在内部缓冲器32b中的数据将被丢弃,并且对应于下一个存储器请求c2的新数据块将被存储在内部缓冲器32b中。因此,在比较系统的存储器控制器30b中,与多个存储器请求中的一个存储器请求c1(即,cxl读取请求)相对应地读取一个闪存页(例如,块x),并将其存储在内部缓冲器中,随后将其输出到主机作为存储器响应c1。在完成一个存储器请求时,闪存页被丢弃,从而导致比较系统中的低效率。

4、本公开的各种示例实施例提供了一种用于有效地服务于对块设备的顺序存储器访问的系统、存储设备和方法。

5、根据本公开的一个方面,主机存储器系统及其操作方法可以使用页面对准的存储器访问,跟踪具有业务类的后续块请求,和/或根据块地址绑定存储器请求。页面对准的存储器访问可以在各种应用和分层存储器体系结构中实现。设备块大小也与存储器页面大小对准,这最佳地导致零输入/输出(io)放大。例如,假设64b主机高速缓存线、4kb主机存储器页面和4kb设备块,则可以在单个闪存页面中执行64顺序存储器访问。此外,随机存储器访问可以以具可比性的性能被提供服务,因为随机访问的高速缓存命中率低是常见的。因此,代替使用内部高速缓存,可以使用业务类和根据块地址绑定存储器请求来跟踪后续块请求。

6、例如,在存储器请求是cxl请求的情况下,由于性能差距,cxl请求的绑定可能是高效的。例如,cxl 2.0(pcie5x4)的带宽(16gb/s)与存储设备的带宽(存储设备可以以10gb/s的速度执行4kb随机读取和2gb/s的随机写入)可能存在差异。cxl 2.0与存储设备之间的差距表明,性能存在显著差异,cxl 2.0更快。因此,根据各种示例实施例的系统和方法利用性能差距来有效地服务于顺序存储器访问,而不使用内部高速缓存。

7、根据本公开的一个方面,提供了一种存储器控制器,包括:接口,被配置为从主机接收存储器请求;以及处理器,被配置为:在存储存储器请求的队列中获取存储器请求,将存储器请求的目的地地址与储存装置中的一个或多个存储目的地地址中的第一存储目的地地址进行比较,基于存储器请求的目的地地址与储存装置中的第一存储目的地地址之间的匹配将存储器请求与储存装置中的第一存储目的地地址相关联,并且响应于存储器请求处理储存装置中的一个或多个条目。

8、根据本公开的另一方面,提供了一种存储器控制器,包括:接口,被配置为从主机接收存储器请求;以及处理器,被配置为:从接口接收存储器请求,将存储器请求的目的地地址与储存装置中的一个或多个存储目的地地址进行比较,基于存储器请求的目的地地址与一个或多个存储目的地地址中的第一存储目的地地址匹配,基于第一存储目的地地址处理存储器请求,以及基于存储器请求的目的地地址未命中一个或多个存储目的地地址,将存储器请求的目的地地址添加为存储器中的新条目。

9、根据本公开的另一方面,提供了一种存储器控制器,包括:第一接口,被配置为与储存设备通信;以及处理器,被配置为:从包括一个或多个信息的存储器获得第一信息,一个或多个信息中的每一个包括彼此相关联的目的地地址、存储器操作和一个或多个存储器请求中的一个,确定存储器操作的类型,以及基于存储器操作的类型处理第一信息。

技术特征:1.一种存储器控制器,包括:

2.根据权利要求1所述的存储器控制器,还包括:多个队列,每个队列存储一个或多个存储器请求,

3.根据权利要求1所述的存储器控制器,其中,处理器被配置为基于存储器请求的目的地地址未命中储存装置中的一个或多个存储目的地地址的确定,在储存装置中添加与存储器请求相对应的新条目。

4.根据权利要求1所述的存储器控制器,其中,处理器被配置为处理储存装置中的一个或多个条目以产生用于访问存储设备的块输入/输出io请求,以及

5.根据权利要求1所述的存储器控制器,其中,一个或多个存储目的地地址对应于由处理器获取的另一存储器请求。

6.根据权利要求1所述的存储器控制器,其中,多个队列被配置为根据基于存储器访问的一个或多个特性定义的业务类来存储多个存储器请求。

7.根据权利要求1所述的存储器控制器,其中,多个队列中的第一队列被配置为包括与第一业务类相对应的第一存储器请求,

8.根据权利要求1所述的存储器控制器,其中,存储器请求是计算快速链路(cxl)请求。

9.根据权利要求1所述的存储器控制器,其中,目的地地址是逻辑块地址(lba)。

10.一种存储器控制器,包括:

11.根据权利要求10所述的存储器控制器,其中,储存装置是缓冲器。

12.根据权利要求10所述的存储器控制器,其中,一个或多个存储目的地地址被存储在表中。

13.根据权利要求10所述的存储器控制器,其中,处理器被配置为通过将存储器请求与第一存储目的地地址相关联而基于一个或多个存储目的地地址来处理存储器请求。

14.根据权利要求11所述的存储器控制器,其中,存储器请求是读取请求或写入请求。

15.根据权利要求10所述的存储器控制器,其中,处理器被配置为:当存储器请求是从处于未决写入状态的第一存储目的地地址读取的读取请求时,通过从与第一存储目的地地址相对应的信息复制数据,基于一个或多个存储目的地地址来处理存储器要求。

16.根据权利要求10所述的存储器控制器,其中,存储器请求包括计算快速链路(cxl)请求。

17.一种存储器控制器,包括:

18.根据权利要求17所述的存储器控制器,其中,储存装置是缓冲器。

19.根据权利要求17所述的存储器控制器,其中,一个或多个信息被存储在表中。

20.根据权利要求17所述的存储器控制器,其中,处理器被配置为:

技术总结提供一种包括接口和处理器的存储器控制器。处理器从主机获取存储多个存储器请求的多个队列的一个中的存储器请求,将存储器请求的目的地地址与储存装置中的一个或多个存储目的地地址中的第一存储目的地地址进行比较,基于存储器请求的目的地地址与储存装置中的第一存储目的地地址之间的匹配将存储器请求与储存装置中的第一存储目的地地址相关联,以及响应于存储器请求处理储存装置中的一个或多个条目。技术研发人员:李好彬,瑞卡·皮楚马尼受保护的技术使用者:三星电子株式会社技术研发日:技术公布日:2024/9/12本文地址:https://www.jishuxx.com/zhuanli/20240914/296308.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表