一种集成电路设计流程中关键数据的提取与展示的方法与流程

- 国知局

- 2024-10-09 15:32:09

本项发明涉及集成电路设计,涉及一种集成电路设计流程中关键数据的提取与展示的方法。

背景技术:

1、在集成电路的设计流程中,因为电路规模非常庞大,设计工程师通常需要将一个完成的流程拆分成多个相对独立的模块,且每个模块都具有前后依赖关系。整个流程如同一张巨大的有向无环图,为确保整张图的流程能完整且正确的运行,就需要先保证图中每个节点模块能正确运行。若一个节点运行错误,其后所依赖的节点都不可运行。

2、在这样的环境下,监控节点模块的运行,判断其运行状态,及时发现并定位错误就显得尤为重要。判断每个节点模块正确性至少要保证两点:

3、1. 模块运行完成;

4、2. 模块运行过程中产生的关键数据在正常范围内。

5、这两点都比较好理解,监控模块运行完成很容易,但提取模块运行过程中的关键数据就比较复杂,因为每个模块的关键数据都可能不一样,位于不同的文件中,且文件格式也可能不相同。例如有的可能是文本文件,有的可能是压缩文件,或者有些数据可能需要在出现某个关键信息后才能开始提取。因此,在集成电路的设计流程中,为确保整个流程的完整性和正确性,很有必要设计一种通用且灵活的关键数据提取方案。

6、集成电路的设计流程是一个非常复杂,非常耗时的流程,且流程中的每个节点可能是串行的,也可能是并行的,一旦发生错误,单靠人工排查是非常不方便的。对运行出错的节点还好说,若节点能正常运行,但数据不在正常范围内,人工排查起来更麻烦。

7、在验证集成电路的设计流程是否正确的过程中,工程师通常需要根据不同的输入数据,比较不同的输出结果,找出潜在隐藏的问题。对于 gpu/cpu/5g 等超大规模数字芯片,流程验证的时间可能需要数天,在数十次迭代的情况下,对关键数据的提取和验证在排查错误的过程中就显得尤为重要。

技术实现思路

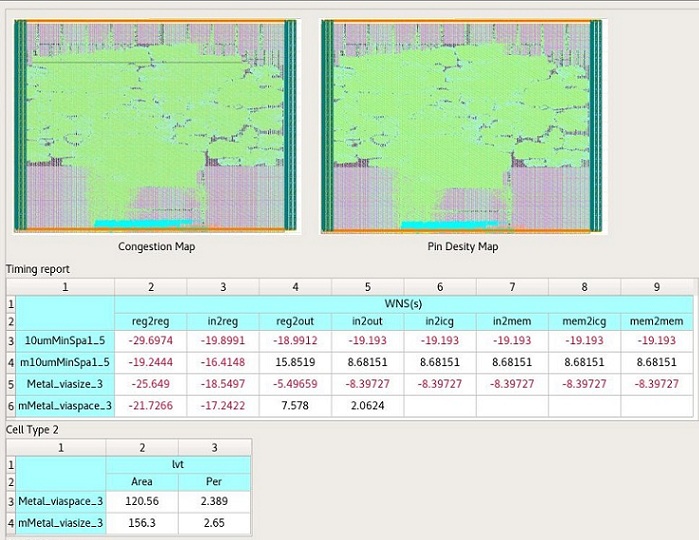

1、本项发明主要用于验证集成电路的设计流程是否正确,为异常的输出提供排查方向。本发明在集成电路设计流程中,提供一种通用的配置方法提取并展示集成电路设计流程中每个节点模块的关键数据信息,并通过表格、图表或图片形式显示,方便用户查看和分析数据。本发明是通过如下技术方案实现的:使用标准通用的json数据定义关键数据的提取格式和显示模板;使用字符串匹配算法,根据用户定义的格式从日志文件中提取数据,支持通配符和忽略符;最后根据定义的模板,采用绘图算法,以表格、折线图或柱状图的方式展示芯片设计流程中各节点模块的关键信息;

2、针对芯片设计流程中不同节点对应的数据内容并不相同,使不同节点可配置不同的数据提取格式,且同时支持文本和压缩格式的日志文件;若用户想忽略该节点的数据,则不用配置任何提取信息,系统会认为该节点不需要提取数据,在数据提取过程中直接跳过该节点;

3、对关键数据的展示同样也是使用json数据格式进行设置,按照用户定义的顺序进行结果展示;每种数据中都包含类型和名称两个固定属性,类型包括图片、表格、折线图和柱状图,名称由用户自定义;包括:

4、(1)图片类型需要设置图片名称和图片路径;

5、(2)表格类型需要设置行列名称和数据的计算函数和计算参数;

6、(3)图表设置数据源和数据范围,包含起始和终止的行列号,还需要设置显示的坐标轴。

7、本发明的有益效果是:

8、本发明方案用于在集成电路设计流程中,提取每个节点的关键数据,并用于展示和分析。它具有以下几个优势:

9、(1)通用性:本发明中采用字符串匹配算法,用户可以根据自身的数据样式来设置数据提取的格式,并且通过处理特殊字符来实现模糊匹配和忽略跳过的功能。另外,匹配后的键值可由用户自定义,用户可以根据实际情况来定义有意义的键值,使之与提取的关键数据一一对应,方便后期做数据展示和数据分析。

10、(2)提供可视化结果:对于提取的关键数据,除了以表格形式展示外,还提供了统计图的展示,比如折线图和柱状图等。可以方便用户进行直观的比较。

11、(3)快速精确的定位:对于异常数据,即小于0或者数量级特别大的数据,用户可以快速而精确的定位到数据所在的日志中,比如对异常数据进行双击操作,十分方便用户排查日志,定位问题。

12、综上所述,基于本方案对集成电路设计流程中的关键数据进行提取、展示和分析,可以有效的帮助设计人员定位问题,提高效率,能很大程度的降低在芯片开发过程中的设计风险,节约用户的成本和时间。

13、本发明提取关键数据的目标是确保电路设计流程中的每个步骤都能满足预定要求,提高电路设计的正确性和可靠性。对数据的展示也能直观显示设计流程中每一步的状态信息、敏感数据和错误数据,并生成统计图用于参考分析,方便设计工程师排查电路设计中的错误,降低设计风险,提供优化方向。

技术特征:1.一种集成电路设计流程中关键数据的提取与展示的方法,其特征在于,包括使用标准通用的json数据定义关键数据的提取格式和显示模板;使用字符串匹配算法,根据用户定义的格式从日志文件中提取数据,支持通配符和忽略符;最后根据定义的模板,采用绘图算法,以表格、折线图或柱状图的方式展示芯片设计流程中各节点模块的关键信息;

2.根据权利要求1所述的集成电路设计流程中关键数据的提取与展示的方法,其特征在于,对不同类型的数据格式进行具体设置,包括:

技术总结本项发明公开了一种在集成电路设计流程中关键数据的提取与展示的方法,涉及集成电路设计技术领域。在验证集成电路设计流程时采用本发明简单通用的数据定义格式,并基于此格式对集成电路设计流程中产生的关键数据进行提取、展示和分析,并生成直观的表格、图表和图片显示给用户。在验证集成电路设计流程时,因为电路规模庞大,会导致整个验证过程非常漫长,如何有效的发现错误,定位错误就显得尤为重要。这其中通过对关键数据的提取和分析就能很好的方便用户进行排错和优化,进一步弥补了工程师的经验不足,提升设计效率。本发明中的方法帮助用户更好的发现和解决问题,既提高电路设计的准确性,也极大的节省了时间成本和人工成本。技术研发人员:马雅威,李庆昌受保护的技术使用者:济南日观科技有限公司技术研发日:技术公布日:2024/9/29本文地址:https://www.jishuxx.com/zhuanli/20241009/309068.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。