抗浪涌电路、控制电路及抗浪涌方法与流程

- 国知局

- 2024-10-21 14:19:56

本技术涉及器件保护,具体而言,涉及一种抗浪涌电路、控制电路及抗浪涌方法。

背景技术:

1、在crm(critical conduction mode,临界导通模式)的led控制芯片中,通常由vin连接输入电压,cs连接led灯、电感等负载电压。当电感电流为峰值时,电感为led灯供电,高压功率mos管关闭;当电感电流为零时,高压功率mos管导通从而继续为led供电,同时电感储存能量,以保证led恒流工作。由于存在高压功率mos管,因此,也存在与其对应的寄生npn以及寄生电阻。

2、目前通常会设计分流的外部电解电容通路,外部电路和芯片内部的高压功率mos管之间的通路,以及外部电路和芯片内部的寄生npn形成的通路这三条电阻较小的通路,以这三条通路作为浪涌发生时的泄放通路。但是,当有浪涌经过时,高压功率器件导通工作状态下会加大浪涌发生时的电流,导致高压功率mos管的衬底、寄生npn与寄生电阻之间的连接节点电压增高,泄放时通过芯片内部通路的浪涌较大,从而导致芯片被烧毁等不利情况。

技术实现思路

1、有鉴于此,本技术实施例的目的在于提供一种抗浪涌电路、控制电路及抗浪涌方法,以改善现有技术中存在的芯片内部浪涌较大导致的芯片被烧毁的问题。

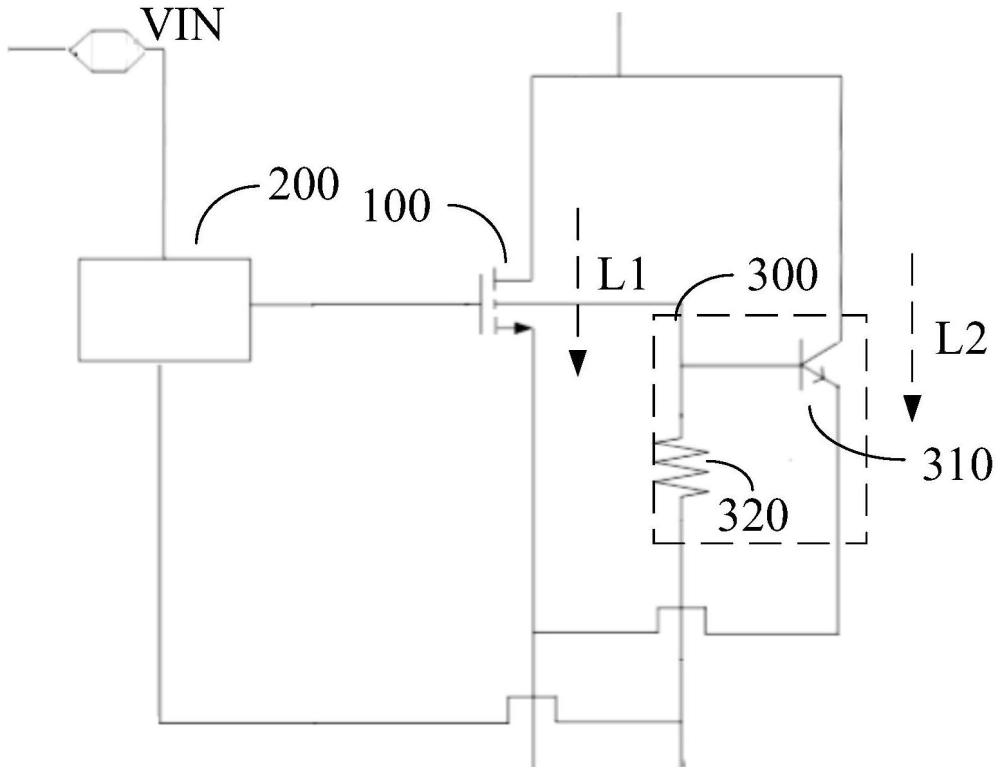

2、为了解决上述问题,第一方面,本技术实施例提供了一种抗浪涌电路,所述抗浪涌电路包括:输入模块、功率管、检测模块和基于所述功率管形成的寄生模块;其中,基于所述功率管形成泄放浪涌的第一浪涌通路,基于所述寄生模块形成泄放浪涌的第二浪涌通路;

3、所述输入模块与所述检测模块连接,所述检测模块与所述功率管连接;

4、所述输入模块用于为所述抗浪涌电路提供输入电压,所述检测模块用于对所述输入电压的浪涌进行检测,生成控制所述功率管的浪涌信号;

5、其中,若所述功率管被关断,则所述第一浪涌通路和所述第二浪涌通路断路。

6、在上述实现过程中,由于功率管为高压器件,因此,会存在对应的寄生模块,且功率管和寄生模块会分别形成两条用于泄放浪涌的浪涌通路。为了减少芯片内部泄放的浪涌,通过在电路中设置相应的检测模块对输入电压的浪涌情况进行检测,以根据检测得到的浪涌信号对功率管进行控制,能够在产生浪涌时实时地关断功率管,从而断开芯片内部泄放浪涌的两条浪涌通路,减少浪涌时芯片内部各器件的工作功率,以减少各个器件超功率过载导致的击穿等情况,从而减少芯片被烧毁的不利情况,有效地保护芯片中的各个器件,提高了芯片使用时的安全性,延长了芯片的使用寿命,从而降低控制电路的修复、替换成本。

7、可选地,所述寄生模块包括:寄生管和寄生电阻;

8、所述寄生管的基极和所述寄生电阻的第一端与所述功率管的衬底连接;

9、所述寄生电阻的第二端接地;

10、所述寄生电阻用于为所述寄生管提供基极低电位,所述寄生管用于基于所述基极低电位截止导通,以断开所述第二浪涌通路。

11、在上述实现过程中,由高压的功率管产生的寄生模块包括寄生管和相应的寄生电阻,寄生管的基极、寄生电阻的第一端与功率管的衬底连接,以对功率管进行接地处理。寄生电阻能够为寄生管的基极提供的较低的电位,以使寄生管能够基于基极低电位截止导通,从而使第二浪涌通路处于未触发的断路状态,减少第二浪涌通路的浪涌泄放量,从而减少寄生模块中产生的电流大小,减少寄生模块中各个器件被烧毁的情况。

12、可选地,其中,所述寄生电阻包括并联电阻;所述并联电阻的第一端与所述功率管的衬底连接,所述并联电阻的第二端接地。

13、在上述实现过程中,为了进一步地减小寄生管的基极电位,可以将功率管设置为具有并联电阻的功率管,以产生相应的并联电阻作为寄生电阻,有效地减小了寄生电阻的阻值,并基于寄生电阻对功率管进行接地处理,减少了第二浪涌通路的触发情况,减少因寄生电阻较大时会根据功率管关断时衬底的漏电流导通第二浪涌通路的不利情况,从而提高了芯片内部的抗浪涌效果。

14、可选地,其中,所述并联电阻由所述功率管的有源区域与多晶材料层连接形成。

15、在上述实现过程中,可以将功率管中的有源区域与多晶材料层进行连接,以生成有源区域的电阻与多晶材料层的电阻并联而成的并联电阻,能够在节约功率管工艺和材料成本的基础上降低寄生电阻的阻值。

16、可选地,其中,所述并联电阻由所述功率管的有源层与金属层连接形成。

17、在上述实现过程中,可以将功率管中的有源层与添加的金属层进行连接,以生成有源层的电阻与金属层的电阻并联而成的并联电阻,能够基于添加的金属层结构有效地降低寄生电阻的阻值。

18、可选地,其中,所述浪涌信号包括:表征浪涌情况的高电平信号和表征非浪涌情况的低电平信号;

19、所述检测模块包括:检测器件和延时器件,所述检测器件与所述延时器件连接;

20、所述检测器件用于对所述输入电压的浪涌情况进行检测,以生成所述高电平信号,所述延时器件用于根据延时阈值对所述高电平信号进行处理,生成相应的所述低电平信号。

21、在上述实现过程中,为了针对浪涌情况和非浪涌情况分别对功率管进行控制,可以设置相应的检测器件对输出电压进行检测,以根据检测到的浪涌情况生成相应的高电平信号,并且,考虑到浪涌的持续时间,还会设置相应的延时器件基于高电平信号进行延时处理,生成相应的低电平信号,从而根据高电平信号和低电平信号对功率管进行对应的控制,以根据电压浪涌的实际情况对功率管进行实时地控制,提高了功率管的控制效率和准确性。

22、可选地,所述检测模块还包括:控制器件;

23、所述检测器件和所述延时器件通过所述控制器件与所述功率管连接,所述控制器件用于接收所述检测器件或所述延时器件发送的所述浪涌信号,并基于所述浪涌信号控制所述功率管开启或关断。

24、在上述实现过程中,为了实现对功率管的控制,还可以设置相应的控制器件,以根据接收的检测器件与延时器件中发送的实时的浪涌信号,开启或关断功率管,有效地提高了功率管的控制效率。

25、可选地,若所述控制器件接收所述高电平信号,则所述控制器件关断所述功率管,以断开所述第一浪涌通路,并断开基于所述功率管形成的所述寄生模块对应的所述第二浪涌通路;

26、若所述控制器件接收所述低电平信号,则所述控制器件开启所述功率管。

27、在上述实现过程中,控制器件接收表征浪涌情况的高电平信号时,则关断功率管,以断开第一浪涌通路,从而断开基于功率管形成的寄生模块对应的第二浪涌通路,即断开芯片内部形成的两条浪涌通路,以减少芯片内部的浪涌,实现对芯片的保护作用。并且,为了使功率管能够正常使用,控制器件接收表征非浪涌情况的低电平信号时,还能够实时地开启功率管,以根据电压浪涌的实际情况对功率管进行自动控制,在正常工作的前提下有效地减少芯片内部的浪涌情况。

28、可选地,其中,所述功率管的电压数量级基于所述输入电压的工作情况设置。

29、在上述实现过程中,考虑到输入电压的不稳定因素,因此,可以根据输入电压的工作情况,设置相应的电压数量级的功率管,以增加功率管在电压不稳定情况下的工作稳定性。

30、第二方面,本技术实施例还提供了一种控制电路,所述控制电路包括:上述第一方面中任一项所述的抗浪涌电路、电容模块以及负载模块;

31、所述抗浪涌电路与所述电容模块和所述负载模块连接;

32、若所述抗浪涌电路的输入电压产生浪涌情况,基于所述电容模块形成第三浪涌通路,以根据所述浪涌情况进行泄放;

33、所述抗浪涌电路用于为所述负载模块提供工作电能。

34、在上述实现过程中,在输入电压产生浪涌情况时,抗浪涌电路中两条浪涌通路为无法触发的断路情况,因此,由芯片外部的电容模块形成相应的第三浪涌通路对浪涌进行泄放,并由抗浪涌电路为负载模块提供正常工作的相关电能,在正常工作的情况下,能够提高芯片内部器件的抗浪涌效果,减少芯片被烧毁的不利情况。

35、第三方面,本技术实施例还提供了一种抗浪涌方法,所述方法应用于上述第一方面中任一项所述的抗浪涌电路,所述抗浪涌电路包括输入模块、功率管、检测模块和基于所述功率管形成的寄生模块;其中,基于所述功率管形成泄放浪涌的第一浪涌通路,基于所述寄生模块形成泄放浪涌的第二浪涌通路;所述输入模块与所述检测模块连接;所述检测模块与所述功率管连接;所述方法包括:

36、通过所述输入模块为所述抗浪涌电路提供输入电压;

37、通过所述检测模块对所述输入电压的浪涌进行检测,生成控制所述功率管的浪涌信号;

38、其中,若所述功率管被关断,则所述第一浪涌通路和所述第二浪涌通路断路。

39、在上述实现过程中,通过设置检测模块对输入模块中输入的输入电压的浪涌情况进行检测,以根据检测得到的浪涌信号对功率管进行控制,能够在产生浪涌时实时地关断功率管,从而断开芯片内部泄放浪涌的两条浪涌通路,减少浪涌时芯片内部各器件的工作功率,以减少各个器件超功率过载导致的击穿等情况,从而减少芯片被烧毁的不利情况。

40、综上所述,本技术实施例提供了一种抗浪涌电路、控制电路及抗浪涌方法,通过对电压的浪涌情况进行检测,并根据检测得到的浪涌信号对功率管进行控制,能够在浪涌时关断功率管,以断开芯片内部泄放浪涌的两条浪涌通路,减少芯片被烧毁的不利情况。

本文地址:https://www.jishuxx.com/zhuanli/20241021/317756.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

电机组件和加工方法与流程

下一篇

返回列表