提高硬盘抗浪涌能力的方法及相应的集成芯片与流程

- 国知局

- 2024-07-31 18:25:54

本发明主要涉及到存储硬盘的,更确切的说,涉及到了可提高硬盘抗浪涌能力的方法及相应的可提高硬盘抗浪涌能力的集成芯片。

背景技术:

1、传统硬盘热插拔设计存在诸多缺点。硬盘的主板热插入到系统后,产生的浪涌电压无法得到抑制,这种瞬时高电压、高电流会直接冲击到相关电子元器件,造成硬盘对接的相关元器件的当场损毁或降低元器件的可用寿命。由于硬盘的主板存在板级电容或存在着线路寄生电容,存储系统在插入硬盘之后,对接硬盘的存储系统需对硬盘及其主板供电且各类电容存在充电行为,这会瞬态拉低系统电压,硬盘及系统双双受损。关于如何提高硬盘抗浪涌能力,是业界亟待解决的严峻问题。

技术实现思路

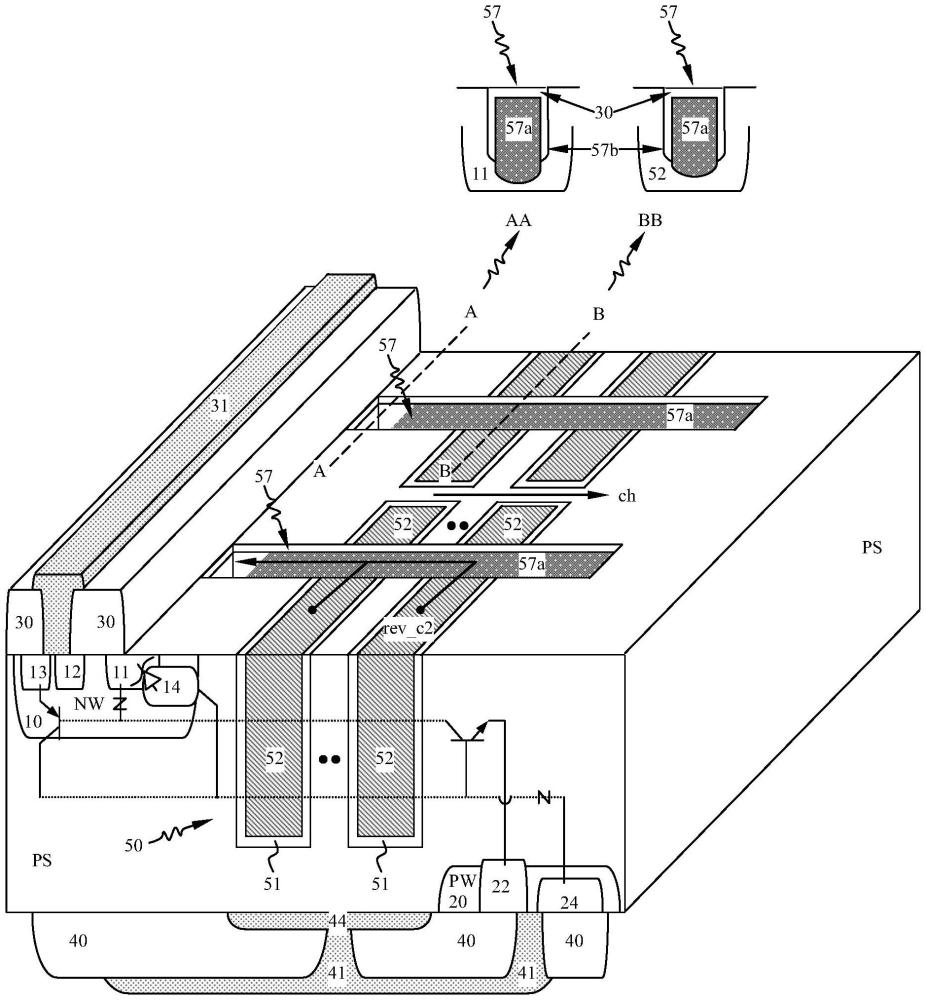

1、本技术涉及一种集成芯片(或称集成芯片结构),其特征在于,包括:

2、开设在一个第一导电类型的衬底正面的具有多个沟槽的沟槽集群,每个沟槽的内壁均设置有绝缘层及每个沟槽的内部均填充有导电材料;

3、植入在衬底正面的第二导电类型的第一阱区,植入在衬底背面的第一导电类型的第二阱区,第一阱区和第二阱区分别位于沟槽集群的相对侧;

4、植入在第一阱区的第二导电类型的第一掺杂区、重掺杂区以及第一导电类型的第三掺杂区、联结区,其中第一掺杂区和各沟槽内的导电材料具有相同的电势;

5、植入在第二阱区的第二导电类型的第二掺杂区和第一导电类型的第四掺杂区;

6、设置在衬底背面的并和第二、第四掺杂区共电势的一个导电层;

7、连接至重掺杂区、第三掺杂区的浪涌信号在使第一掺杂区与联结区之间的结点反向击穿的条件下,第一、第二掺杂区与衬底之间的一个双极晶体管以及第三、第四掺杂区与第一阱区之间的另一双极晶体管被触发导通而泄放所述浪涌信号;

8、各沟槽内的导电材料的存储电荷之等效电压用于夹断处于反向击穿状态下的所述结点流向衬底的电流通道。

9、上述的集成芯片:还包括覆盖在衬底正面的顶部介质层和覆盖在衬底背面的底部介质层;一个用于承接所述浪涌信号的顶部电极层覆盖在顶部介质层上,顶部电极层穿过设于顶部介质层的通孔而分别接触重掺杂区和第三掺杂区;

10、一个用于连接到参考地的底部电极层覆盖在底部介质层上,底部电极层穿过设于底部介质层的通孔而分别接触第二、第四掺杂区和导电层。

11、上述的集成芯片:还包括一个覆盖在顶部介质层上的互联电极层,互联电极层穿过设于顶部介质层的通孔而分别接触第一掺杂区、各沟槽内的导电材料,从而将第一掺杂区和各沟槽内的导电材料电性连接起来。

12、上述的集成芯片:还包括开设在衬底正面的横跨各沟槽并延伸到第一掺杂区的一个或多个槽体,每个槽体内壁衬垫附着有隔离层及每个槽体的内部填充有导体材料;

13、槽体在与沟槽相交的交叉位置、与第一掺杂区接触的部分位置开设有接触孔,以便每个槽体内的导体材料分别电性连接到沟槽内的导电材料、第一掺杂区。

14、上述的集成芯片:还包括植入在衬底背面的并介于所述沟槽的底部与所述导电层之间的一个或多个掩埋区,掩埋区为第二导电类型(有时允许为第一导电类型),掩埋区与所述导电层间隔开或直接触及所述导电层。

15、上述的集成芯片:在衬底的位于多个所述沟槽之间的位置处预留有让一对双极晶体管的电流流通的沟道区域,沟道区域引导流过一对双极晶体管的电流从沟槽集群的一侧穿过沟槽集群而横向流向沟槽集群的相对另一侧。

16、上述的集成芯片:衬底的位于沟槽集群中最邻近第一阱区的一个沟槽与第一阱区之间的局部区域之电流通道被所述等效电压截断;联结区在第一阱区的轮廓设成与衬底正面的表层间隔开;或者联结区在第一阱区的轮廓设置成触及到衬底正面的表层。

17、上述的集成芯片:衬底位于沟槽集群中最邻近第一阱区的沟槽与第一阱区间的局部区域之电流通道被等效电压截断;局部区域交替植入第一导电类型的第一类屏蔽区和第二导电类型的第二类屏蔽区,第一和第二类屏蔽区在局部区域抵达衬底正面的表层。

18、上述的集成芯片:在衬底的位于多个所述沟槽之间的位置处所预留的让一对双极晶体管的电流流通的沟道区域;基于电流通道被等效电压截断的条件,第一和第二类屏蔽区在所述等效电压的作用下相互耗尽,以锁闭多个沟槽间的沟道区域,从而让一对双极晶体管的电流流通的实际渠道从最初的沟道区域下移到沟槽的底部的衬底区域。

19、本技术涉及提高硬盘抗浪涌能力的方法,使用集成芯片吸收灌入至硬盘中受保护的线路上的浪涌信号(surge voltage/current):集成芯片(或集成芯片结构)包括:

20、开设在一个第一导电类型的衬底正面的具有多个沟槽的沟槽集群,每个沟槽的内壁均设置有绝缘层及每个沟槽的内部均填充有导电材料;

21、植入在衬底正面的第二导电类型的第一阱区,植入在衬底背面的第一导电类型的第二阱区,第一阱区和第二阱区分别位于沟槽集群的相对侧;

22、植入在第一阱区的第二导电类型的第一掺杂区、重掺杂区以及第一导电类型的第三掺杂区、联结区,其中第一掺杂区和各沟槽内的导电材料具有相同的电势;

23、植入在第二阱区的第二导电类型的第二掺杂区和第一导电类型的第四掺杂区;

24、设置在衬底背面的并和第二、第四掺杂区共电势的一个导电层;

25、施加于重掺杂区、第三掺杂区的浪涌信号在使第一掺杂区与联结区之间的结点反向击穿的条件下,第一、第二掺杂区与衬底之间的一个双极晶体管以及第三、第四掺杂区与第一阱区之间的另一个双极晶体管被触发导通而泄放所述浪涌信号;

26、各沟槽内的导电材料的存储电荷之等效电压用于夹断处于反向击穿条件下的所述结点流向衬底的电流通道;所述方法包括:

27、将硬盘中受保护的线路上所灌入的浪涌信号引导至为沟槽集群与导电层之间的电容充电,以便在各沟槽内的导电材料处形成存储电荷;

28、在利用被触发导通的一对双极晶体管泄放所述浪涌信号的过程中,使用电容处的存储电荷反向放电、耗尽所述联结区,将所述结点处的所述电流通道锁死。

29、上述的方法:集成芯片包括覆盖在衬底正面的顶部介质层和覆盖在衬底背面的底部介质层;承接浪涌信号的顶部电极层覆盖在顶部介质层上,顶部电极层穿过顶部介质层的通孔而接触重掺杂区和第三掺杂区;连接参考地的底部电极层覆盖在底部介质层上,底部电极层穿过设于底部介质层的通孔而接触第二、第四掺杂区和导电层。

30、上述的方法:集成芯片还包括一个覆盖在顶部介质层上的互联电极层,互联电极层穿过设于顶部介质层的通孔而分别接触第一掺杂区、各沟槽内的导电材料,从而将第一掺杂区和各沟槽内的导电材料电性连接起来。

31、上述的方法:所述集成芯片还包括开设在衬底正面的横跨各沟槽并延伸到第一掺杂区的一个或多个槽体,每个槽体内壁均衬垫附着有隔离层及每个槽体的内部均填充有导体材料;槽体在与沟槽相交的交叉位置、与第一掺杂区接触的部分位置开设有接触孔,以便每个槽体内的导体材料分别电性连接到沟槽内的导电材料、第一掺杂区。

32、上述的方法:所述集成芯片还包括植入在衬底背面的并介于沟槽的底部与导电层之间的一个或多个掩埋区,掩埋区为第二导电类型(有时允许第一导电类型),掩埋区与所述导电层间隔开或直接触及所述导电层。

33、上述的方法:在所述集成芯片当中,在衬底的位于多个所述沟槽之间的位置处预留有让一对双极晶体管的电流流通的沟道区域,沟道区域引导流过一对双极晶体管的电流从沟槽集群的一侧穿过沟槽集群而横向流向沟槽集群的相对另一侧。

34、上述的方法:在所述集成芯片当中,衬底的位于沟槽集群中最邻近第一阱区的沟槽与第一阱区之间的局部区域之电流通道被等效电压截断;联结区在第一阱区的轮廓设成与衬底正面的表层间隔开;或联结区在第一阱区的轮廓设置成触及衬底正面的表层。

35、上述的方法:在所述集成芯片当中,衬底的位于沟槽集群中最邻近第一阱区的一个沟槽与第一阱区之间的局部区域之电流通道被所述等效电压截断;

36、所述局部区域交替植入有第一导电类型的第一类屏蔽区和第二导电类型的第二类屏蔽区,第一和第二类屏蔽区在所述局部区域处向上抵达至衬底正面的表层。

37、上述的方法:在所述集成芯片当中,在衬底的位于多个所述沟槽之间的位置处所预留的让一对双极晶体管的电流流通的沟道区域;

38、基于所述电流通道被所述等效电压截断的条件,第一和第二类屏蔽区在所述等效电压的作用下相互耗尽,以锁闭多个沟槽间的沟道区域,从而让一对双极晶体管的电流流通的实际渠道从最初的所述沟道区域下移到所述沟槽的底部的衬底区域。

39、本技术涉及一种集成芯片(或称集成芯片结构),其特征在于,包括:

40、开设在一个p型衬底正面的具有多个沟槽(trench)的沟槽集群,每个沟槽的内壁均设置有绝缘层及每个沟槽的内部均填充有导电材料;

41、位于衬底正面的n型第一阱区,位于衬底背面的p型第二阱区,第一阱区和第二阱区分别位于沟槽集群(trench cluster)的相对侧;

42、位于第一阱区的n型第一掺杂区、重掺杂区及p型第三掺杂区、联结区,第一掺杂区和各沟槽内的导电材料具有相同的电势;

43、位于第二阱区的n型第二掺杂区、p型第四掺杂区;

44、设置在衬底背面的并和第二、第四掺杂区共电势的一个导电层;

45、施加于重掺杂区、第三掺杂区的浪涌信号在使第一掺杂区与联结区之间的结点反向击穿的条件下,第一、第二掺杂区与衬底之间的第一双极晶体管及第三、第四掺杂区与第一阱区之间的第二双极晶体管被触发导通而泄放浪涌信号(surge voltage/current);

46、各沟槽内的导电材料的存储电荷之等效电压用于夹断处于(或进入)反向击穿状态下的所述结点流向衬底的电流通道。

47、本技术的优势之一:作为经常热插拔的硬盘而言,硬盘中受保护的线路如金属外壳或电子元器件焊点或插拔端子或板载布线或携带寄生谐振电路的电子线路等,存在较大概率的浪涌电压或浪涌电流,本技术在面对浪涌信号时能触发集成芯片产生浪涌信号泄放路径而释放浪涌或卸掉浪涌。可防止硬盘数据丢失和避免硬盘的电子线路损坏。集成芯片的物理结构不仅仅能够耐受低压也还兼顾性的耐受极高压,基于电流通道锁存,集成芯片能够轻松的应对被施加的极高电压水准而不被大电流烧毁,这意味着,除表现出纳秒或毫秒级的浪涌自身被抵御之外,浪涌所混频而携带的低频脉动电压成分也被抵御。

48、本技术的优势之二:触发集成芯片导通而形成泄放路径的结点击穿处,其仅仅只是在触发阶段被击穿而引流,引流是基于引导双极晶体管被触发导通,结点自身在完成引流任务之后并不承担大电流,保障了结点的各相关功能模块不会因浪涌而损毁。这种模式下能够应对重复发生而又难以预料的无处不在的浪涌信号。如果结点及结点各相关功能模块在某单次功率极大的浪涌冲击下被完全损毁或部分损坏,那么后续再次发生的浪涌就无法再继续触发集成芯片的浪涌泄放功能,受到集成芯片保护的线路将失去保障。

49、本技术的优势之三:集成芯片基于使用大泄放电流的模式来抑制浪涌,具体而言是使用一对双极晶体管卸压,容易理解,双极晶体管对组合成双电流泄放路径,优点是能更快捷的抵消浪涌的大功率,但是双极晶体管对之间也存在着电流的失配问题,本技术基于解决双极晶体管对的电流失配、以及失配电流之电流差大量涌入结点之疑虑。和前文所言单次功率极大的浪涌冲击所造成的结点损坏不同,电流失配是两个双极晶体管之间的电流差异过大而被迫将差额电流挤入串并联的结点二极管位置,以至于损坏结点。

本文地址:https://www.jishuxx.com/zhuanli/20240731/179132.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表