多位触发器及多位触发器的方法与流程

- 国知局

- 2024-10-21 14:58:22

本公开涉及半导体装置的领域,并且更具体地,涉及半导体单元架构(诸如,用于标准单元库的多位触发器)。

背景技术:

1、持续需要具有降低的功耗和减小的尺寸的片上系统(soc)。时钟功耗是同步soc设计中的问题。多位库套件是一种低功率解决方案,其可用于基于时钟树的设计中以降低时序单元的内部功耗并优化触发器电路的时钟负载。时钟反相器共享可辅助减小触发器电路的电容。扫描链可连接在时序单元内部,以优化触发器电路的扫描链路径中的保持缓冲器插入。然而,现有方法和技术没有提供可使用超低功率触发器位进行操作的低功率多位触发器、如何使用超低功率触发器位在低功率多位触发器中创建异步复位/置位版本、以及如何以高效地使用功率的方式和在紧凑区域中连接多位解决方案内的扫描链。

技术实现思路

1、一个或多个示例实施例涉及用于标准单元库的多位触发器的设计和配置。

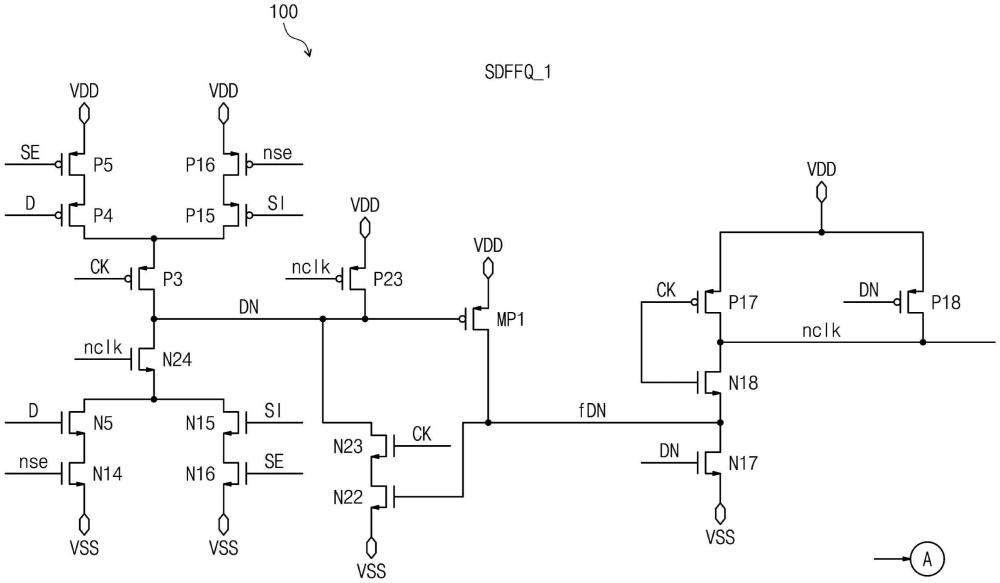

2、一个或多个示例实施例涉及基于高度优化的低功率位单元的电路,该电路具有内部扫描链拼接和真单相时钟设计,而对扫描链连接没有任何惩罚。多位电路为2位单元提供改进的功率增益和面积节省。提出的电路可使用触发器的基于交叉耦合传输门的拓扑,而不对性能造成任何损害。电路拓扑可跨任何位长度扩展,并且与技术节点无关。

3、一个或多个示例实施例还提供具有触发器之间的共享时钟网(而不使用导致各个触发器之间没有共享晶体管的时钟缓冲器或反相器)的真单相时钟电路,其中共享时钟网提供改进的功率优化。

4、一个或多个示例实施例提供被专门布置为形成具有减少的晶体管计数的时序逻辑电路并且在输出引脚上提供异步置位/复位的一组晶体管。

5、根据示例实施例,一种多位触发器包括:第一级一位触发器;以及第二级一位触发器,其中,第一级一位触发器和第二级一位触发器被配置为共享公共时钟信号。第一级一位触发器和第二级一位触发器被配置为以顺序方式使用单元间扫描输入传递功能,第一级一位触发器还被配置为基于在第一级一位触发器的输入端口处提供的扫描输入信号来提供扫描输出信号,并且第二级一位触发器还被配置为基于在第二级一位触发器的输入端口处提供的扫描输出信号来提供扫描最终输出信号。

6、根据示例实施例,一种多位触发器包括:第一级一位触发器;至少一个中间级一位触发器;以及最末级一位触发器,其中,第一级一位触发器、所述至少一个中间级一位触发器和最末级一位触发器被配置为共享公共时钟信号。第一级一位触发器、所述至少一个中间级一位触发器和最末级一位触发器被配置为以顺序方式使用单元间扫描输入传递功能,第一级一位触发器被配置为基于在第一级一位触发器的输入端口处提供的扫描输入信号来提供扫描输出信号,所述至少一个中间级一位触发器被配置为基于扫描输出信号来提供扫描中间输出信号,并且最末级一位触发器被配置为基于扫描中间输出信号来提供扫描最终输出信号。

7、根据示例实施例,一种多位触发器的方法包括:设置第一级一位触发器和第二级一位触发器,其中,第一级一位触发器和第二级一位触发器共享公共时钟信号,并且其中,第一级一位触发器和第二级一位触发器以顺序方式使用单元间扫描输入传递功能;基于提供给第一级一位触发器的输入端口的扫描输入信号来生成扫描输出信号;以及基于扫描输出信号来生成扫描最终输出信号。

8、根据示例实施例,一种多位触发器的方法包括:设置第一级一位触发器、至少一个中间级一位触发器和最末级一位触发器,其中,第一级一位触发器、所述至少一个中间级一位触发器和最末级一位触发器共享公共时钟信号,并且其中,第一级一位触发器、所述至少一个中间级一位触发器和最末级一位触发器以顺序方式使用单元间扫描输入传递功能;基于提供给第一级一位触发器的输入端口的扫描输入信号来生成扫描输出信号;基于扫描输出信号来生成扫描中间输出信号;以及基于扫描中间输出信号来生成扫描最终输出信号。

技术特征:1.一种多位触发器,包括:

2.根据权利要求1所述的多位触发器,其中,第一级一位触发器还被配置为:

3.根据权利要求1所述的多位触发器,其中,第二级一位触发器被配置为:

4.根据权利要求1所述的多位触发器,其中,第一级一位触发器包括:

5.根据权利要求4所述的多位触发器,其中,混合主锁存器包括:反相时钟生成电路,被配置为提供正有效异步复位功能,并且

6.根据权利要求4所述的多位触发器,其中,混合主锁存器包括:反相时钟生成电路,被配置为提供扫描和异步功能,并且

7.根据权利要求1所述的多位触发器,其中,第二级一位触发器包括:

8.根据权利要求7所述的多位触发器,其中,混合主锁存器包括:反相时钟生成电路,被配置为提供正有效异步复位功能,并且

9.根据权利要求7所述的多位触发器,其中,混合主锁存器包括:反相时钟生成电路,被配置为提供扫描和异步功能,并且

10.一种多位触发器,包括:

11.根据权利要求10所述的多位触发器,其中,第一级一位触发器包括:

12.根据权利要求11所述的多位触发器,其中,混合主锁存器包括:反相时钟生成电路,被配置为提供正有效异步复位功能,并且

13.根据权利要求11所述的多位触发器,其中,混合主锁存器包括:反相时钟生成电路,被配置为提供扫描和异步功能,并且

14.根据权利要求10所述的多位触发器,其中,所述至少一个中间级一位触发器包括:

15.根据权利要求14所述的多位触发器,其中,混合主锁存器包括:反相时钟生成电路,被配置为提供正有效异步复位功能,并且

16.根据权利要求14所述的多位触发器,其中,混合主锁存器包括:反相时钟生成电路,被配置为提供扫描和异步功能,并且

17.根据权利要求10所述的多位触发器,其中,最末级一位触发器包括:

18.根据权利要求17所述的多位触发器,其中,混合主锁存器包括:反相时钟生成电路,被配置为提供正有效异步复位功能,并且

19.根据权利要求17所述的多位触发器,其中,混合主锁存器包括:反相时钟生成电路,被配置为提供扫描和异步功能,并且

20.一种多位触发器的方法,包括:

技术总结提供了多位触发器及多位触发器的方法。所述多位触发器包括:第一级一位触发器;以及第二级一位触发器,其中,第一级一位触发器和第二级一位触发器被配置为共享公共时钟信号。第一级一位触发器和第二级一位触发器被配置为以顺序方式使用单元间扫描输入传递功能。第一级一位触发器还被配置为基于在第一级一位触发器的输入端口处提供的扫描输入信号来提供扫描输出信号。第二级一位触发器还被配置为基于在第二级一位触发器的输入端口处提供的扫描输出信号来提供扫描最终输出信号。技术研发人员:米特什·高亚,哈里哈让·那伽拉疆,阿布舍克·高希,契让舒·班特西亚受保护的技术使用者:三星电子株式会社技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/320019.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表