一种针对FPGA块RAM抗单粒子多位翻转的加固系统

- 国知局

- 2024-07-31 19:16:49

本发明涉及航空、航天数据处理,特别涉及一种针对fpga块ram抗单粒子多位翻转的加固系统。

背景技术:

1、fpga具有可编程逻辑运算、高性能、可重构、高集成度的优势,已成为星载数据系统的核心元器件。然而fpga内部存储器、寄存器等资源的逻辑状态,在太空辐射环境下极易发生单粒子效应,导致电路逻辑和功能发生改变,是影响卫星安全和任务的重要因素。

2、随着复杂空间任务对在轨数据处理、运算能力要求越来越高,需要应用更高性能的fpga,比如xilinx的7系列fpga。而90nm以下的此类器件对空间单粒子效应更敏感。由于fpga制作工艺尺寸的几何级变小,如65nm、28nm、16nm工艺,fpga内部的高密集存储部件块ram,发生单粒子翻转事件时,更多的以多位翻转(multi bit upset,简称mbu)为主。mbu是在轨使用高性能fpga需要解决的关键问题。

3、根据研究发现,单次辐射引起的mbu并不是均匀地分布在各个字中,而是具有一定的错误图样。当错误数较多时,mbu将影响上下相邻两个字,以包含“田”字形的图样为主;当错误数较小时,图像主要为“l”和“田”字形,错误图样如图1所示。

技术实现思路

1、现有技术中多位纠错码算法复杂延时高、仅数据交织可靠性不强等的缺点,本发明的目的在于克服现有技术缺陷,提出了一种针对fpga块ram抗单粒子多位翻转的加固方法。

2、为了实现上述目的,本发明提出了一种针对fpga块ram抗单粒子多位翻转的加固系统,用于对星载fpga块ram发生多位翻时进行检测和纠正,所述系统包括:

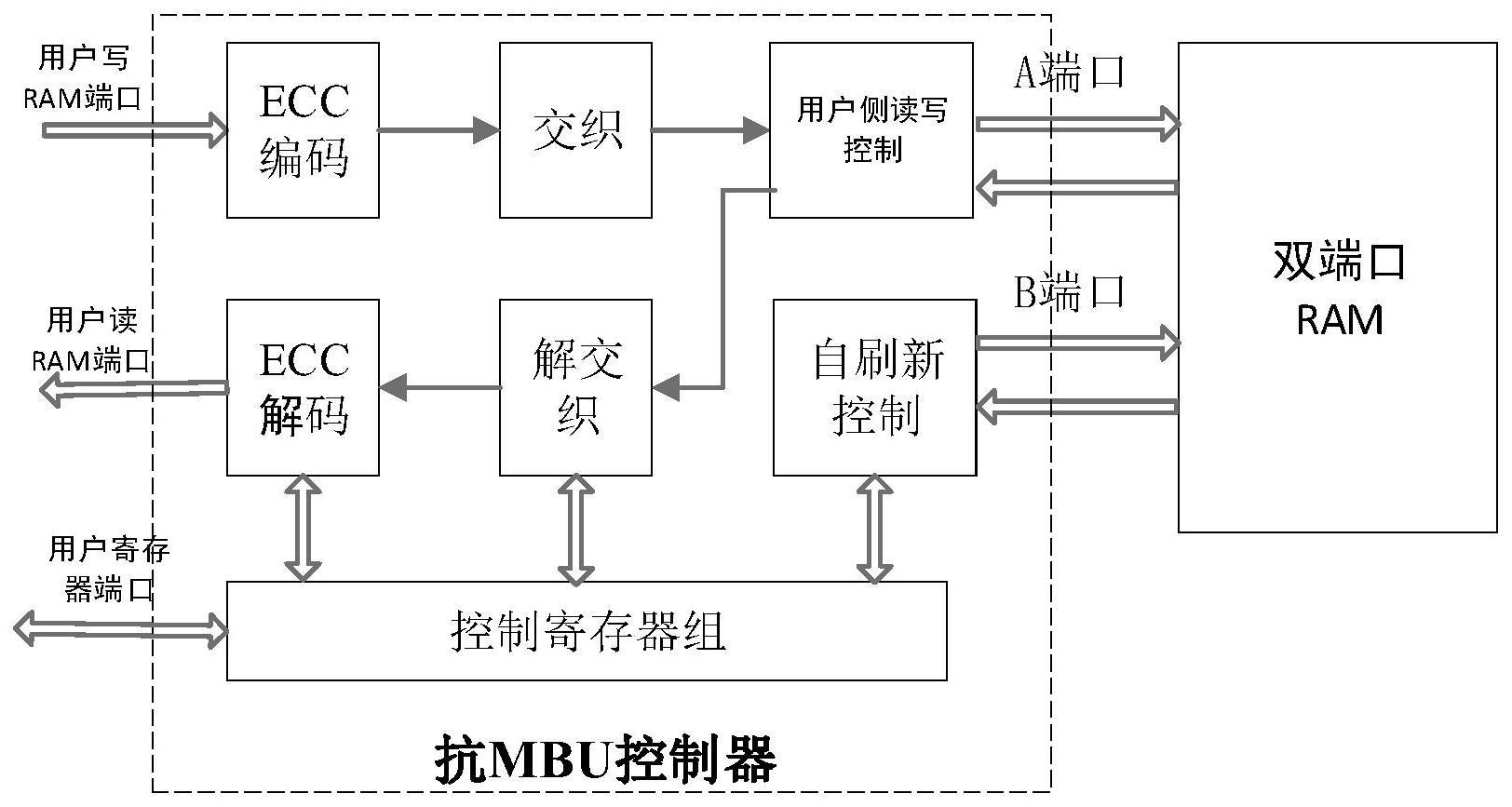

3、若干个抗mbu控制器,每个抗mbu控制器对应一个用户ram模块,所述用户ram模块包括一个或多个fpga块ram;所述抗mbu控制器包括:控制寄存器组、ecc编码模块、交织模块、用户侧读写控制模块、自刷新控制模块、解交织模块和ecc解码模块,其中,

4、所述控制寄存器组,用于抗mbu控制器的控制和状态记录;

5、所述ecc编码模块,用于根据用户待存储的数据位宽进行ecc编码;

6、所述交织模块,用于对ecc编码后的数据进行数据交织;

7、所述用户侧读写控制模块,用于将数据交织后的数据通过块ram的a端口输入块ram进行分块存储,还用于通过块ram的a端口读出数据进入解交织模块;

8、所述自刷新控制模块,用于在块ram空闲时通过块ram的b端口进行自刷新;还用于对块ram进行读写碰撞控制;

9、所述解交织模块,用于实现数据的解交织;

10、所述ecc解码模块,用于对解交织后的数据进行ecc解码。

11、作为上述系统的一种改进,所述块ram的a端口和b端口均为读写端口,a端口的优先级高于b端口。

12、作为上述系统的一种改进,所述控制寄存器组包括:配置寄存器、中断使能寄存器、错误计数寄存器、ecc出错地址寄存器、ecc出错类型寄存器、ecc状态清除寄存器和ecc出错数据寄存器。

13、作为上述系统的一种改进,所述ecc编码模块的处理过程包括:

14、根据用户待存储的数据位宽,8位数据进行汉明码(8,5)编码,16位数据进行汉明码(16,6)编码,32位数据进行汉明码(32,7)编码,64位数据进行汉明码(64,8)编码。

15、作为上述系统的一种改进,所述交织模块的处理过程具体包括:

16、采用4个数据交织存储的方法,将4个ecc编码后的数据按低地址0-3顺序存储,并将地址0和1上的偶数位与地址2和3上的偶数位交换,再通过块ram的a端口写入块ram进行分块存储。

17、作为上述系统的一种改进,所述块ram的分块存储具体包括:

18、对于用户待存储的数据位宽:

19、8位数据经ecc编码和交织处理后的数据使用一个16位宽的块ram存储;

20、16位数据经ecc编码和交织处理后的数据使用一个16位宽的块ram存储分高低地址存储;

21、32位数据经ecc编码和交织处理后的数据使用一个32位宽的块ram存储有效位,使用一个8位宽的块ram存储编码位;

22、64位数据经ecc编码和交织处理后的数据使用两个36位宽的块ram存储。

23、作为上述系统的一种改进,所述块ram的读写操作具体包括:

24、步骤s1)上电后,自动进行块ram初始化,块ram全部写0;

25、步骤s2)当用户读/写使能信号有效时,用户侧读写控制模块根据地址从块ram的a端口读出数据,由解交织模块进行解交织,再由ecc解码模块进行ecc解码;

26、步骤s3)当ecc解码正确,若是读操作,根据地址输出数据;若是写操作,将待写入数据和读出数据合并成一个相应位宽的数据后,由ecc编码模块进行ecc编码,再由交织模块进行数据交织后由用户侧读写控制模块根据地址通过a端口写入数据;

27、步骤s4)当ecc解码错误,根据ecc报错类型,若是一位错,控制寄存器组记录现场,ecc纠错,转至步骤s3);

28、步骤s5)当ecc解码错误,根据ecc报错类型,若是不可纠错,控制寄存器组记录现场,通知用户,根据中断使能寄存器,确定是否对外输出中断。

29、作为上述系统的一种改进,所述自刷新控制模块的自刷新处理过程包括:

30、步骤t1)从块ram的b端口按低地址到高地址的顺序依次读出;

31、步骤t2)由解交织模块进行解交织,再由ecc解码模块进行ecc解码;

32、步骤t3)判断ecc解码是否正确,若ecc解码无错,地址加1,继续读下一地址,并转至步骤t1);

33、若发生一位错误,记录出错类型、错误计数、数据和地址,根据提示的数据错误位置修改数据并通过b端口写回原地址,地址加1,继续读取下一地址,转至步骤t1);

34、若出现多位错误,记录现场,通知用户,并根据控制寄存器组的中断使能寄存器,判断是否对外输出中断。

35、作为上述系统的一种改进,所述自刷新控制模块的读写碰撞控制具体包括:

36、当块ram的a端口和b端口同时对块ram的同一地址读写时,发生读写碰撞,b端口采用读写握手机制,等待a端口操作完成,再进行b端口的操作。

37、与现有技术相比,本发明的优势在于:

38、1、本发明的针对fpga块ram抗单粒子多位翻转的加固系统,将多位翻转转换为多个单位翻,通过组合逻辑实现汉明编译码,具有延时短、逻辑简单的优点;

39、2、本发明的针对fpga块ram抗单粒子多位翻转的加固系统,利用块ram空闲状态进行自刷新,若发生错误自动写回,且进行了ram读写碰撞设计,具有可靠性高的优点;

40、3、本发明的针对fpga块ram抗单粒子多位翻转的加固系统,针对8位、16位、32位和64位数据宽度,根据特点提出分块存储的方法,具有效率高、资源利用率高的优点。

本文地址:https://www.jishuxx.com/zhuanli/20240731/182138.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表