具有时钟同步的光通信收发机的制作方法

- 国知局

- 2024-10-21 15:07:18

本申请涉及集成电路,特别涉及一种具有时钟同步的光通信收发机。

背景技术:

1、在光通信收发机中(特别是相干通信),通常是由两组正交信号xi/xq、yi/yq通道组成。锁相环(pll)生成公用的时钟信号(global clock,或称为pll时钟),然后分别传输给xi、xq、yi、yq四个通道,如图1所示。

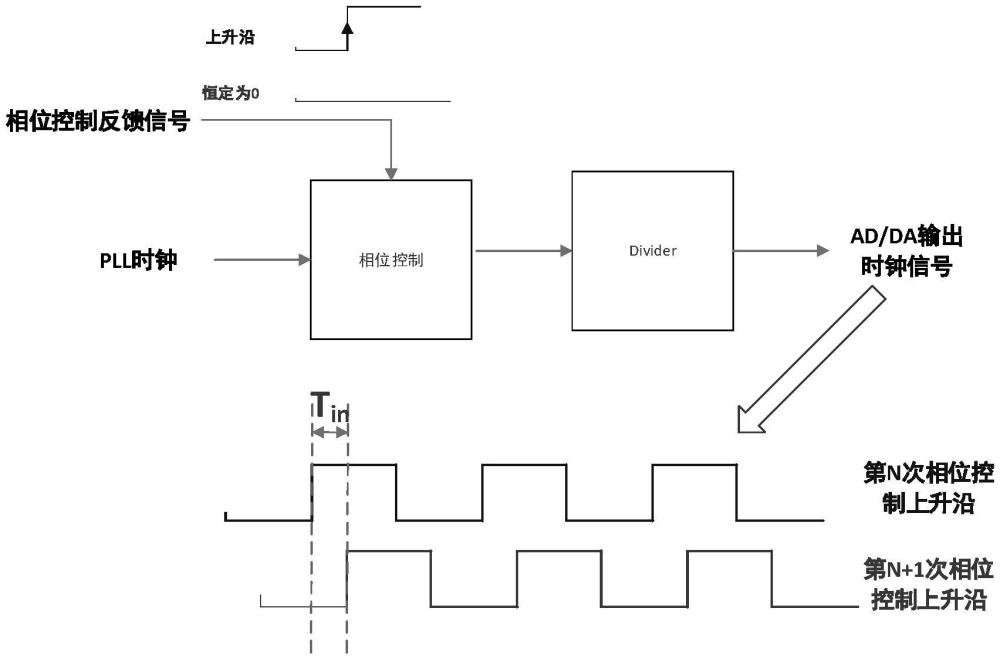

2、在每个通道中,一般由多级级联的分频器(divider)产生模数转换器和数模转换器(ad/da)所需要的多相位时钟,其周期是共用周期的m倍。受分频器自身特性的限制,不能准确地产生第一个上升沿。如图2所示,通道1(例如通道xi)的ad/da的时钟上升沿和通道2(例如通道xq)的差了1个pll时钟周期。若各通道信号没有同步,破坏了xi/xq、yi/yq的正交性,会使系统性能恶化,同时影响后续数字信号处理器(dsp)模块的正常工作。通常光通信系统对不同通道的ad/da信号间隔(skew)有明确的指标要求。因此,必须对不同通道的ad/da时钟信号进行同步。

技术实现思路

1、本申请的目的在于提供一种具有时钟同步的光通信收发机,用于将各个通道的时钟信号的上升沿对齐以同步时钟信号。

2、本申请公开了一种具有时钟同步的光通信收发机,包括:

3、锁相环,所述锁相环产生多路时钟信号,所述多路时钟信号具有第一周期;

4、多个时钟通路,每一个时钟通路各自包括依次耦合的相位控制模块、一个或多个分频器和模数/数模转换模块,每一个时钟通路的相位控制模块分别接收一路时钟信号,每一路时钟信号分别经过所述一个或多个分频器的一级或多级分频并将分频后的时钟信号输出到相应的模数/数模转换模块,所述分频后的时钟信号具有第二周期;以及

5、一个或多个鉴相控制模块,每个鉴相控制模块各自包括鉴相器,每个鉴相器均接收所述多个时钟通路的分频后的时钟信号,并选取一路分频后的时钟信号作为参考时钟信号,将剩余的几路分频后的时钟信号与参考时钟信号进行比较,当某一路分频后的时钟信号的上升沿与参考时钟信号的上升沿未对齐时,所述鉴相器输出检测信号到与该路分频后的时钟信号对应的相位控制模块,所述相位控制模块根据检测信号调整该路时钟信号上升沿推迟一个第一周期,直至该路分频后的时钟信号的上升沿与参考时钟信号的上升沿对齐。

6、在一个优选例中,每个鉴相控制模块还包括:

7、数字控制模块,所述数字控制模块耦合到相应鉴相器,并且,用于接收相应鉴相器输出的检测信号并根据预定时间内的检测信号生成相位反馈控制信号;

8、多路选择器,所述多路选择器的输入端分别耦合到所述鉴相器和所述数字控制模块并用于根据相位控制选择信号输出所述鉴相器输出的检测信号或所述数字控制模块输出的相位反馈控制信号到相应的相位控制模块。

9、在一个优选例中,当所述相位控制选择信号为低电平时,所述多路选择器输出所述鉴相器输出的检测信号到相应的相位控制模块;当所述相位控制选择信号为高电平时,所述多路选择器输出所述数字控制模块输出的相位反馈控制信号到相应的相位控制模块。

10、在一个优选例中,包括:一个鉴相控制模块,所述鉴相控制模块包括鉴相器,所述鉴相器接收所述多个时钟通路的分频后的时钟信号,并选取一路分频后的时钟信号作为参考时钟信号,依次将剩余的几路分频后的时钟信号与参考时钟信号进行比较并依次通过相应的相位控制模块调整该路分频后的时钟信号的上升沿与参考时钟信号的上升沿对齐。

11、在一个优选例中,包括:多个鉴相控制模块,每个鉴相控制模块对应一个时钟通路,每个鉴相器接收所述多个时钟通路的分频后的时钟信号,并选取一路分频后的时钟信号作为参考时钟信号,每个鉴相器将相应的一路分频后的时钟信号与所述参考时钟信号进行比较并分别通过相应的相位控制模块调整该路分频后的时钟信号的上升沿与参考时钟信号的上升沿对齐。

12、在一个优选例中,所述锁相环产生n路时钟信号,所述时钟同步电路包括n个时钟通路和n个鉴相控制模块,其中,n取值为大于等于2的整数。

13、在一个优选例中,所述第二周期是所述第一周期的m倍,其中m取值为大于等于2的整数。

14、在一个优选例中,每路时钟信号的上升沿推迟1至m-1个第一周期。

15、在一个优选例中,每个时钟通路包括k个依次连接的分频器,k取值为大于等于1的整数。

16、本申请实施方式中,可以用于将各个通道的时钟信号的上升沿对齐以同步时钟信号。本申请通过简单的时钟校准,使得iq两路信号实现正交化,省去了用在正交化补偿上的大量资源开销,减小了复杂度。

17、本申请的说明书中记载了大量的技术特征,分布在各个技术方案中,如果要罗列出本申请所有可能的技术特征的组合(即技术方案)的话,会使得说明书过于冗长。为了避免这个问题,本申请上述技术实现要素:中公开的各个技术特征、在下文各个实施方式和例子中公开的各技术特征、以及附图中公开的各个技术特征,都可以自由地互相组合,从而构成各种新的技术方案(这些技术方案均应该视为在本说明书中已经记载),除非这种技术特征的组合在技术上是不可行的。例如,在一个例子中公开了特征a+b+c,在另一个例子中公开了特征a+b+d+e,而特征c和d是起到相同作用的等同技术手段,技术上只要择一使用即可,不可能同时采用,特征e技术上可以与特征c相组合,则,a+b+c+d的方案因技术不可行而应当不被视为已经记载,而a+b+c+e的方案应当视为已经被记载。

技术特征:1.一种具有时钟同步的光通信收发机,其特征在于,包括:

2.根据权利要求1所述的光通信收发机,其特征在于,每个鉴相控制模块还包括:

3.根据权利要求2所述的光通信收发机,其特征在于,当所述相位控制选择信号为低电平时,所述多路选择器输出所述鉴相器输出的检测信号到相应的相位控制模块;当所述相位控制选择信号为高电平时,所述多路选择器输出所述数字控制模块输出的相位反馈控制信号到相应的相位控制模块。

4.根据权利要求2所述的光通信收发机,其特征在于,包括:一个鉴相控制模块,所述鉴相控制模块包括鉴相器,所述鉴相器接收所述多个时钟通路的分频后的时钟信号,并选取一路分频后的时钟信号作为参考时钟信号,依次将剩余的几路分频后的时钟信号与参考时钟信号进行比较并依次通过相应的相位控制模块调整该路分频后的时钟信号的上升沿与参考时钟信号的上升沿对齐。

5.根据权利要求2所述的光通信收发机,其特征在于,包括:多个鉴相控制模块,每个鉴相控制模块对应一个时钟通路,每个鉴相器接收所述多个时钟通路的分频后的时钟信号,并选取一路分频后的时钟信号作为参考时钟信号,每个鉴相器将相应的一路分频后的时钟信号与所述参考时钟信号进行比较并分别通过相应的相位控制模块调整该路分频后的时钟信号的上升沿与参考时钟信号的上升沿对齐。

6.根据权利要求1所述的光通信收发机,其特征在于,所述锁相环产生n路时钟信号,所述时钟同步电路包括n个时钟通路和n个鉴相控制模块,其中,n取值为大于等于2的整数。

7.根据权利要求1所述的光通信收发机,其特征在于,所述第二周期是所述第一周期的m倍,其中m取值为大于等于2的整数。

8.根据权利要求7所述的光通信收发机,其特征在于,每路时钟信号的上升沿推迟1至m-1个第一周期。

9.根据权利要求1所述的光通信收发机,其特征在于,每个时钟通路包括k个依次连接的分频器,k取值为大于等于1的整数。

技术总结本申请涉及集成电路技术领域,公开了一种具有时钟同步的光通信收发机,包括:锁相环,产生多路具有第一周期的时钟信号;多个时钟通路,每个通路各自包括相位控制模块、一个或多个分频器和模数/数模转换模块,相位控制模块分别接收一路时钟信号,每一路时钟信号经过分频得到分频后的具有第二周期的时钟信号;一个或多个鉴相控制模块,每个包括鉴相器,每个鉴相器均接收多个时钟通路的分频后的时钟信号,选取一路分频后的时钟信号作为参考时钟信号,将剩余的几路分频后的时钟信号与参考时钟信号进行比较,当某一路与参考时钟信号未对齐时,鉴相器输出检测信号到对应的相位控制模块,相位控制模块调整该路时钟信号上升沿推迟一个第一周期,直至该路分频后的时钟信号与参考时钟信号对齐。本申请可以将各个通道的时钟信号对齐。技术研发人员:胡新荣,蔡敏卿,姚豫封,李承哲受保护的技术使用者:上海钫铖微电子有限公司技术研发日:技术公布日:2024/10/17本文地址:https://www.jishuxx.com/zhuanli/20241021/320604.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。