一种FPGA间的高速串行通信方法

- 国知局

- 2024-11-19 09:43:44

(一)本发明涉及的是一种高速串行通信方法,尤其涉及一种fpga间的高速串行通信方法,可用于高速串行数据通信,光纤通信,fpga间通信等多种,属于数据通信。

背景技术:

0、(二)背景技术

1、在过去的数十年里,电子信息技术水平以飞快的节奏在进步。现如今大数据时代的步伐已经迈开,生活中数据信息的交流传输也愈加的频繁。这就不仅要求更大的数据存储,对数据的传输速率的要求也同样严格。收发器接口电路广泛的应用于我们的日常生活中,它主要负责通信数据的串并转换,以实现传输的数据的正确性和高效性等。接口电路应用的广泛性和重要性促使针对它的研究变得尤为突出和迅速。

2、随着半导体技术的飞速发展,集成电路技术作为半导体技术的重要方向其发展进步亦是突飞猛进,处理器的性能也是迅速提高。由于通信数据的体积和速率愈来愈大,对于接口延迟的要求更为严格,其中互连延迟成为影响处理器性能关键问题。

3、传统并行形式的数据传输方式有如下几点不足,导致它在现如今的高速传输时代无法满足通信需求:首先,并行形式的传输中,所有数据共享一条总线,这就使得负载的驱动以及多路仲裁的问题尤为突出,传输速率严重受限;其次,并行形式传输数据时需要多条交互连接线,连接线的设计过程中就必须考虑偏差、串扰、噪声及抖动等问题,这使得高速系统的设计难度提高;最后,并行形式传输对布线面积和引脚数目的需求量大,引向片外的连线数目也很大,这就使得芯片内部电路设计的复杂程度提高。

4、综上所述,并行形式传输数据的缺点有布局布线相对复杂、信号传输距离受限以及对硬件的要求巨大等。故而,为了实现数据传输过程中的误码率较低、功耗较低、成本较低、传输速率较高和稳定性较高的要求,高速串行通信技术成为了一种需求广泛的技术。

5、本发明公开了一种fpga间的高速串行通信方法,与传统的并行数据传输相比,实现了误码率较低、功耗较低、成本较低、传输速率较高和稳定性较高的要求。

技术实现思路

0、(三)技术实现要素:

1、本发明的目的在于提供一种结构简单、便于fpga实现、工作速率高、抗干扰能力强、高速的串行通信方法。

2、本发明的目的是这样实现的:

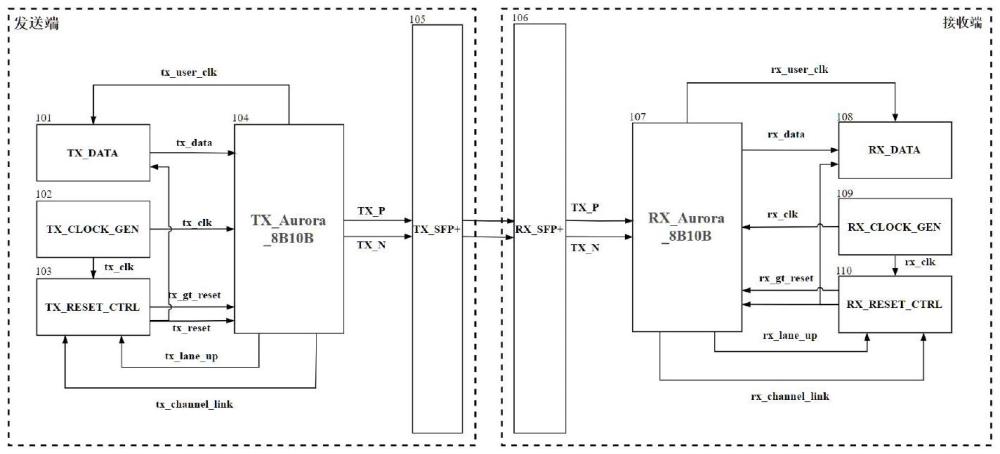

3、一种fpga间的高速串行通信方法。其特征是:它由tx_data模块101、tx_clock_gen模块102、tx_reset_ctrl模块103、tx_aurora_8b10b模块104、tx_sfp+模块105、rx_sfp+模块106、rx_aurora_8b10b模块107、rx_data模块108、rx_clock_gen模块109和rx_reset_ctrl模块110组成。

4、在发送端和接收端中进行数据传输时,首先进行模块的复位。复位分为串行收发器复位和模块复位。在发送端中,复位控制由tx_reset_ctrl模块103控制,在接收端中,复位控制由rx_reset_ctrl模块110控制。

5、tx_reset_ctrl模块103完成发送端模块的复位控制。tx_reset_ctrl模块103的输入信号为tx_clock_gen模块102输出的时钟信号tx_clk、tx_aurora_8b10b模块104输出的tx_channel_up和tx_lane_up信号。tx_reset_ctrl模块103的输出信号为tx_gt_reset和tx_reset信号。tx_reset_ctrl模块103的输出信号tx_reset输出到tx_data模块101和tx_aurora_8b10b模块104;tx_reset_ctrl模块103的输出信号tx_gt_reset输出到tx_aurora_8b10b模块104。tx_reset_ctrl模块103输出tx_gt_reset和tx_reset两路复位信号,复位信号高电平有效。tx_reset_ctrl模块103的控制逻辑如图2所示,上电启动后进入idle状态201,并启动复位计数控制器进入reset状态202,首先计数到tx_gt_reset复位的计数值输出tx_gt_reset为低电平,然后继续计数到tx_reset复位的计数值输出tx_reset为低电平,完成复位。完成复位后进入detect状态203,tx_reset_ctrl模块103实时监测来自tx_aurora_8b10b模块104的状态反馈信号tx_lane_up和tx_channel_link信号,当tx_lane_up和tx_channel_link信号状态正常时保持detect状态203,当tx_lane_up和tx_channel_link信号状态异常时进入idle状态201,重新进行复位。tx_aurora_8b10b模块104接收到来自tx_reset_ctrl模块103的复位信号后,完成复位。

6、tx_clock_gen模块102完成tx_reset_ctrl模块103和tx_aurora_8b10b模块104的时钟信号提供。

7、tx_data模块101完成串行传输数据的打包。tx_data模块101的输入为tx_reset_ctrl模块103提供的复位信号tx_reset和tx_aurora_8b10b模块104提供的时钟信号tx_user_clk。tx_data模块101的输出为打包好的数据tx_data。tx_data为4个字节位宽的数据。

8、tx_aurora_8b10b模块104完从输入数据的串行化、数据封帧和单端信号转差分信号。tx_aurora_8b10b模块104的输入信号为tx_data模块101的输出tx_data、tx_clock_gen模块102输出的tx_clk、tx_reset_ctrl模块103输出的复位信号tx_gt_reset和tx_reset。tx_aurora_8b10b模块104的输出信号为tx_user_clk、tx_lane_up和tx_channel_up信号。

9、tx_sfp+模块105完成电信号转换为光信号。tx_sfp+模块105的输入为tx_aurora_8b10b模块104输出的差分串行信号tx_p和tx_n。tx_sfp+模块105的输出为光信号。

10、rx_sfp+模块106完成光信号转换为电信号。rx_sfp+模块106的输入为tx_sfp+模块105输出的光信号。rx_sfp+模块106的输出信号为差分信号rx_p和rx_n。

11、rx_aurora_8b10b模块107完成串行数据的接收、串行并行化、数据解包。rx_aurora_8b10b模块107的输入信号为rx_clock_gen模块109输出的时钟rx_clk、rx_reset_ctrl模块110输出的复位信号rx_gt_reset和rx_reset。rx_aurora_8b10b模块107的输出信号为rx_data、tx_lane_up和tx_channel_up信号。

12、rx_reset_ctrl模块110完成接收端模块的复位控制。rx_reset_ctrl模块110的输入信号为rx_clock_gen模块109输出的时钟信号rx_clk、rx_aurora_8b10b模块107输出的rx_channel_up和rx_lane_up信号。rx_reset_ctrl模块110的输出信号为rx_gt_reset和rx_reset信号。rx_reset_ctrl模块110的输出信号rx_reset输出到rx_data模块108和rx_aurora_8b10b模块107;rx_reset_ctrl模块110的输出信号rx_gt_reset输出到rx_aurora_8b10b模块107。rx_reset_ctrl模块107输出rx_gt_reset和rx_reset两路复位信号,复位信号高电平有效。tx_reset_ctrl模块110的控制逻辑如图2所示,上电启动后进入idle状态201,并启动复位计数控制器进入reset状态202,首先计数到rx_gt_reset复位的计数值输出rx_gt_reset为低电平,然后继续计数到rx_reset复位的计数值输出rx_reset为低电平,完成复位。完成复位后进入detect状态203,rx_reset_ctrl模块110实时监测来自rx_aurora_8b10b模块107的状态反馈信号rx_lane_up和rx_channel_link信号,当rx_lane_up和rx_channel_link信号状态正常时保持detect状态203,当rx_lane_up和rx_channel_link信号状态异常时进入idle状态201,重新进行复位。rx_aurora_8b10b模块107接收到来自rx_reset_ctrl模块110的复位信号后,完成复位。

13、rx_clock_gen模块109完成rx_reset_ctrl模块110和rx_aurora 8b10b模块107的时钟信号提供。

14、rx_data模块108完成传输数据的接收和解包。rx_data模块108的输入为rx_reset_ctrl模块110提供的复位信号rx_reset和rx_aurora_8b10b模块107提供的时钟信号rx_user_clk。当rx_data模块108接收到有效数据时,fpga间的串行数据发送和接收完成。

本文地址:https://www.jishuxx.com/zhuanli/20241118/329954.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表