一种应用于高速SARADC的电容阵列及控制方法

- 国知局

- 2024-11-21 11:44:43

本发明属于模拟数字转换器,涉及一种分裂式电容阵列架构和提前置位的sar逻辑控制模块。

背景技术:

1、模数转换器(analog-to-digital converter,adc)可以将自然界中的模拟信号转换成数字信号送给数字电路进行处理,是连接芯片和现实世界的接口。其中逐次逼近寄存器型模数转换器(successive approximate analog-to-digital converter,sar adc) 由于具有电路结构较为简单,功耗较低等优势,且速度和精度都能到达中高等,得到了较为广泛的应用。并且由于工艺的进步,sar adc的速度也得到了进一步的提升,高速sar adc也成为目前模数转换器的研究热点。

2、在传统的异步sar adc中,比较器比较完成产生输出信号后需经过多个逻辑门和寄存器才能控制电容阵列进行切换,环路延迟较大。并且当量化位数较高时,电容的权重值也较高,高位电容的电容值会很大,使得建立时间较长,也限制了sar adc的速度。

3、因此为了进一步提升sar adc的速度,需要对sar adc的电容阵列和异步sar逻辑进行优化,减小环路延迟和建立时间。

技术实现思路

1、基于上述分析,本发明提出了一种应用于高速sar adc的电容阵列及控制方法。将电容阵列中的每一位电容都分裂为容值减半的两个电容,减小建立时间。并且sar逻辑使用提前置位的结构,当比较器产生输出信号后只需经过两级反相器的延迟就可以控制电容阵列进行切换,减小环路延迟。

2、本发明的技术方案如下:

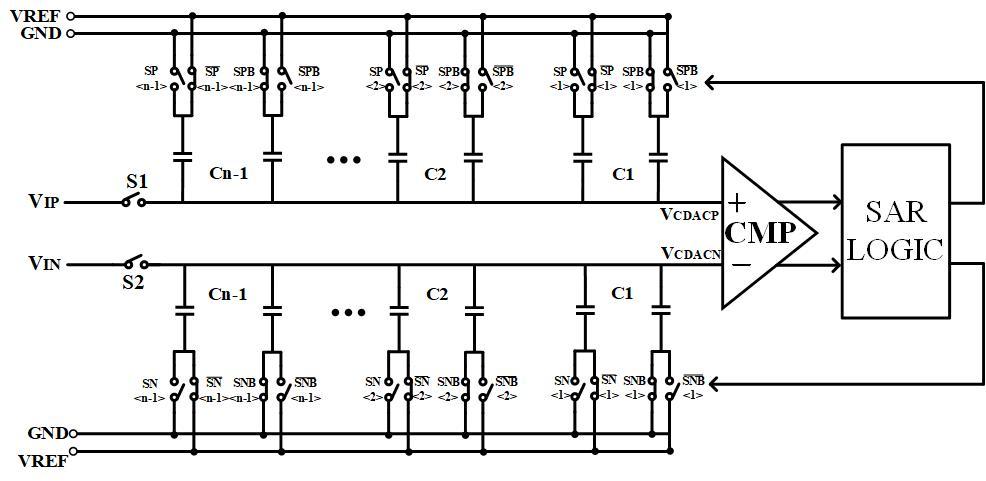

3、一种应用于高速sar adc的电容阵列及控制方法,包括cdac电容阵列模块、比较器cmp模块和控制电容切换的sar逻辑模块。其中,cdac电容阵列的切换使用基于vcm的开关切换策略,并且每一位电容都分裂为两个相同的且容值为原来电容一半的电容,每个电容下极板的控制开关分别由两个反相的信号控制,在量化过程中只切换每一位的两个分裂电容中的一个。其中,sar逻辑模块的输入信号为控制比较过程开始进行的soc信号和控制比较器进行比较的latch信号以及比较器的输出信号op_cmp和on_com,bi信号为预置位信号,输出信号为控制电容阵列各个开关切换的共2n-2个信号。输入信号vip通过采样开关s1连接到p端电容阵列的上极板,输入信号vin通过采样开关s2连接到n端电容阵列的上极板;p端电容阵列的上极板连接到比较器的同相输入端,n端电容阵列的上极板连接到比较器的反相输入端;两端电容阵列的下极板都与由sar逻辑控制的开关相连,并且每个电容与两个由反相信号控制的开关相连,分别控制其接到参考电平vref或者地电平gnd;比较器的输出端与sar逻辑模块相连。

4、在本发明一实施例中,在比较器cmp进行比较前,对sar逻辑模块完成预置位,比较器产生输出信号后立即通过sar逻辑模块并且仅经过两级反相器延时产生开关控制信号来控制4n-4个电平切换开关,使p端和n端电容阵列的下极板迅速连接到对应的电平,即参考电平vref或地电平gnd。

5、在本发明一实施例中,所述p端电容阵列和n端电容阵列的电容阵列结构完全相同,都为二进制权重,权重值为1、2、4……2n-1。

6、本发明还提供了一种基于上述所述的一种应用于高速sar adc的电容阵列及控制方法的具体的电容阵列切换方法,包括以下步骤:

7、步骤1:在采样阶段,开关s1和s2都导通,p端电容阵列的上极板接输入信号vip,n端电容阵列的上极板接输入信号vin。并且此时soc信号和latch信号都为低电平,sar逻辑模块中x处为高电平,a1处为低电平,b1处为高阻状态,y处为高电平,a2处为低电平,b2处为高阻状态,后续部分以此情况类推。sar逻辑模块输出的所有sp<i>和sn<i>信号都为低电平,所有spb<i>和snb<i>信号都为高电平,等效为电容阵列中每一位电容的下极板都接vcm电平,即1/2vref电平。

8、步骤2:采样结束时,开关s1和s2都断开,电容阵列的上极板电压分别保持为vip和vin,送到比较器输入端进行第一次比较。同时soc信号变为高电平,控制比较过程开始,进入量化阶段。latch信号被拉到高电平,使比较器开始工作。sar逻辑模块中x点处电平变为低电平,a1处变为高阻状态仍保持低电平,b1处变为高电平,完成第一次比较的预置位。后续部分保持不变。

9、步骤3:比较器完成第一次比较后,如果输入信号vip大于vin,则比较器输出信号op_cmp变为高电平,on_cmp信号仍为低电平,仅通过两级反相器延时使sp<n-1>信号变为高电平,snb<n-1>信号变为低电平,sn<n-1>信号不变,仍为低电平,spb<n-1>信号不变,仍为高电平,其他开关信号保持不变。且比较结束后latch信号变为低电平,将a1信号拉高并保持,将b1信号拉低并保持,锁存开关控制信号sp<n-1>、snb<n-1>、sn<n-1>、spb<n-1>。并且将b2信号拉高,完成第二次比较的预置位。开关信号控制电容阵列进行切换,使得p端电容阵列最高位电容的两个分裂电容的下极板都接到gnd电平,等效为p端电容阵列最高位电容的下极板接到gnd电平,n端电容阵列最高位电容的两个分裂电容的下极板都接到vref电平,等效为n端电容阵列最高位电容的下极板接到vref电平,其它电容下极板保持不变,完成第一次电容阵列切换。p端电容阵列上极板电压变为vip-1/4vref,n端电容阵列上极板电压变为vin+1/4vref,送到比较器进行第二次比较。如果输入信号vip小于vin,则比较器输出信号on_cmp变为高电平,op_cmp信号仍为低电平,仅通过两级反相器延时使sn<n-1>信号变为高电平,spb<n-1>信号变为低电平,sp<n-1>信号不变,仍为低电平,snb<n-1>信号不变,仍为高电平,其他开关信号保持不变。使得p端电容阵列最高位电容的两个分裂电容的下极板都接到vref电平,等效为p端电容阵列最高位电容的下极板接到vref电平,n端电容阵列最高位电容的两个分裂电容的下极板都接到gnd电平,等效为n端电容阵列最高位电容的下极板接到gnd电平,其它电容下极板保持不变,完成第一次电容阵列切换。p端电容阵列上极板电压vcdacp变为vip+1/4vref,n端电容阵列上极板电压vcdacn变为vin-1/4vref,送到比较器进行第二次比较。

10、步骤4:比较器完成第二次比较后,如果p端电容阵列上极板电压vcdacp大于n端电容阵列上极板电压vcdacn,则第二次比较完成后比较器输出信号op_cmp变为高电平,on_cmp信号仍为低电平,仅通过两级反相器延时使sp<n-2>信号变为高电平,snb<n-2>信号变为低电平,sn<n-2>信号不变,仍为低电平,spb<n-2>信号不变,仍为高电平,后续部分暂不变化。且比较结束后latch信号变为低电平,将a2信号拉高并保持,将b2信号拉低并保持,锁存开关控制信号sp<n-2>、snb<n-2>、sn<n-2>、spb<n-2>。并且将b3信号拉高,完成第三次比较的预置位。开关信号控制电容阵列进行切换,使得p端电容阵列次高位电容的两个分裂电容的下极板都接到gnd电平,等效为p端电容阵列次高位电容的下极板接到gnd电平,n端电容阵列次高位电容的两个分裂电容的下极板都接到vref电平,等效为n端电容阵列次高位电容的下极板接到vref电平,完成第二次电容阵列切换。p端电容阵列上极板电压变为vcdacp-1/8vref,n端电容阵列上极板电压变为vcdacn+1/8vref,送到比较器进行第三次比较。如果p端电容阵列上极板电压vcdacp小于n端电容阵列上极板电压vcdacn,则第二次比较完成后比较器输出信号on_cmp变为高电平,op_cmp信号仍为低电平,仅通过两级反相器延时使sn<n-2>信号变为高电平,spb<n-2>信号变为低电平,sp<n-2>信号不变,仍为低电平,snb<n-2>信号不变,仍为高电平,其他开关信号保持不变。使得p端电容阵列次高位电容的两个分裂电容的下极板都接到vref电平,等效为p端电容阵列次高位电容的下极板接到vref电平,n端电容阵列次高位电容的两个分裂电容的下极板都接到gnd电平,等效为n端电容阵列次高位电容的下极板接到gnd电平,完成第二次电容阵列切换。p端电容阵列上极板电压变为vcdacp+1/8vref,n端电容阵列上极板电压变为vcdacn-1/8vref,送到比较器进行第三次比较。

11、步骤5:重复步骤4中的方式对p端和n端电容阵列中的电容依次进行切换,直到比较器完成n次比较完成整个量化过程。

本文地址:https://www.jishuxx.com/zhuanli/20241120/332689.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表