基于ZYNQ的千兆以太网PHY芯片PTP测试方法与流程

- 国知局

- 2024-11-25 15:17:31

本发明涉及芯片测试,具体涉及一种基于zynq的千兆以太网phy芯片ptp测试方法。

背景技术:

1、千兆以太网技术已成为现代通信领域的主流标准,网络设备大多采用千兆以太网phy芯片进行通信。在网络通信中,时钟同步是至关重要的,ptp全称是precision timeprotocol,即精密时间协议,是一种高精度网络时间同步协议。在使用千兆以太网phy芯片时,确保它正常工作并实现精准的时钟同步对网络稳定性和性能至关重要。其中,phy全称是physical layer,即物理层,千兆以太网phy芯片则是一种用于千兆以太网通信的物理层芯片。

2、许多工业、测试、测量和通信应用都要求高精度的时钟信号以便同步控制信号和捕捉数据等。目前,在部分标准以太网中,可以通过应用精密时间协议ptp,将主时钟的时间信息传播到系统中的多个节点,并且精密时间协议ptp还为这些节点提供了测试方法,以验证时间同步的效果,一种方法是单纯依靠软件来进行控制,另一种方法是软件和fpga混合或软件和asic混合再进行传输。尽管使用这些方法时,结点能基于主时钟来产生时钟输出信号,但这样的信号精度不足以满足系统对极低的时钟抖动的要求。此外,系统的时钟相位对准和时间同步也难以满足严格要求。

3、也就是说,目前采取的这些措施至少包含以下三种问题:

4、1)信号精度不足,难以满足系统对极低的时钟抖动的要求;

5、2)难以做到时钟的相位对准和时间同步;

6、3)测试的准确性和可靠性不足。

技术实现思路

1、针对上述三个问题,本发明的目的是提出一种基于zynq的千兆以太网phy芯片ptp测试方法,通过主从系统的phy芯片和zynq芯片进行时钟同步测试,可以在示波器处进行精准的测试结果显示,也便于分析,有效提升测试的准确性;同时,优化zynq芯片的处理系统和可编程逻辑的结构,以多种专用的高效接口进行对应传输,并在软件驱动程序的控制下利用mac控制器控制多个测试用例,可以有效做到精准的时钟对准和时间同步;此外,还针对最终测试结果进行多角度性能分析,进一步提升测试的可靠性。

2、通过以下技术方案实现的:

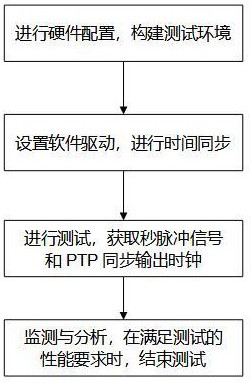

3、一种基于zynq的千兆以太网phy芯片ptp测试方法,该方法包括如下步骤:s1、进行硬件配置:设置主系统和从系统,主系统包括互连的主zynq芯片和主phy芯片,从系统包括互连的从zynq芯片和从phy芯片,主phy芯片分别通过电缆和示波器连接从phy芯片;分别在主zynq芯片内部和从zynq芯片内部构建相同的测试环境,用于集成相同的时钟源并模拟相同的网络条件;s2、设置软件驱动:分别对步骤s1中的主zynq芯片设置第一软件驱动程序和对步骤s1中的从zynq芯片设置第二软件驱动程序,利用第一软件驱动程序控制主phy芯片的第一ptp,同时将主phy芯片与主zynq芯片进行时间同步;利用第二软件驱动程序控制从phy芯片的第二ptp,同时将从phy芯片与从zynq芯片进行时间同步;s3、进行测试:完成步骤s2后,设置多个测试用例并将多个测试用例同时存储在第一软件驱动程序中和第二软件驱动程序中;依次对每个测试用例进行测试,利用示波器获取主zynq芯片在每个测试用例下对应的每个第一秒脉冲信号和每个第一ptp同步输出时钟,利用示波器获取每个从zynq芯片在每个测试用例下对应的每个第二秒脉冲信号和每个第二ptp同步输出时钟;将每个第一秒脉冲信号、每个第一ptp同步输出时钟、每个第二秒脉冲信号和每个第二ptp同步输出时钟作为最终测试结果;s4、监测与分析:对步骤s3中最终测试结果进行延迟、抖动和同步精度的多角度性能分析,判断是否满足测试的性能要求,若满足,则结束测试;若不满足,则重新返回步骤s1中分别在主zynq芯片内部和从zynq芯片内部构建相同的测试环境的步骤进行循环,直至满足测试的性能要求时,结束测试。

4、利用主系统的主phy芯片和主zynq芯片以及从系统的从phy芯片和从zynq芯片进行多个测试用例下的时钟同步测试,可以在示波器处进行精准的测试结果显示,便于分析,有效提升测试的准确性;同时,优化每个zynq芯片的每个处理系统和每个可编程逻辑的结构,在每个软件驱动程序的控制下利用对应的每个mac控制器控制多个测试用例,可以有效做到精准的时钟对准和时间同步;此外,还针对最终测试结果进行多角度性能分析,进一步提升测试的可靠性。

5、优选地,步骤s1中主zynq芯片内部包括第一可编程逻辑和第一处理系统,第一处理系统中设置有第一mac控制器,第一mac控制器用于连接主phy芯片和第一软件驱动程序,还用于控制第一软件驱动程序中的每个测试用例是否进行测试;第一可编程逻辑中设置有第一硬件触发模块和第一ip核,第一ip核分别连接第一处理系统和第一硬件触发模块,第一硬件触发模块用于在第一软件驱动程序进行任意测试用例的测试时控制第一ip核向示波器发射对应的第一秒脉冲信号;从zynq芯片的结构与主zynq芯片的结构相同。

6、优选地,第一ip核为ieee 1588 ip核,第一ip核中包括互连的第一寄存器单元和第一实时时钟单元,第一寄存器单元和第一实时时钟单元均受第一硬件触发模块控制,第一寄存器单元连接第一处理系统,第一实时时钟单元连接示波器。ieee 1588 ip核为高精度的ip核,可以保证测试的准确性。

7、优选地,主zynq芯片内部还包括第一应用处理器模块、第一时间戳单元、第一rgmii接口、第一mio多功能接口、第一中心联接单元和第一状态与控制寄存器;第一mac控制器分别连接第一时间戳单元、第一中心联接单元和第一状态与控制寄存器,第一mac控制器通过第一mio多功能接口连接第一软件驱动程序以及通过第一rgmii接口连接主phy芯片,第一中心联接单元分别连接第一mac控制器、第一mio多功能接口、第一ip核和第一应用处理器模块,第一应用处理器模块用于执行多个测试用例的测试。第一时间戳单元、第一状态与控制寄存器、第一中心联接单元结合第一应用处理器模块,可以让主zynq芯片高效准确的进行每个测试用例的测试。

8、优选地,步骤s2中利用第一软件驱动程序控制主phy芯片的第一ptp时,第一软件驱动程序先通过第一uart接口和第一jtag接口连接到第一处理系统,再通过第一处理系统连接到主phy芯片;步骤s2中利用第二软件驱动程序控制从phy芯片的第二ptp时,第二软件驱动程序先通过第二uart接口和第二jtag接口连接到第二处理系统,再通过第二处理系统连接到从phy芯片。jtag接口便于进行程序方面的调试,uart接口便于快速传输数据,软件驱动程序通过处理系统与phy芯片交互,灵活性高,便于进行精准控制。

9、优选地,步骤s3中,多个测试用例包括同步延迟用例、漂移测量用例、时间戳准确性用例和丢包率验证用例。多个测试用例可以多方面获取同步的精确度和准确性,进而确保整个测试的精度和准确性。

10、优选地,步骤s4中,在完成多角度性能分析后,继续进行符合性验证,检测最终测试结果是否符合ieee1588标准。ieee1588标准是高精密度的标准且具有较高的通用性,符合该标准也保证了测试的准确性和精度。

11、本发明与现有技术相比具有的有益效果是:

12、本发明的技术方案,通过主从系统的phy芯片和zynq芯片进行时钟同步测试,可以在示波器处进行精准的测试结果显示,也便于分析,有效提升测试的准确性;同时,优化zynq芯片的处理系统和可编程逻辑的结构,以多种专用的高效接口进行对应传输,并在软件驱动程序的控制下利用mac控制器控制多个测试用例,可以有效做到精准的时钟对准和时间同步;此外,还设置多种测试用例并针对最终测试结果进行多角度性能分析,进一步提升测试的可靠性。

本文地址:https://www.jishuxx.com/zhuanli/20241125/337146.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表