发光二极管外延片及其制备方法、LED与流程

- 国知局

- 2024-12-06 12:49:47

本发明涉及光电,尤其涉及一种发光二极管外延片及其制备方法、led。

背景技术:

1、目前,以ingan量子阱为有源层的gan基led器件在各领域都有广泛应用,但因缺乏合适的同质外延衬底,gan通常生长在与其有较大晶格失配的蓝宝石、碳化硅或硅衬底上。gan与衬底间的晶格失配无疑会形成大量的位错缺陷,从而影响其外延质量。此外,长波长ingan基led因多量子阱发光层的ingan与gan之间亦存在较大的晶格失配,ingan量子阱会受到来自gan的压应力。不论是位错缺陷还是压应力均会对led器件的性能产生不良影响。因此为了提高长波长ingan基led的发光效率和性能,减小外延层材料所受的应力和降低外延层材料的缺陷密度是十分必要的。

技术实现思路

1、本发明所要解决的技术问题在于,提供一种发光二极管外延片,其能够降低多量子阱发光层材料所受的应力和缺陷密度,显著提高多量子阱发光层的质量,提升多量子阱发光层中的辐射复合效率,从而提高led器件的发光效率。

2、本发明所要解决的技术问题还在于,提供一种发光二极管外延片的制备方法,其工艺简单,能够稳定制得发光效率良好的发光二极管外延片。

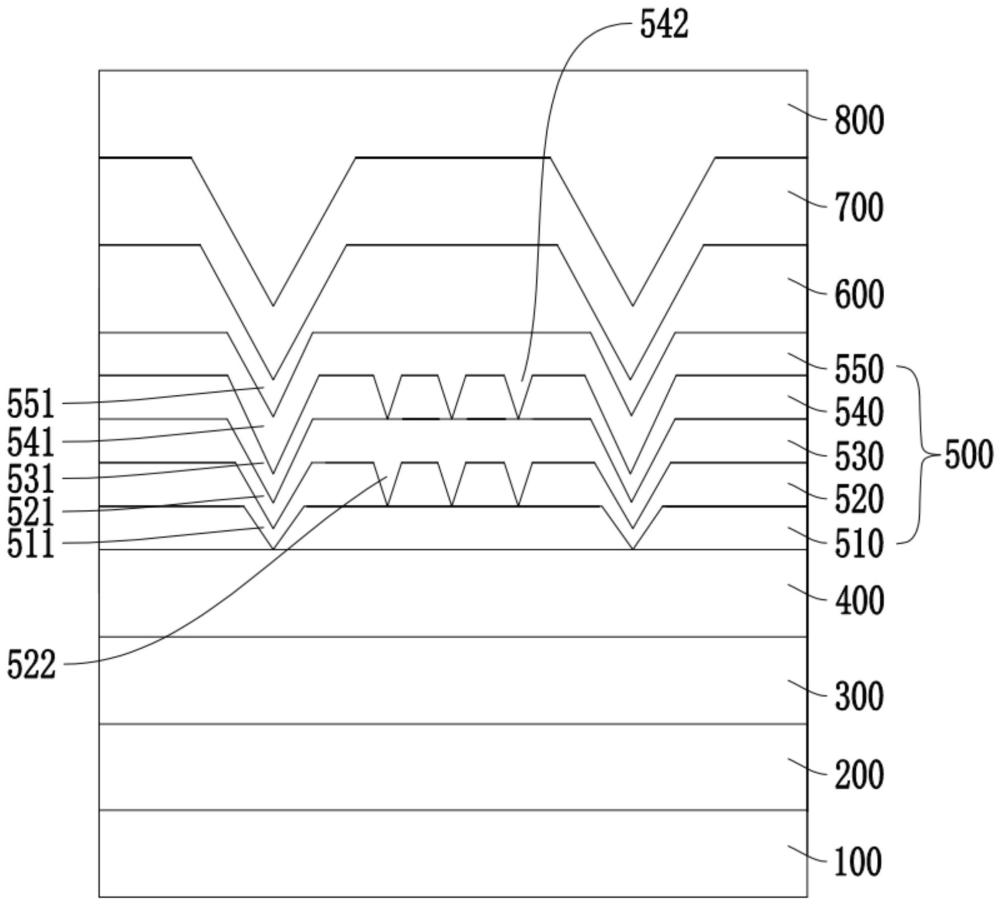

3、为了解决上述技术问题,本发明提供了一种发光二极管外延片,包括衬底,所述衬底上依次设有缓冲层、非掺杂gan层、n型gan层、应力释放层、多量子阱发光层、电子阻挡层、p型gan层;

4、所述应力释放层包括依次层叠的si掺杂多孔gan层、低in组分的多孔ingan/gan超晶格层、低si掺杂gan合并层、高in组分的多孔ingan/gan超晶格层和si掺杂gan合并层。

5、在一些实施方式中,所述si掺杂多孔gan层的厚度为16nm~520nm;

6、所述si掺杂多孔gan层的si掺杂浓度为3.6×1017atoms/cm3~2.8×1019atoms/cm3;

7、所述si掺杂多孔gan层设有贯穿所述si掺杂多孔gan层的第一v型孔洞;

8、所述第一v型孔洞均匀地分布在所述si掺杂多孔gan层中,所述第一v型孔洞的密度为1.2×108个/cm2~5.6×1011个/cm2。

9、在一些实施方式中,所述低in组分的多孔ingan/gan超晶格层包括交替层叠的第一ingan层和第一gan层,周期数为2~5;

10、所述第一ingan层的厚度为1.2nm~5nm;

11、所述第一ingan层的in组分为0.01~0.15;

12、所述第一gan层的si掺杂浓度为1.2×1017atoms/cm3~5.6×1018atoms/cm3;

13、所述第一gan层的厚度为2nm~13.6nm;

14、所述低in组分的多孔ingan/gan超晶格层设有贯穿所述低in组分的多孔ingan/gan超晶格层的第三v型孔洞,且所述第三v型孔洞层叠在所述第一v型孔洞上;

15、所述第三v型孔洞均匀地分布在所述低in组分的多孔ingan/gan超晶格层中,所述第三v型孔洞的密度为1.2×108个/cm2~5.6×1011个/cm2;

16、所述低in组分的多孔ingan/gan超晶格层设有贯穿所述低in组分的多孔ingan/gan超晶格层的第二v型孔洞,所述第二v型孔洞不层叠在所述第一v型孔洞上;

17、所述第二v型孔洞均匀地分布在所述低in组分的多孔ingan/gan超晶格层中,所述第二v型孔洞的密度为2.6×108个/cm2~1.8×1012个/cm2;

18、所述第三v型孔洞的开口尺寸大于所述第二v型孔洞的开口尺寸。

19、在一些实施方式中,所述低si掺杂gan合并层的厚度为10nm~180nm;

20、所述低si掺杂gan合并层的si掺杂浓度为1.2×1017atoms/cm3~5.6×1018atoms/cm3;

21、所述低si掺杂gan合并层完全填充所述第二v型孔洞,且未完全填充所述第三v型孔洞;

22、所述低si掺杂gan合并层设有贯穿所述低si掺杂gan合并层的第五v型孔洞,且所述第五v型孔洞层叠在所述第三v型孔洞上。

23、在一些实施方式中,所述高in组分的多孔ingan/gan超晶格层包括交替层叠的第二ingan层和第二gan层,周期数为2~8;

24、所述第二ingan层的厚度为1.2nm~5nm;

25、所述第二ingan层的in组分为0.03~0.3;

26、所述第二gan层的si掺杂浓度为1.2×1017atoms/cm3~5.6×1018atoms/cm3;

27、所述第二gan层的厚度为2nm~13.6nm;

28、所述高in组分的多孔ingan/gan超晶格层设有贯穿所述高in组分的多孔ingan/gan超晶格层的第六v型孔洞,且所述第六v型孔洞层叠在所述第五v型孔洞上;

29、所述第六v型孔洞均匀地分布在所述高in组分的多孔ingan/gan超晶格层中,所述第六v型孔洞的密度为1.2×108个/cm2~5.6×1011个/cm2;

30、所述高in组分的多孔ingan/gan超晶格层设有贯穿所述高in组分的多孔ingan/gan超晶格层的第四v型孔洞,所述第四v型孔洞不层叠在所述第五v型孔洞上;

31、所述第四v型孔洞均匀地分布在所述高in组分的多孔ingan/gan超晶格层中,所述第四v型孔洞的密度为2.6×108个/cm2~1.8×1012个/cm2;

32、所述第六v型孔洞的开口尺寸大于所述第四v型孔洞的开口尺寸。

33、在一些实施方式中,所述si掺杂gan合并层的厚度为12nm~250nm;

34、所述si掺杂gan合并层的si掺杂浓度为3.6×1017atoms/cm3~2.8×1019atoms/cm3;

35、所述si掺杂gan合并层完全填充所述第四v型孔洞,且未完全填充所述第六v型孔洞;

36、所述si掺杂gan合并层设有贯穿所述si掺杂gan合并层的第七v型孔洞,且所述第七v型孔洞层叠在所述第六v型孔洞上。

37、为解决上述问题,本发明还提供了一种发光二极管外延片的制备方法,包括以下步骤:

38、s1、提供衬底;

39、s2、在所述衬底上依次沉积缓冲层、非掺杂gan层、n型gan层、应力释放层、多量子阱发光层、电子阻挡层、p型gan层;

40、所述应力释放层包括依次层叠的si掺杂多孔gan层、低in组分的多孔ingan/gan超晶格层、低si掺杂gan合并层、高in组分的多孔ingan/gan超晶格层和si掺杂gan合并层。

41、在一些实施方式中,在沉积所述si掺杂多孔gan层之前对外延层材料表面进行第一高温h2气处理,在沉积所述低in组分的多孔ingan/gan超晶格层之前对外延层材料表面进行第二高温h2气处理,在沉积所述高in组分的多孔ingan/gan超晶格层之前对外延层材料表面进行第三高温h2气处理;

42、高温h2气处理包括:

43、步骤一、在反应腔温度为920℃~1200℃、压力为50torr~500torr的条件下,向反应腔中通入h2和n2混合气体并保持3s~180s;

44、步骤二、停止通入h2和n2混合气体;

45、循环所述步骤一和步骤二,完成高温h2气处理。

46、在一些实施方式中,所述第一高温h2气处理的处理时间≥所述第二高温h2气处理的处理时间≥所述第三高温h2气处理的处理时间;

47、所述第一高温h2气处理的h2通入流量≥所述第二高温h2气处理的h2通入流量≥所述第三高温h2气处理的h2通入流量。

48、相应地,本发明还提供了一种led,所述led包括如上文所述的发光二极管外延片,或者包括由上文所述的发光二极管外延片的制备方法所制得的发光二极管外延片。

49、实施本发明,具有如下有益效果:

50、本发明提供的发光二极管外延片中,所述应力释放层包括依次层叠的si掺杂多孔gan层、低in组分的多孔ingan/gan超晶格层、低si掺杂gan合并层、高in组分的多孔ingan/gan超晶格层和si掺杂gan合并层。

51、其中si掺杂多孔gan层、低in组分的多孔ingan/gan超晶格层、高in组分的多孔ingan/gan超晶格层三个子层均为多孔结构,该结构的设计有利于充分释放外延层材料的应力,能够有效减少后续外延层材料受到大的应力而产生缺陷,从而提高多量子阱发光层材料的质量。

52、再者,低in组分的多孔ingan/gan超晶格层、高in组分的多孔ingan/gan超晶格层均为多孔ingan/gan超晶格材料,且in组分存在差异,这种结构设计不仅有利于充分释放外延层材料的应力,而且能够减少为增强空穴注入而牺牲的侧壁量子阱发光面积,有效的增加发光二极管所需要的平台量子阱的发光面积,从而提高发光二极管的发光效率。

53、进一步地,由于所述应力释放层设有特定结构的v型孔洞,致使所述多量子阱发光层中存在v坑,v坑产生于多层结构的应力释放层,并贯穿整个发光单元;量子阱在v坑中生长形成侧壁量子阱,其厚度较平台量子阱薄,禁带宽度更小,在载流子注入有源区时,v坑侧壁位置的量子阱禁带宽度更小,厚度更薄,通过隧穿作用,载流子在v坑侧壁更容易注入,提高量子阱中电子空穴的匹配度,促进接近n面的量子阱发光,以提高ingan基led的发光效率。

54、本发明提供的发光二极管外延片的制备方法中,在沉积si掺杂多孔gan层、低in组分的多孔ingan/gan超晶格层和高in组分的多孔ingan/gan超晶格层之前,均需要对外延层材料表面进行高温h2气处理,经过高温h2气处理的外延层材料表面结晶质量差的材料将被分解,有利于降低外延层材料的缺陷密度提高外延层材料的晶体质量,同时形成凹凸不平的粗糙表面,有利于后续沉积的外延层材料更容易获得尺寸大小相同、分布均匀的大v型孔洞、小v型孔洞,进一步充分释放外延层材料的应力,提高外延层材料的质量。

55、综合以上工艺,采用本发明制备的led芯片能够降低多量子阱发光层材料所受的应力和缺陷密度,显著提高多量子阱发光层的质量,并有效的增强有源区中空穴的注入提高量子阱中电子空穴浓度的匹配度的同时,增加发光二极管所需要的平台量子阱的发光面积,使多量子阱发光层中的辐射复合效率提升,从而提高led芯片的发光效率。

本文地址:https://www.jishuxx.com/zhuanli/20241204/342819.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表