一种金属互连器件的阻挡层制备方法与流程

- 国知局

- 2024-12-06 13:05:59

本申请涉及半导体工艺,尤其涉及一种金属互连器件的阻挡层制备方法。

背景技术:

1、在半导体工艺中的铜后段工艺制造中,通过大马士革互连工艺来填充铜,以降低器件电阻和电容,但是铜的引入可能会产生电迁移(em),影响器件的使用寿命。目前通过在铜界面增加覆盖金属互连线的保护层(cap layer),或者去除污染和提升通孔(via)底部的纯度,或者采用cual和cumn的合金来做阻挡层,以改善电迁移。虽然上述方式可以改善电迁移,但是需要引入额外的步骤或者更换靶材,增加了晶圆制造的成本。

技术实现思路

1、有鉴于此,本申请的目的在于至少提供一种金属互连器件的阻挡层制备方法,通过在金属互连器件的器件层上已蚀刻出沟道的介质层上沉积第一阻挡层,并且第一阻挡层防止后续过度蚀刻,再在对沟道对应的凹槽进行蚀刻来至少去除第一阻挡层,以此来增加沟道的深度,再沉积出第二阻挡层,以得到第一阻挡层与第二阻挡层结合的目标阻挡层,进而通过增加沟道的接触面积以及增加第一阻挡层的厚度来优化金属互连器件的电迁移现象,解决了现有技术中金属互连器件的电迁移性能差的技术问题,达到了提高金属互连器件的电迁移性能的技术效果。

2、本申请主要包括以下几个方面:

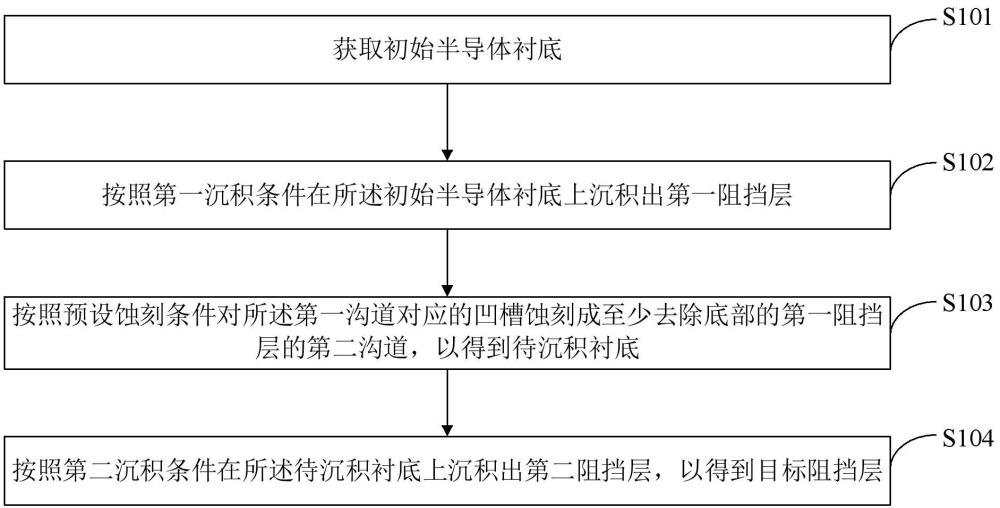

3、第一方面,本申请实施例提供一种金属互连器件的阻挡层制备方法,所述方法包括:获取初始半导体衬底,所述初始半导体衬底包括位于金属互连器件的器件层上的介质层中的第一沟道;按照第一沉积条件在所述初始半导体衬底上沉积出第一阻挡层,所述第一阻挡层覆盖所述初始半导体衬底;按照预设蚀刻条件对所述第一沟道对应的凹槽蚀刻成至少去除底部的第一阻挡层的第二沟道,以得到待沉积衬底;按照第二沉积条件在所述待沉积衬底上沉积出第二阻挡层,以得到覆盖介质层和第二沟道的目标阻挡层;其中,所述第一沉积条件和所述预设蚀刻条件均用于限制所述第二沟道的规格,以提升金属互连器件的电迁移性能。

4、可选地,所述第一沉积条件用于通过限制所述第一阻挡层的厚度来并防止过度蚀刻所述第二沟道,所述预设蚀刻条件用于增加所述第二沟道被蚀刻的介质层以下的部分与第二阻挡层的接触面积。

5、可选地,所述按照第一沉积条件在所述初始半导体衬底上沉积出第一阻挡层,包括:按照所述第一沉积条件在所述初始半导体衬底上沉积出第一材质的粘附层并在所述粘附层上沉积出第二材质的隔离层,以使所述粘附层与所述隔离层作为所述第一阻挡层;其中,所述第一沉积条件用于增加所述粘附层和所述隔离层的厚度。

6、可选地,所述第一沉积条件通过增加沉积时间和/或增加沉积功率来增加所述粘附层和所述隔离层的厚度,所述预设蚀刻条件通过增加蚀刻时间和/或增加蚀刻功率来增加所述接触面积。

7、可选地,所述第二沉积条件用于修复蚀刻所产生的缺陷,所述第二阻挡层的材质与所述隔离层的材质相同。

8、可选地,所述方法还包括:在所述目标阻挡层上沉积预设金属,再进行化学机械抛光处理。

9、可选地,通过以下方式在所述目标阻挡层上沉积预设金属:在所述目标阻挡层上沉积出所述预设金属的初始种子层;在所述初始种子层上沉积所述预设金属并填充所述第二沟道。

10、可选地,所述方法还包括:采集所述金属互连器件的多个参数,所述多个参数包括不同位置的所述目标阻挡层的厚度参数以及蚀刻后的所述第二沟道的规格参数;确定出所述多个参数中的两个预设参数的比值;通过所述比值及对应的预设比值范围,对所述金属互连器件的电迁移性能进行判定。

11、可选地,所述第二沟道包括水平区域,所述第二沟道包括一个或多个,所述目标阻挡层包括位于所述第二沟道中的所述第二阻挡层以及除所述第二阻挡层之外的组合部分,其中,所述多个参数包括位于目标水平面上的所述组合部分的第一厚度、位于所述第二沟道的侧壁的所述组合部分的第二厚度、位于介质层以下的所述第二沟道的深度以及宽度,其中,所述目标水平面包括:一个第二沟道的水平区域,或者,相邻第二沟道之间沉积预设金属的水平区域。

12、可选地,所述预设金属为铜。

13、本申请实施例提供的一种金属互连器件的阻挡层制备方法,方法包括:获取初始半导体衬底,所述初始半导体衬底包括位于金属互连器件的器件层上的介质层中的第一沟道;按照第一沉积条件在所述初始半导体衬底上沉积出第一阻挡层,所述第一阻挡层覆盖所述初始半导体衬底;按照预设蚀刻条件对所述第一沟道对应的凹槽蚀刻成至少去除底部的第一阻挡层的第二沟道,以得到待沉积衬底;按照第二沉积条件在所述待沉积衬底上沉积出第二阻挡层,以得到覆盖介质层和第二沟道的目标阻挡层;其中,所述第一沉积条件和所述预设蚀刻条件均用于来限制所述第二沟道的规格,以提升金属互连器件的电迁移性能。通过在金属互连器件的器件层上已蚀刻出沟道的介质层上沉积第一阻挡层,并且第一阻挡层防止后续过度蚀刻,再在对沟道对应的凹槽进行蚀刻来至少去除第一阻挡层,以此来增加沟道的深度,再沉积出第二阻挡层,以得到第一阻挡层与第二阻挡层结合的目标阻挡层,进而通过增加沟道的接触面积以及增加第一阻挡层的厚度来优化金属互连器件的电迁移现象,解决了现有技术中金属互连器件的电迁移性能差的技术问题,达到了提高金属互连器件的电迁移性能的技术效果。

14、为使本申请的上述目的、特征和优点能更明显易懂,下文特举较佳实施例,并配合所附附图,作详细说明如下。

技术特征:1.一种金属互连器件的阻挡层制备方法,其特征在于,所述方法包括:

2.根据权利要求1所述的方法,其特征在于,所述第一沉积条件通过限制所述第一阻挡层的厚度来并防止过度蚀刻所述第二沟道,

3.根据权利要求2所述的方法,其特征在于,所述按照第一沉积条件在所述初始半导体衬底上沉积出第一阻挡层,包括:

4.根据权利要求3所述的方法,其特征在于,所述第一沉积条件通过增加沉积时间和/或增加沉积功率来增加所述粘附层和所述隔离层的厚度,

5.根据权利要求3所述的方法,其特征在于,所述第二沉积条件用于修复蚀刻所产生的缺陷,所述第二阻挡层的材质与所述隔离层的材质相同。

6.根据权利要求1所述的方法,其特征在于,所述方法还包括:

7.根据权利要求6所述的方法,其特征在于,通过以下方式在所述目标阻挡层上沉积预设金属:

8.根据权利要求6所述的方法,其特征在于,其中,所述方法还包括:

9.根据权利要求8所述的方法,其特征在于,所述第二沟道包括水平区域,所述第二沟道包括一个或多个,

10.根据权利要求6至9任一项所述的方法,其特征在于,所述预设金属为铜。

技术总结本申请提供了一种金属互连器件的阻挡层制备方法,方法包括:获取初始半导体衬底,所述初始半导体衬底包括位于金属互连器件的器件层上的介质层中的第一沟道;按照第一沉积条件在所述初始半导体衬底上沉积出第一阻挡层,所述第一阻挡层覆盖所述初始半导体衬底;按照预设蚀刻条件对所述第一沟道对应的凹槽蚀刻成至少去除底部的第一阻挡层的第二沟道,以得到待沉积衬底;按照第二沉积条件在所述待沉积衬底上沉积出第二阻挡层,以得到覆盖介质层和第二沟道的目标阻挡层;其中,所述第一沉积条件和所述预设蚀刻条件均用于限制所述第二沟道的规格,以提升金属互连器件的电迁移性能。技术研发人员:鄢江兵,张丽娜,卢金德,陈献龙受保护的技术使用者:粤芯半导体技术股份有限公司技术研发日:技术公布日:2024/12/2本文地址:https://www.jishuxx.com/zhuanli/20241204/343220.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

上一篇

一种单芯电缆的制作方法

下一篇

返回列表