1.本发明是关于物理不可复制功能(physical unclonable function,puf),尤指一种用于物理不可复制功能品质检查的内建自我测试(built-in self-test,bist)电路以及内建自我测试方法。

背景技术:

2.物理不可复制功能可视为晶片上的指纹,由于不同晶片的物理特性会因为制造过程中的某些不可控因素而有些微差异,这些差异是无法被复制或预测的,因此可作为静态熵(entropy)以用于资安相关应用。在物理不可复制功能的某些实施方式中,这个物理不可复制功能池内的某些元件需要进行注册(enrollment),以将这些元件的某些物理特性转换为随机比特(bit)。然而,注册的动作可能会被意外地跳过或具有某些缺陷,因此需要对来自所述物理不可复制功能池读取的随机比特进行侦测以检查其品质,而这会大幅增加制造时间以及人力成本。

3.因此,需要一种新颖的方法以及相关设备,以在没有副作用或较不会带来副作用的情况下检查所述物理不可复制功能池提供的随机比特的品质。

技术实现要素:

4.本发明的一目的在于提供一种用于物理不可复制功能(physical unclonable function,puf)品质检查的内建自我测试(built-in self-test,bist)电路以及内建自我测试方法,以在不大幅增加额外成本的情况下提升检查一物理不可复制功能池的品质的效率。

5.本发明至少一实施例提供一种用于物理不可复制功能品质检查的内建自我测试电路。所述内建自我测试电路可包含一物理不可复制功能阵列、耦接至所述物理不可复制功能阵列的一读出电路、以及耦接至所述读出电路的一第一比较电路。所述物理不可复制功能阵列可包含多个物理不可复制功能单元,其中所述多个物理不可复制功能单元中的每一物理不可复制功能单元包含一第一存储单元(memory cell)以及一第二存储单元。所述读出电路可用来输出包含有自多个被选择的物理不可复制功能单元的第一存储单元读取的多个输出比特(bit)的一输出字串(string)、以及包含有自所述多个被选择的物理不可复制功能单元的第二存储单元读取的多个奇偶性(parity)比特的一奇偶性字串。所述第一比较电路可用来依据所述输出字串与所述奇偶性字串之间的一汉明距离(hamming distance)产生一奇偶性检查结果。

6.本发明至少一实施例提供一种用于物理不可复制功能品质检查的内建自我测试方法。所述内建自我测试方法可包含:利用一物理不可复制功能阵列提供物理不可复制功能值,其中,所述物理不可复制功能阵列包含多个物理不可复制功能单元,以及所述多个物理不可复制功能单元中的每一物理不可复制功能单元包含一第一存储单元以及一第二存储单元;利用一读出电路输出包含有自多个被选择的物理不可复制功能单元的多个第一存

储单元读取的多个输出比特的一输出字串、以及包含有自所述多个被选择的物理不可复制功能单元的多个第二存储单元读取的多个奇偶性比特的一奇偶性字串;以及利用一第一比较电路依据所述输出字串与所述奇偶性字串之间的一汉明距离产生一奇偶性检查结果。

7.本发明至少一实施例提供一种用于物理不可复制功能品质检查的内建自我测试电路。所述内建自我测试电路可包含一物理不可复制功能阵列以及一比较电路,其中所述物理不可复制功能阵列可包含多个物理不可复制功能单元。所述比较电路可用来从所述物理不可复制功能阵列接收一第一水平字串、一第一垂直字串以及一第一歪斜字串,以计算所述第一水平字串的一水平汉明权重(hamming weight)、所述第一垂直字串的一垂直汉明权重以及所述第一歪斜字串的一歪斜汉明权重,并且判断所述水平汉明权重、所述垂直汉明权重以及所述歪斜汉明权重是否符合预定标准,以产生一健康度检查结果。

8.本发明的实施例提供了一种内建自我测试电路以及内建自我测试方法,其能藉助于内建电路检查物理不可复制功能的品质。因此,不需要外部测量仪器,而测试时间成本以及人力成本能被大幅减少。另外,本发明的实施例不会大幅增加额外硬体。因此,本发明能在没有副作用或较不会带来副作用的情况下提升检查物理不可复制功能品质的效率。

附图说明

9.图1为依据本发明一实施例的一物理不可复制功能单元的注册的示意图。

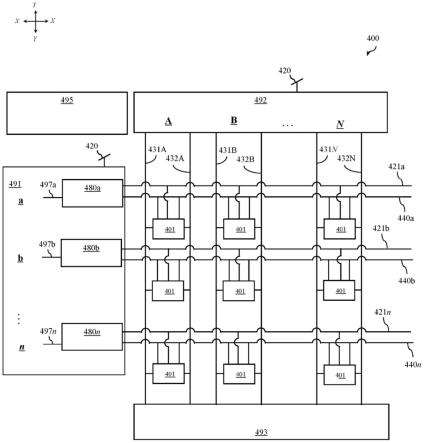

10.图2为依据本发明一实施例的一物理不可复制功能阵列的示意图。

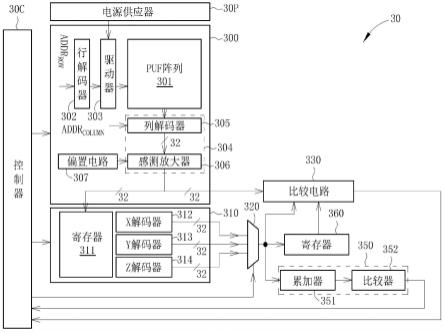

11.图3为依据本发明一实施例的一种用于物理不可复制功能品质检查的内建自我测试电路的示意图。

12.图4为依据本发明一实施例的图3所示的读出电路的某些细节。

13.图5为依据本发明一实施例的一种用于物理不可复制功能品质检查的内建自我测试方法的工作流程的示意图。

14.图6为依据本发明一实施例的针对一物理不可复制功能阵列中的一组物理不可复制功能单元的奇偶性检查的工作流程的示意图。

15.图7为依据本发明一实施例的来自一物理不可复制功能阵列中的一组被选择的物理不可复制功能单元中的每一物理不可复制单元的读出电压的分布的示意图。

16.图8为依据本发明一实施例的一物理不可复制功能阵列的一解码方案的示意图。

17.其中,附图标记说明如下:

18.10、210、220

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

物理不可复制功能单元

19.20

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

物理不可复制功能阵列

20.m0、m1、t1~t12

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

晶体管

21.wl0~wl3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

字线

22.fl0~fl3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

随动线

23.af0~af3

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制线

24.30

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

内建自我测试电路

25.30c

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

控制器

26.30p

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

电源供应器

27.300

ꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀꢀ

物理不可复制功能装置

function,简称“puf”)单元(puf unit)10的注册的示意图。如图1所示,puf单元10可至少包含两个puf存储单元诸如一第一存储单元以及一第二存储单元,其中所述第一存储单元可包含晶体管m0,以及所述第二存储单元可包含晶体管m1。在本实施例中,一高电压可被施加于晶体管m0及m1的闸极端子,使得晶体管m0及m1被同时注册,这表示晶体管m0及m1会被初始化以产生一随机码。详细来说,在晶体管m0及m1的闸极端子上累积的能量达到某个程度后,晶体管m0及m1的其中一者会发生量子隧穿(quantum-tunneling),而晶体管m0及m1的闸极端子上累积的能量会通过发生量子隧穿的晶体管的闸极漏电路径被释放。因此,晶体管m0及m1的其中一者(例如晶体管m0)会产生大于一预定阈值的量子隧穿电流,而晶体管m0及m1的另一者(例如晶体管m1)会产生小于所述预定阈值的量子隧穿电流或是不会发生量子隧穿。上述量子隧穿的机制可类似于闸极氧化层击穿(gate oxide breakdown),但并不限于硬性/破坏性击穿。例如,量子隧穿可为利用能井辅助隧穿(trap-assisted tunneling)的软击穿,但本发明不限于此。为便于理解,产生大于所述预定阈值的量子隧穿电流的晶体管可称为“破裂的”晶体管,而产生小于所述预定阈值的量子隧穿电流(或是并未发生量子隧穿)的晶体管可称为“未破裂的”晶体管。在本实施例中,发生在晶体管m0及/或晶体管m1上的量子隧穿的机制即具有本质上的随机性。另外,晶体管m0及m1因为制程变异而在物理特性上并非完美地对称或互相一致。因此,晶体管m0及m1中的哪一个会破裂会是随机的。例如,晶体管m0及m1会具有相同的概率(例如各50%)会成为破裂的晶体管,但本发明不限于此。

65.图2为依据本发明一实施例的puf阵列20的示意图。在本实施例中,puf阵列20为了说明的目的而展示了二乘二的puf阵列,但这并非对本发明的限制,而具有不同大小的puf阵列可依此类推。在本实施例中,puf阵列20的每一puf单元包含六个互相串联的晶体管,其中图1所示的注册运作可在此实施例中被采用,尤其可被施加于puf阵列20的每一puf单元。例如,puf单元210可包含互相串联的晶体管t1~t6,其中晶体管t1~t6的闸极端子分别连接至一字线wl0、一随动线(following line)fl0、一控制线af0、一控制线af1、一随动线fl1以及一字线wl1。另外,puf单元220可包含互相串联的晶体管t7~t12,其中晶体管t7~t12的闸极端子分别连接至一字线wl2、一随动线fl2、一控制线af2、一控制线af3、一随动线fl3以及一字线wl3。在本实施例中,puf单元210的晶体管t3及t4可分别作为图1所示的晶体管m0及m1的例子,而puf单元220的晶体管t9及t10可分别作为图1所示的晶体管m0及m1的例子。

66.如图2所示,puf阵列20中的第一组puf单元(例如图2的上半部所示的puf单元)耦接至一比特(bit)线bl0,以及puf阵列20中的第二组puf单元(例如图2的下半部所示的puf单元)耦接至一比特线bl1。以下描述为简明起见聚焦于所述第一组puf单元(例如puf单元210及220)的运作,其中所述第二组puf单元的类似细节可依此类推。关于puf单元210,晶体管t3及t4在注册后可视为电阻值相异的两个电阻,其中晶体管t3及t4中的破裂的晶体管会具有相对低的电阻值(其对应于相对高的闸极漏电流),而晶体管t3及t4中的未破裂的晶体管会具有相对高的电阻值(其对应于相对低的闸极漏电流)。晶体管t1及t6是用来控制puf数据的读出,而晶体管t2及t5是用来在对t3及t4进行注册的期间避免晶体管t1及t6被破坏(例如确保跨在晶体管t1及t6的每一晶体管上的电压差落在一可容忍范围内)。在某些实施例中,晶体管t2及t5可被省略,表示晶体管t1可被直接连接至晶体管t3而晶体管t6可被直

接连接至晶体管t4。puf单元220的相关细节与puf单元210类似,为简明起见在此不重复赘述。

67.表1

[0068] af0af1fl0fl1wl0wl1bl0注册vppvppvxvxvprvpr0数据提取(m0)vsen0vdd0vdd00数据提取(m1)0vsen0vdd0vdd0

[0069]

表1展示于进行注册以及数据提取时被选择的puf单元诸如puf单元210内的晶体管的控制(例如施加于其闸极端子的电压诸如施加于字线wl0、随动线fl0、控制线af0、控制线af1、随动线fl1及字线wl1的电压)。假设puf单元210被选择且puf单元220未被选择,其中零电压(例如接地电压)可被施加于未被选择的puf单元内的全部晶体管(例如puf单元220内的晶体管t7~t12)的闸极端子,以禁能(disable)所述未被选择的puf单元,但本发明不限于此。在进行puf单元210的注册的期间,控制线af0及af1会被施加电压vpp,随动线fl0及fl1会被施加电压vx,以及字线wl0及wl1会被施加电压vpr,其中比特线bl0会被施加所述零电压(在表1中标示为“0”)。假设在进行puf单元210的注册后,晶体管t3破裂了而晶体管t4未破裂,为了自puf单元210的晶体管t3提取数据(在表1中标示为“数据提取(m0)”),控制线af0可被施加感测电压vsen而控制线af1可被施加所述零电压(在表1中标示为“0”),其中字线wl0以及随动线fl0会被施加电压vdd,而字线wl1以及随动线fl1会被施加所述零电压,以及比特线bl0会被施加所述零电压。因为来自破裂的晶体管t3具有相对高的闸极漏电流,在比特线bl0上可侦测到相对低的读出电压,而来自puf单元210的晶体管t3的数据可被判断为逻辑值“0”。为了自puf单元210的晶体管t4提取数据(在表1中标示为“数据提取(m1)”),控制线af1可被施加感测电压vsen而控制线af0可被施加所述零电压,其中字线wl1以及随动线fl1会被施加电压vdd,而字线wl0以及随动线fl0会被施加所述零电压,以及比特线bl0会被施加所述零电压。因为来自未破裂的晶体管t4具有相对低的闸极漏电流,在比特线bl0上可侦测到相对低的读出电压,而来自puf单元210的晶体管t4的数据可被判断为逻辑值“1”。关于在进行puf单元210的注册后晶体管t3未破裂而晶体管t4破裂的情况,数据提取的运作可依此类推,在此不赘述。上述数据提取方案可称为单端(single-ended)感测方案,例如晶体管t3及晶体管t4的数据读出示分别运作的。在选择puf单元220的情况下的相关细节可依此类推,为简明起见在此不赘述。

[0070]

图3为依据本发明一实施例的一种用于puf品质检查的内建自我测试(built-in self-test,简称“bist”)电路30的示意图。在本实施例中,bist电路30可包含电源供应器30p、控制器30c、以及耦接至电源供应器30p以及控制器30c的一puf装置300。电源供应器30p可为高电压系统以用来提供电源给bist电路30内的元件,而控制器30c可用来控制bist运作的工作流程。puf装置300可包含puf阵列301、行(row)解码器302、耦接于puf阵列301与行解码器302之间的驱动器303、以及耦接至puf阵列301的读出电路304,其中读出电路304可包含耦接至puf阵列301的列(column)解码器305、以及耦接至列解码器305的感测放大器306。puf装置300可另包含耦接至读出电路304内的感测放大器306的偏置(bias)电路307。在本实施例中,puf阵列301可包含多个puf单元,所述多个puf单元的每一者可包含图1所示的一第一存储单元(其包含有晶体管m0)以及第二存储单元(其包含有晶体管m1)。详细来

说,所述第一存储单元可包含图2所示的puf单元210的晶体管t1~t3(或图2所示的puf单元220的晶体管t7~t9),以及所述第二存储单元可包含图2所示的puf单元210的晶体管t4~t6(或图2所示的puf单元220的晶体管t10~t12),但本发明不限于此。

[0071]

在理想状况下,关于puf阵列301内的每一puf单元的晶体管m0(例如puf单元210的电晶t3或puf单元220的晶体管t9)以及m1(例如puf单元210的电晶t4或puf单元220的晶体管t10),在进行注册后这两个晶体管的其中一个是破裂的而另一个是未破裂的。因此,对于单一的puf单元,来自晶体管m0的数据(其被称为“输出比特”)以及来自晶体管m1的数据(其被称为“奇偶性(parity)比特”)被期望具有相反的逻辑值(例如若两者的其中一个为“1”。则另一者为“0”)。实作上,puf阵列301内的一或多个puf单元的注册可能是有缺陷的。例如,单一的puf单元内的晶体管m0及m1均为破裂的,导致其输出比特与奇偶性比特均为“0”。又例如,单一的puf单元内的晶体管m0及m1均为未破裂的,导致其输出比特与奇偶性比特均为“1”。

[0072]

读出电路304可用来从所述第一存储单元诸如晶体管m0输出一输出比特并且从所述第二存储单元诸如晶体管m1输出一奇偶性比特。具体来说,行解码器302可依据行位址addr

row

产生控制信号以选择一行puf单元,而驱动器303可依据这些控制信号使用电源供应器30p所提供的驱动电压驱动puf阵列301(例如驱动图2所示的字线wl0及wl1),以容许读出电路304自一行被选择的puf单元的每一puf单元提取数据(例如所述输出比特及/或所述奇偶性比特)。另外,列解码器305可用来依据列位址addr

column

选择至少一列puf单元,以感测来自puf阵列301的至少一列被选择的puf单元的读出电压,而感测放大器304可判断来自被选择的puf单元的数据的逻辑值为“0”或“1”,其中感测放大器304可依据偏置电路307所提供的偏置电压运作。为便于理解,本实施例可用32

×

32的puf阵列作为puf阵列301的例子,但本发明不限于此。需注意的是,puf阵列301并非必须为方形阵列(例如在puf阵列301中的行的数量可异于列的数量),而列解码器305并非必须选择一整个列的puf单元以进行读出。在某些实施例中,puf阵列301可为2

×

512的puf阵列,其中行解码器302可从这个2

×

512的puf阵列选择一行puf单元(例如512个puf单元),而列解码器305可从这512个puf单元中只选择32个puf单元以提取32比特的数据,但本发明不限于此。

[0073]

图4为依据本发明一实施例的图3所示的读出电路304的某些细节(例如其内的列解码器305以及感测放大器306)。在本实施例中,图3所示的列解码器305可包含开关控制电路305c(标示为“开关控制”以求简明)以及开关电路305w,其中开关电路305w可包含多个开关诸如dl0、dl1、dl2、

…

及dl31,而开关控制电路305c可依据列位址addr

column

产生32个开关控制信号以分别用来控制开关dl0、dl1、dl2、

…

及dl31。另外,图3所示的感测放大器306可用来依据自被选择的puf单元的晶体管m0读取的读出电压输出所述输出比特并且依据自被选择的puf单元的晶体管m1读取的读出电压输出所述奇偶性比特。尤其,图3所示的感测放大器306可包含一或多个放大器电路诸如sa0、sa1、sa2、

…

及sa31以分别用来输出比特数据data0、data1、data2、

…

及data31。在本实施例中,开关dl0可耦接于puf阵列301的比特线bl0与放大器电路sa0之间;开关dl1可耦接于puf阵列301的比特线bl1与放大器电路sa1之间;开关dl2可耦接于puf阵列301的比特线bl2与放大器电路sa2之间;而其余可依此类推,例如开关dl31可耦接于puf阵列301的比特线bl31与放大器电路sa31之间;但本发明不限于此。在某些实施例中,开关电路305w可包含两层以上的开关以实施更多弹性的开关控制方

案,但本发明不限于此。

[0074]

在图4的实施例中,放大器电路sa0、sa1、sa2、

…

及sa31的每一者可运作为一比较器。在下列说明中是以放大器电路sa0作为例子,其中其他的放大器电路诸如放大器电路sa1、sa2、

…

及sa31的运作与放大器电路sa0类似,在此不重复赘述。当来自被选择的puf单元(例如其内的晶体管m0)的读出电压小于参考电压vref,所述读出电压与参考电压vref之间的电压差可被放大而使放大器电路sa0的输出为一高电压(例如电压vdd),而所述输出比特可被判断为具有一第一逻辑值诸如“1”。当来自被选择的puf单元(例如其内的晶体管m0)的读出电压大于参考电压vref,所述读出电压与参考电压vref之间的电压差可被放大而使放大器电路sa0的输出为一低电压(例如所述零电压),而所述输出比特可被判断为具有一第二逻辑值诸如“0”。通过感测放大器306自晶体管m1提取所述奇偶性比特的运作与自晶体管m0提取所述输出比特的运作类似,相关细节在此不重复赘述。

[0075]

为了检查puf装置300(尤指其内的puf阵列301)的品质,bist电路30可用来检查puf装置300所提供的puf数据的真实性(authenticity)、可靠性(reliability)以及随机性(randomness)。除了上述元件以外,bist电路30可另包含耦接至puf装置300的寄存装置310、耦接至寄存装置310的多工器320、耦接至puf装置300及多工器320的比较电路330、耦接至多工器320的比较电路350、以及耦接至多工器320及比较电路330的寄存器360,如图3所示。尤其,寄存电路310可包含耦接至puf装置300的寄存器311、一水平解码器诸如耦接于寄存器311与多工器320之间的x解码器312、一垂直解码器诸如耦接于寄存器311与多工器320之间的y解码器313、以及一歪斜解码器诸如耦接于寄存器311与多工器320之间的z解码器314。多工器320是用来选择x解码器312、y解码器313及z解码器314的其中一者以用于自寄存器311输出数据/字串(string)。

[0076]

在本实施例中,读出电路304可一次从puf装置300截取32比特的数据(例如自puf阵列301的一行puf单元的数据)并且储存在寄存器311,但本发明不限于此。在对puf阵列301的全部行的puf单元进行数据提取后,puf阵列301中的全部的puf数据(例如自puf装置300提取的32

×

32个输出比特)可被倒进(dump)寄存器311,但本发明不限于此。另外,x解码器312可用来从寄存器311提取数据,并且藉由将从puf阵列301中的一组水平puf单元读取的多个输出比特收集为一组,以产生一水平字串,其中所述组水平puf单元内的puf单元在puf阵列301中是以水平方向排列。y解码器313可用来从寄存器311提取数据,并且藉由将从puf阵列301中的一组垂直puf单元读取的多个输出比特收集为一组,以产生一垂直字串,其中所述组垂直puf单元内的puf单元在puf阵列301中是以垂直方向排列。z解码器314可用来从寄存器311提取数据,并且藉由将从puf阵列301中的一组歪斜puf单元读取的多个输出比特收集为一组,以产生一歪斜字串,其中所述组歪斜puf单元内的puf单元在puf阵列301中是以歪斜方向排列。

[0077]

图5为依据本发明一实施例的一种用于puf品质检查的bist方法的工作流程的示意图,其中图5所示的工作流程可藉由图3所示的bist电路30来执行。需注意的是,图5所示的工作流程只是为了说明的目的,并非对本发明的限制。另外,一或多个步骤可在此工作流程中被新增、删除或修改。若能得到相同的结果,这些步骤并非必须完全依照图5所示的顺序来执行。为便于理解,请连同图3来参考图5。

[0078]

在步骤s510中,bist电路30可利用pug阵列301提供puf值,其中puf阵列301包含多

个puf单元(例如32

×

32个puf单元),以及所述多个puf单元的每一者可包含一第一存储单元诸如晶体管m0以及一第二存储单元诸如晶体管m1。

[0079]

在步骤s520中,bist电路30可利用读出电路304自所述第一存储单元诸如晶体管m0输出一输出比特并且自所述第二存储单元诸如晶体管m1输出一奇偶性比特。

[0080]

在步骤s530中,bist电路30可利用比较电路330将一输出字串与一奇偶性字串作比较以产生一奇偶性检查结果,其中所述输出字串包含分别自所述多个puf单元中的多个被选择的puf单元读取的多个输出比特,以及所述奇偶性字串包含分别自所述多个被选择的puf单元读取的多个奇偶性比特。

[0081]

详细来说,当puf阵列301中的一第一行puf单元被选择,多工器320可选择x解码器312以自寄存器311内的第一行储存单元输出一输出字串,其中所述输出字串内的输出比特是从所述第一行puf单元提取的。读出电路304可自所述第一行puf单元输出一奇偶性字串,其中所述奇偶性字串内的奇偶性比特是从所述第一行puf单元提取的。对于所述第一行puf单元的每一puf单元,比较电路330(例如32比特的比较电路)可检查所述每一puf单元的输出比特与奇偶性比特是否具有相反的逻辑值以产生一比较结果,其中比较电路330可包含多个互斥或(exclusive or,xor)逻辑电路以逐比特地(bit by bit)比较两个字串。所述比较结果可指出所述第一行puf单元中的那些puf单元通过了奇偶性检查(即其输出比特与奇偶性比特具有相反的逻辑值)。比较电路330可包含一计数器以计算在所述第一行puf单元中有多少个puf单元通过了奇偶性检查。例如,比较电路330的所述计数器可计算所述输出字串与所述奇偶性字串之间的汉明距离(hamming distance)以作为所述第一行puf单元的奇偶性检查结果,并且将此奇偶性检查结果回传给控制器30c以供进一步判断的使用。针对puf阵列301中的其他行puf单元的奇偶性检查可依此类推,为简明起见在此不赘述。

[0082]

为便于理解上述奇偶性检查,请参考图6,其为依据本发明一实施例的针对puf阵列301中的一组puf单元的奇偶性检查的工作流程的示意图。需注意的是,图6所示的工作流程只是为了说明的目的,并非对本发明的限制。另外,一或多个步骤可在此工作流程中被新增、删除或修改。若能得到相同的结果,这些步骤并非必须完全依照图6所示的顺序来执行。

[0083]

在步骤s610中,puf数据(例如多个输出比特)以单端感测方案自晶体管m0被提取。

[0084]

在步骤s620中,puf数据(例如多个奇偶性比特)以单端感测方案自晶体管m1被提取。

[0085]

在步骤s630中,bist电路30(例如比较电路330)检查来自晶体管m0的puf数据与来自晶体管m1的puf数据之间的一汉明距离(在图6中标示为“检查m0与m1之间的hd”以求简明)。

[0086]

在步骤s640中,控制器30c可判断所述汉明距离的计算结果(例如指出所述汉明距离的一奇偶性检查结果)是否符合预定标准(例如判断所述汉明距离是否大于一预定值),其中为简明起见,本步骤在图6中标示为“hd的结果符合标准?”。例如,当所述多个输出比特及所述多个奇偶性比特均为32比特的字串,所述预定值可设为30。若判断结果为“是”,工作流程进入步骤s650;而若判断结果为“否”,工作流程进入步骤s660。例如,针对puf阵行301中的单一行puf单元,控制器30c可判断对应于这个单一行puf单元的汉明距离的计算结果是否符合标准。又例如,在计算分别对应于puf阵列301中的全部的行的puf单元的汉明距离的计算结果后,控制器30c可依据这些计算结果的总结/总和来判断整个puf阵列301是否符

合标准。

[0087]

在步骤s650中,bist电路30可利用puf装置300自晶体管m0或m1输出puf数据。例如,当利用所述puf数据作为一最终随机码时,所述puf数据只从晶体管m0提取而不会从晶体管m1提取(例如只有输出比特从puf阵列301中被输出,而奇偶性比特不会被输出)。又例如,当利用所述puf数据作为所述最终随机码时,所述puf数据只从晶体管m1提取而不会从晶体管m0提取(例如只有奇偶性比特从puf阵列301中被输出,而输出比特不会被输出)。

[0088]

在步骤s660中,bist电路30可输出一警报信号,以将puf装置300的奇偶性检查结果无法符合标准的状况通报使用者或耦接至bist电路30的电子装置。

[0089]

在上述说明中,一行puf单元可作为进行奇偶性检查的单位的例子,但本发明不限于此。在其他实施例中,不同数量的puf单元可被收集为一组以作为进行上述奇偶性检查的单位,而比较电路330的比特数可据以变化。如上所述,来自相同puf单元的输出比特以及奇偶性比特被期望具有相反的逻辑值。实作上,当puf阵列301中的有缺陷的puf单元的数量小于一可容忍数量,puf阵列301依然可被视为通过奇偶性检查。因此,判定puf阵列301是否通过奇偶性检查的标准的实施细节可依据厂商需求而予以变化,而不限于上述说明中的任一特定规则。

[0090]

图7为依据本发明一实施例的来自puf阵列301中的一组被选择的puf单元中的每一puf单元的读出电压(或读出电流)的分布的示意图,其中图7的横轴表示来自晶体管m0或m1的读出电压(或读出电流),而图7的纵轴表示对应于这些读出电压(或读出电流)的命中数(number of hits)。当感测电压vsen被设至正常感测电平v

ns

并且参考电压vref被设至依正常参考电平v

nr

时,来自所述组被选择的puf单元内的破裂的晶体管的读出电压的分布可由图7中标示为“开启正常读取(on normal read,简称onnr)”的曲线来表示,而来自所述组被选择的puf单元内的未破裂的晶体管的读出电压的分布可由图7中标示为“关闭正常读取(off normal read,简称offnr)”的曲线来表示。为了检查puf装置300的可靠性,bist电路30可对感测电压vsen或参考电压vref作变动(shift)以使读出运作变得更加关键的或阈的(critical),而若从所述组被选择的puf单元提取的数据未改变,表示感测电压vsen或参考电压vref被施加的变动量是可容忍的。

[0091]

在一实施例中,bist电路30可用一偏移(offset)电压δvr变动参考电压vref以将参考电压vref变动至一开启裕量(on-margin)电平onmvref(例如onmvref=v

nr

δvr),这使得来自破裂的晶体管的读出电压被判断为“0”的运作变得更加阈的。在参考电压vref被设至开启裕量电平onmvref的情况下,puf阵列301中的全部的puf数据(自puf装置300提取的32

×

32个输出比特)可先被倒至寄存器311。当puf阵列301中的第一行puf单元被选择时,多工器320可选择x解码器312以自寄存器311的第一行储存单元输出一参考电压开启裕量字串,其中所述参考电压开启裕量字串内的输出比特是从所述第一行puf单元提取的。bist电路30可用偏移电压δvr变动参考电压vref以将参考电压vref另变动至一关闭裕量(off-margin)电平offmvref(例如offmvref=v

nr

–

δvr),这使得来自未破裂的晶体管的读出电压被判断为“1”的运作变得更加阈的。读出电路304可自所述第一行puf单元输出一参考电压关闭裕量字串,其中所述参考电压关闭裕量字串内的输出比特是从所述第一行puf单元提取的。比较电路330可检查所述参考电压开启裕量字串与所述参考电压关闭裕量字串是否互相一致,以产生一参考电压裕量检查结果,其中开启裕量电平onmvref大于关闭裕量电平

offmvref。比较电路330可包含一计数器以计算在所述第一行puf单元中有多少个puf单元通过裕量检查。例如,比较电路330的所述计数器可产生所述参考电压裕量检查结果,其指出在所述第一行puf单元中有多少个puf单元是能够容忍此变动量(即偏移电压δvr),并且考将所述参考电压裕量检查结果回传给控制器30c以供进一步判断的使用。例如,当所述参考电压裕量检查结果指出所述参考电压开启裕量字串与所述参考电压关闭裕量字串互相一致时,控制器30c可判断所述第一行puf单元通过参考电压裕量检查。

[0092]

在一实施例中,bist电路30可用一偏移电压δvs变动感测电压vsen以将感测电压vsen变动至一开启裕量电平v

onms

(例如v

onms

=v

ns

–

δvs),这使得来自破裂的晶体管的读出电压的分布被往左平移为在图7中标示为onmr的分布,而来自破裂的晶体管的读出电压被判断为“0”的运作变得更加阈的。在感测电压vsen被设至开启裕量电平v

onms

的情况下,puf阵列301中的全部的puf数据(自puf装置300提取的32

×

32个输出比特)可先被倒至寄存器311。当puf阵列301中的第一行puf单元被选择时,多工器320可选择x解码器312以自寄存器311的第一行储存单元输出一感测电压开启裕量字串,其中所述感测电压开启裕量字串内的输出比特是从所述第一行puf单元提取的。bist电路30可用偏移电压δvs变动感测电压vsen以将感测电压vsen另变动至一关闭裕量电平v

offms

(例如v

offms

=v

ns

δvs),这使得来自未破裂的晶体管的读出电压的分布被向右平移为图7中标示为offmr的分布,而来自未破裂的晶体管的读出电压被判断为“1”的运作变得更加阈的。读出电路304可自所述第一行puf单元输出一感测电压关闭裕量字串,其中所述感测电压关闭裕量字串内的输出比特是从所述第一行puf单元提取的。比较电路330可检查所述感测电压开启裕量字串与所述感测电压关闭裕量字串是否互相一致,以产生一感测电压裕量检查结果,其中开启裕量电平v

onms

小于关闭裕量电平v

offms

。比较电路330的所述计数器对于所述感测电压裕量检查结果的运作与对于所述参考电压裕量检查结果类似,为简明起见在此不赘述。

[0093]

需注意的是,针对puf阵列301中的其他行的puf单元的裕量检查(例如参考电压裕量检查以及感测电压裕量检查)可依此类推,相关细节在此不重复赘述。另外,在上述说明中,一行puf单元可作为进行裕量检查的单位的例子,但本发明不限于此。在其他实施例中,不同数量的puf单元可被收集为一组以作为进行上述裕量检查的单位,而比较电路330的比特数可据以变化。另外,用来判定puf阵列301是否通过裕量检查的标准的实施细节(例如无法容忍针对感测电压vsen或参考电压vref施加的偏移量的puf单元的可接受数量)可依据厂商需求而予以变化,而不限于上述说明中的任一特定规则。在某些实施例中,当所述裕量检查(例如所述参考电压裕量检查即所述感测电压裕量检查的任一者)失败,控制器30c可降低偏移电压δvr及/或δvs直到puf阵列301通过所述裕量检查,而puf阵列301的一对应程度的可靠性可依据降低后的偏移电压δvr及/或δvs估计得知,但本发明不限于此。

[0094]

图8为依据本发明一实施例的puf阵列301的一解码方案的示意图,其中puf阵列301内的全部puf数据(例如来自puf装置300的32

×

32个输出比特)可被倒至寄存器311。为便于理解,储存于寄存器311的数据可用d

ra,ca

来表示,其中ra可代表行位址,而ca可代表列位址。例如,储存在寄存器311的第一行的数据可为{d

0,0

,d

0,1

,d

0,2

,

…

,d

0,30

,d

0,31

};储存在寄存器311的第二行的数据可为{d

1,0

,d

1,1

,d

1,2

,

…

,d

1,30

,d

1,31

};储存在寄存器311的第三行的数据可为{d

2,0

,d

2,1

,d

2,2

,

…

,d

2,30

,d

2,31

};而其余可依此类推,例如储存在寄存器311的第三十二行的数据可为{d

31,0

,d

31,1

,d

31,2

,

…

,d

31,30

,d

31,31

}。另外,x解码器312可藉由将自水平方

向排列的一组水平puf单元读取的输出比特收集为一组以产生水平字串px(0)、px(1)、px(2)、

…

及px(31)的每一者,其中这些水平字串{px(nx)|nx=0,1,2,

…

,31}={d

nx,0

,d

nx,1

,d

nx,2

,

…

,d

nx,30

,d

nx,31

}。y解码器313可藉由将自垂直方向排列的一组垂直puf单元读取的输出比特收集为一组以产生垂直字串px(0)、px(1)、px(2)、

…

及px(31)的每一者,其中这些垂直字串{py(ny)|ny=0,1,2,

…

,31}={d

0,ny

,d

1,ny

,d

2,ny

,

…

,d

30,ny

,d

31,ny

}。z解码器314可藉由将自歪斜方向排列的一组歪斜puf单元读取的输出比特收集为一组以产生歪斜字串pz(0)、pz(1)、pz(2)、

…

及pz(31)的每一者,其中pz(0)={d

0,0

,d

1,1

,d

2,2

,

…

,d

30,30

,d

31,31

}、pz(1)={d

0,1

,d

1,2

,d

2,3

,

…

,d

30,31

,d

31,0

}、以及pz(2)={d

0,2

,d

1,3

,d

2,4

,

…

,d

30,0

,d

31,1

},其余可依此类推,例如pz(30)={d

0,30

,d

1,31

,d

2,0

,

…

,d

30,28

,d

31,29

}、以及pz(31)={d

0,31

,d

1,0

,d

2,1

,

…

,d

30,29

,d

31,30

}。在本实施例中,bist电路30可依据水平字串{px(nx)|nx=0,1,2,

…

,31}的至少一者、垂直字串{py(ny)|ny=0,1,2,

…

,31}及/或歪斜字串{pz(nz)|nz=0,1,2,

…

,31}的至少一者(例如其组合)产生至少一健康度检查结果。

[0095]

在健康度检查的第一部分,比较电路250可利用其内的累加器351(例如5比特的累加器)计算水平字串{px(nx)|nx=0,1,2,

…

,31}的每一者的一水平汉明权重(hamming weight)、垂直字串{py(ny)|ny=0,1,2,

…

,31}的每一者的一垂直汉明权重以及歪斜字串{pz(nz)|nz=0,1,2,

…

,31}的每一者的一歪斜汉明权重。比较电路250可另利用其内的比较器352(例如5比特的比较器)判断所述水平汉明权重、所述垂直汉明权重以及所述歪斜汉明权重是否符合预定标准(例如是否落在一预定范围),以产生所述健康度检查的所述第一部分的结果。需注意的是,一个字串的汉明权重为这个字串中的非零比特(例如逻辑值“1”)的数量,而一组随机比特中的零比特的数量与非零比特的数量是被期望为大致相同。基于期望自puf阵列301中的一组puf单元提取的零比特的数量与非零比特的数量之间的差值小于一可容忍值的目的,用于判断puf阵列301是否通过所述健康度检查的所述第一部分的所述预定标准的实施细节可依据厂商需求而予以变化,而不限于上述说明的任一特定规则。例如,某组puf单元(例如水平字串px(nx)、垂直字串py(ny)及歪斜字串pz(nz)的任一者或每一者)在这组puf单元的汉明权重(例如上述水平汉明权重、垂直汉明权重以及歪斜汉明权重的任一者或每一者)等于一理想值时(例如当32比特的字串的汉明权重等于16时)可被判断为通过健康度测试。又例如,某组puf单元(例如水平字串px(nx)、垂直字串py(ny)及歪斜字串pz(nz)的任一者或每一者)在这组puf单元的汉明权重(例如上述水平汉明权重、垂直汉明权重以及歪斜汉明权重的任一者或每一者)相对于所述理想值的误差落在一可容忍范围内诸如

±

4%时(例如当32比特的字串的汉明权重落在14到18之间的范围内时)可被判断为通过健康度测试。需注意的是,所述预定标准(例如所述可容忍范围)可基于一统计分布模型的计算来决定,并且在实作中可依据需求(例如可接受的随机性)做调整。

[0096]

在所述健康度检查的第二部分,bist电路30可藉助于比较电路330计算水平字串px(m1)与px(m2)之间的一水平汉明距离、垂直字串py(m1)与py(m2)之间的一垂直汉明距离、以及歪斜字串pz(m1)与pz(m2)之间的一歪斜汉明距离,以依据所述水平汉明距离、所述垂直汉明距离及/或所述歪斜汉明距离(例如其组合)产生所述健康检查的所述第二部分的结果,其中m1及m2为0到31之间的范围内的两个相异的值。另外,本实施例较佳为选择实体上相邻的两组puf比特(例如m2=m1 1)以用于进行上述计算,但本发明不限于此。在某些实施例中,m2=m1 n,其中n为任意合适的整数。

[0097]

例如,x解码器312以及多工器320可先将水平字串px(0)输出至寄存器360(例如32比特的寄存器),并接着将水平字串px(1)输出至比较电路330。比较电路330可将水平字串px(0)与水平字串px(1)作逐比特地比较,并且可依据水平字串px(0)与水平字串px(1)的比较结果计算(例如藉由一计数器)水平字串px(0)与水平字串px(1)之间的水平汉明距离。其余可依此类推,例如水平字串px(2)与水平字串px(3)之间的水平汉明距离、水平字串px(4)与水平字串px(5)之间的水平汉明距离、

…

以及水平字串px(30)与水平字串px(31)之间的水平汉明距离可通过上述方式计算得到,即m1=0、2、4、

…

及30而m2=1、3、5、

…

及31,但本发明不限于此。类似地,y解码器313以及多工器320可先将垂直字串py(0)输出至寄存器360(例如32比特的寄存器),并接着将垂直字串py(1)输出至比较电路330。比较电路330可将垂直字串py(0)与垂直字串py(1)作逐比特地比较,并且可依据垂直字串py(0)与垂直字串py(1)的比较结果计算(例如藉由一计数器)垂直字串py(0)与垂直字串py(1)之间的垂直汉明距离。其余可依此类推,例如垂直字串py(2)与垂直字串py(3)之间的垂直汉明距离、垂直字串py(4)与垂直字串py(5)之间的垂直汉明距离、

…

以及垂直字串py(30)与垂直字串py(31)之间的垂直汉明距离可通过上述方式计算得到,即m1=0、2、4、

…

及30而m2=1、3、5、

…

及31,但本发明不限于此。类似地,z解码器314以及多工器320可先将歪斜字串pz(0)输出至寄存器360(例如32比特的寄存器),并接着将歪斜字串pz(1)输出至比较电路330。比较电路330可将歪斜字串pz(0)与歪斜字串pz(1)作逐比特地比较,并且可依据歪斜字串pz(0)与歪斜字串pz(1)的比较结果计算(例如藉由一计数器)歪斜字串pz(0)与歪斜字串pz(1)之间的歪斜汉明距离。其余可依此类推,例如歪斜字串pz(2)与歪斜字串pz(3)之间的歪斜汉明距离、歪斜字串pz(4)与歪斜字串pz(5)之间的歪斜汉明距离、

…

以及歪斜字串pz(30)与歪斜字串pz(31)之间的歪斜汉明距离可通过上述方式计算得到,即m1=0、2、4、

…

及30而m2=1、3、5、

…

及31,但本发明不限于此。在某些实施例中,m1=0、1、2、

…

及30而m2=1、2、3、

…

及31。在某些实施例中m1=0、4、8、12、

…

及28而m2=1、5、9、

…

及29。这些设计上的变化均隶属于本发明的范畴。

[0098]

需注意的是,从一组随机比特提取的任两个字串是被期望为与彼此尽可能地相异,而这两个字串之间的汉明距离是被期望为大于一预定值。基于此,用于判断puf阵列301是否通过所述健康度检查的所述第二部分的预定标准的实施细节可依据厂商需求予以变化,而不限于上述说明的任一特定规则。另外,在控制器30c接收到所述健康度检查的所述第一部分与所述健康度检查的所述第二部分的结果后,控制器30c可总结这些结果以判断puf阵列301是否通过所述健康度检查。例如,控制器30c可只在所述健康度检查的所述第一部分与所述第二部分均符合预定标准时才判断puf阵列301通过所述健康度检查,但本发明不限于此。

[0099]

总结来说,本发明的实施例提供了一种bist电路以及bist方法,能藉助于本发明所提出的奇偶性检查、裕量检查以及健康度检查确保真实性、可靠性以及随机性。上述奇偶性检查、裕量检查以及健康度检查可分别进行或一并进行。另外,由于相关测试电路是连同puf装置被内建在其中,因此不需要外部的量测设备,而测试时间成本与人力成本能大幅地减少。另外,本发明的实施例不会大幅的增加额外硬体,因此本发明能在没有副作用或较不会带来副作用的情况下提升检查puf品质的效率。

[0100]

以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技

术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。