电接触部和用于制造电接触部的方法与流程

- 国知局

- 2024-07-27 12:33:06

[0001]本发明涉及一种在重布线和导体区域之间的电接触部,其中,导体区域布置在soi晶片或soi芯片上方的导体层中,其中,在导体层上方并且在重布线下方布置有覆盖层。此外,本发明涉及一种用于制造电接触部的方法和一种包括电接触部的系统。背景技术:[0002]通常已知电接触部、尤其是硅通孔(tsvs)。这种接触部可以穿过晶片或者晶片的仅一个部分区域。典型地尝试在实现小通过电阻的同时实现尽可能小的贯通接触部。为了实现这种情况,经常在晶片中例如借助于沟槽过程或者激光产生具有近似垂直的壁的狭长孔。然后将绝缘部沉积到孔中。在孔的底部处的区域中穿过绝缘部进行直至位于下方的导电轨的接触蚀刻。然后,所述孔被完全或部分地填充以导电材料或者粘附物/障碍物和导电层。在此,这样选择导电材料,使得实现小电阻。整体上,将绝缘部和之后的导电材料引入到相同的先前产生的孔中。[0003]然而,对于很多系统、例如微机电构件,这种已知的硅通孔不能制成或者仅以非常高的耗费和相关的费用制成,因为在已知的方法中还需要附加的蚀刻停止层。[0004]相应地,对于微机械构件大部分寻求另外的解决方案,并且硅通孔由掺杂硅制成。然而,这种硅通孔具有相对较高的电阻。因此,高频应用是不可能的或者仅在容忍质量损失的情况下是可能的。技术实现要素:[0005]本发明的任务是,提供在重布线和导体区域之间的电接触部,该电接触部可以在多方面使用、尤其用于微机电系统,具有高导电性并且优选能够以合适的耗费和相对较低的过程费用制成。[0006]根据主权利要求,根据本发明的在重布线和导体区域之间的电接触部相对于现有技术具有以下优点:接触部的绝缘(尤其借助于第一凹槽布置,该第一凹槽布置使覆盖层的接触部区域与剩余的覆盖层绝缘)的功能步骤和金属材料的布置可以分开地实施,其中,导体区域布置在soi晶片或soi芯片上方的导体层中。由此,可以取消在覆盖层和导体层之间(尤其在接触部区域中)的附加的蚀刻停止层。根据本发明,因此可能的是,提供节省成本的电接触部,该电接触部具有高导电性能。因此,例如可以实现用于在高频范围的微机电元件中的应用的特定优点。而通过在覆盖层中的接触部区域内部不具有(带高导电性能的)金属材料的硅通孔不能实现这种优点。同样地,这种优点(小费用和灵活的可使用性)通过绝缘体和之后的金属相继布置在相同的、先前产生的孔中的系统或过程不能实现。[0007]根据本发明,概念“上方”和“下方”涉及相对于soi晶片或芯片的表面的距离。因此,布置在导体层上方并且布置在重布线下方的覆盖层例如比导体层距离soi晶片(或soi芯片)的表面远,并且没有重布线距离soi晶片(或soi芯片)的表面远。[0008]有利的扩展方案和实施方式由从属权利要求得出。[0009]根据本发明的实施方式,在导体区域中还构造有开口,其中,金属材料还布置在导体区域的开口中,由此能够有利地在小的过程耗费的同时实现特别高的导电性能,因为金属材料可以在电接触部的较大距离上构造。[0010]根据本发明的实施方式,在第一凹槽布置中布置有第一绝缘体,由此能够有利地实现在接触部区域(和由此电接触部本身)和剩余的覆盖层之间的高品质的绝缘。同时可以实现在硅通孔绝缘部和金属之间的空间分隔,因为第一绝缘体不布置在开口中。因此,可以特别有利地取消之后在开口的底部区域中的蚀刻步骤。[0011]根据本发明的实施方式,在第一接触区域中构造在导体层和覆盖层之间的直接接触,其中,第一接触区域至少部分地、优选完全地围绕开口,由此能够构造完全由第一凹槽布置围绕的第一接触区域。因此,可以实现在电接触部和剩余的覆盖层之间的高品质绝缘,并且同时以简单的方式构造在接触部区域和导体区域中的开口(并且以金属材料填充)。[0012]接触部区域全面地围绕开口,由此可以实现在(覆盖层中的)第一凹槽布置和布置在其中的第一绝缘体和电贯穿接触部的金属材料之间的有利的空间分隔。在此,接触部区域优选在覆盖层的(垂直于衬底/芯片表面的)整个延展尺度上全面地围绕开口。[0013]根据本发明的实施方式,金属材料布置在导体区域中的开口的侧壁上,其中,金属材料尤其布置在接触部区域中的开口的另外的侧壁上,由此能够实现在导体区域和金属材料之间的大面积的直接接触。大接触面积能够以有利的方式减小组件的总电阻。此外,由此可能的是,掺杂分布在导体层/导体区域内部在竖直方向上不重要并且可以实现在导体区域的整个高度上的优化接触。而在金属材料和导体区域之间仅在导体区域的表面上直接接触(即没有金属材料在导体区域中的开口的侧壁上的布置)的情况下不能实现这些优点。[0014]根据本发明的实施方式,开口还构造在soi晶片或soi芯片的硅层的附加区域中,其中,金属材料还布置在附加区域中的开口中,由此可能的是,金属材料跨越(覆盖层的)接触部区域和(导体层的)导体区域延伸到soi晶片或soi芯片的硅层的附加区域中,由此可以实现特别小的电阻。[0015]根据本发明的实施方式优选的是,开口至少基本上垂直于晶片或芯片表面地构造。[0016]根据本发明的实施方式可以考虑,覆盖层和/或导体层具有(掺杂的)硅。[0017]根据本发明的实施方式可以考虑,在soi晶片或soi芯片中构造有机电构件/系统。尤其设置为,导体区域与机电构件的部件连接并且这样在重布线和机电构件的部件之间形成导电连接。[0018]根据本发明的实施方式可以考虑,导体区域或导体轨尽可能宽地构型,以便在导体轨中使电阻保持小。尤其可能的是,导体轨/导体区域比典型的硅通孔直径(尤其是在开口中的金属材料的直径)和对应于所述直径的接触面明显更宽地设计。这尤其在钨-硅通孔中适用,所述钨-硅通孔优选在钨沉积时本身应封闭。[0019]本发明的另一主题是根据本发明的实施方式的用于制造电接触部的方法,其中,所述方法包括以下步骤:[0020]--在第一步骤中,将覆盖层这样结构化,使得构造出接触部区域,该接触部区域借助于第一凹槽布置相对于剩余的覆盖层绝缘,[0021]--在第二步骤中,至少在接触部区域中构造开口,[0022]--在第三步骤中,在开口中布置金属材料,其中,金属材料使重布线和导体区域连接。[0023]根据本发明的实施方式可以考虑,在第一步骤中除了构造第一凹槽布置之外还进一步结构化覆盖层,例如建立沟槽,所述沟槽能够实现,(在第一步骤之后)执行蚀刻步骤,在该蚀刻步骤中蚀刻掉第二绝缘体、第二绝缘体层、第三绝缘体和第三绝缘体层的部分,以便露出微机电构件。[0024]根据本发明的实施方式,在第二步骤中开口还构造在导体区域中,其中,在第三步骤中,金属材料还布置在导体区域中的开口中,由此能够在小过程耗费的同时实现特别高的导电性。优选地设置为,开口(基本上)垂直于晶片/芯片的表面延伸并且金属材料形成在导体区域和重布线之间的无中断的连接。[0025]根据本发明的实施方式,在第一步骤中覆盖层构造在第一接触区域中,其中,在第一接触区域中形成在导体层和覆盖层之间的直接接触,其中,覆盖层尤其还布置在第二绝缘体层上,由此可能的是,邻接于之后的接触部区域构造有第一接触区域,在该第一接触区域中覆盖层和导体层具有(直接的)接触面。相应地可能的是,开口在之后的进程中既构造在覆盖层的接触部区域中也构造在导体层的(至少部分在该接触部区域下方并且邻接于该接触部区域布置的)导体区域中。[0026]根据本发明的实施方式,在第一中间步骤中、在第一步骤之后并且在第二步骤之前,将第一绝缘体布置在第一凹槽布置中,其中,还将第一绝缘体层布置在覆盖层上,其中,优选在第二中间步骤中、在第一中间步骤之后并且在第二步骤之前,移除在第三接触区域中、尤其在接触部区域处的第一绝缘体层,由此能够形成在接触部区域和剩余的覆盖层之间的高品质绝缘。优选地,同时(或在一个步骤中)施加第一绝缘体层和第一绝缘体。特别优选地,由相同的电介质组成第一绝缘体和第一绝缘体层。[0027]根据本发明的实施方式,在第三步骤中将重布线、尤其是金属重布线布置在第一绝缘体层上,由此能够形成仅在接触部区域中或在金属材料处在重布线和覆盖层之间的电接触。[0028]根据本发明的实施方式,[0029]--在第一预步骤中,在soi晶片或soi芯片的硅层中构造结构,[0030]--在第二预步骤中、在第一预步骤之后,将第三绝缘体至少部分地布置在所述结构中,并且在硅层上方布置第三绝缘体层,[0031]--在第三预步骤中、在第二预步骤之后,移除在第二接触区域中的第三绝缘体层,[0032]--在第四预步骤中、在第三预步骤之后,将导体层布置在第三绝缘体层上并且尤其在第二接触区域中形成在导体层和硅层之间的直接接触,其中,导体层这样结构化,使得构造有导体区域,该导体区域借助于第二凹槽布置相对于导体层的另外的导体区域绝缘,[0033]--在第五预步骤中、在第四预步骤之后,将第二绝缘体层布置在导体层上,其中,在第二凹槽布置中布置第二绝缘体,[0034]--在第六预步骤中、在第五预步骤之后并且在第一步骤之前,移除在第一接触区域中、尤其在导体区域处的第二绝缘体层,由此能够提供特别有效的示例性的过程,借助于所述过程能够构造所示出的微机电构件并且能够以特别有效和节省成本的方式进行接触。[0035]根据本发明的实施方式优选可能的是,在第一步骤和第一中间步骤之间实施蚀刻步骤。在该蚀刻步骤中可以蚀刻掉第二绝缘体、第二绝缘体层、第三绝缘体和/或第三绝缘体层的部分。尤其地,这样可能的是,移除围绕微机电元件的绝缘体材料(牺牲氧化物)并且因此露出微机电构件。[0036]根据本发明的实施方式,为了特别有效地避免在能良好导电的、但可能狭长的金属区域和硅区域之间的狭长的过渡区域处的电阻增大,有利地可以考虑,导体区域/导体轨和覆盖层的接触部区域之间的第一接触面(第一接触区域)选择成大于金属材料被引入其中的开口。由此可以增大在狭长的硅通孔和宽的硅导体轨之间的过渡区域中的有效的硅厚度并且在那里局部地减小电阻。替代地或附加地可以考虑,在导体区域下方附加地设置soi层的(绝缘的)附加区域并且使该附加区域与朝着硅导体轨的第二接触区域连接。由此可能的是,通过第二步骤(沟槽步骤)也蚀刻到(附加区域中的)soi材料中。因此,可以使用soi层来局部地减小硅导体轨的电阻。[0037]本发明的另一主题是一种系统,包括根据本发明的实施方式中的任一个实施方式的、用于接触构件、尤其是传感器的电接触部。所述构件尤其是微机电构件,该微机电构件至少基本上构造在soi晶片或soi芯片中。[0038]对于根据本发明的系统,包括根据本发明的实施方式中的任一个实施方式的、用于接触构件的电接触部,以及对于根据本发明的用于制造电接触部的方法,可以使用结合根据本发明的电接触部或根据本发明的电接触部的一个实施方式已描述的特征、构型和优点。[0039]对于根据本发明的电接触部,可以使用结合根据本发明的用于制造电接触部的方法、根据本发明的包括电接触部的系统、根据本发明的用于制造电接触部的一个实施方式或者包括电接触部的系统的一个实施方式已描述的特征、构型和优点。附图说明[0040]在附图中示出并且在下面的说明书中详细阐释本发明的实施例。[0041]图1示出根据本发明的实施方式的用于制造电接触部的方法在第三预步骤之后的示意性示图。[0042]图2示出根据本发明的实施方式的用于制造电接触部的方法在第六预步骤之后的示意性示图。[0043]图3示出根据本发明的实施方式的用于制造电接触部的方法在第一步骤之后的示意性示图。[0044]图4示出根据本发明的实施方式的用于制造电接触部的方法在第一步骤之后并且在蚀刻步骤之后的示意性示图。[0045]图5示出根据本发明的实施方式的用于制造电接触部的方法在第二中间步骤之后的示意性示图。[0046]图6示出根据本发明的实施方式的用于制造电接触部的方法在第二步骤之后的示意性示图。[0047]图7示出根据本发明的实施方式的用于制造电接触部的方法在第三步骤之后的示意性示图。[0048]图8示出根据本发明的另外的实施方式的系统的示意性示图,该系统包括用于接触构件的电接触部。[0049]在不同附图中,相同部件总是设有相同的附图标记并且因此通常分别仅命名或提到一次。具体实施方式[0050]在图1中示出根据本发明的实施方式的用于制造电接触部1的方法在第三预步骤之后的示意性示图。在第二预步骤之前已经在soi晶片5或soi芯片5的硅层20中产生(挖出)结构19。借助于结构19限定微机电构件30的各个部件。在第二预步骤中已经在结构19中沉积第三绝缘体21并且同时在硅层20上方构造有第三绝缘体层22。优选地,第三绝缘体层22和第三绝缘体21相应地由相同的氧化物组成。在第三预步骤中,已经在第二接触区域23中移除绝缘体层22。[0051]在图2中示出根据本发明的实施方式的用于制造电接触部1的方法在第六预步骤之后的示意性示图。在第四预步骤中,首先已经在第三绝缘体层22上施加有导体层4。在此,已经在第二接触区域23中构造有在导体层4和硅层20之间的直接接触。导体层4已经被这样结构化,使得已经构造出导体区域3,该导体区域相对于导体层4的另外的导体区域24借助于第二凹槽布置25隔开。同时也可以进行导体层4的另外的结构化。在第五预步骤中,已经将第二绝缘体层16施加在导体层4上。在此,已经在第二凹槽布置25中布置有第二绝缘体26。因此,第二绝缘体26建立在导体区域3和所述另外的导体区域24之间的电绝缘。最后,在第六预步骤中已经在邻接于导体区域3的第一接触区域12中移除第二绝缘体层16。在此有利地,第一接触区域部分地或完全地与之后构造的开口9(参见图6)重叠。[0052]在图3中示出根据本发明的实施方式的用于制造电接触部1的方法在第一步骤之后的示意性示图。在第一步骤中,已经在第一接触区域12中构造有覆盖层6,使得在第一接触区域12中建立在导体层4和覆盖层6之间的直接接触。此外,已经将覆盖层6施加在第二绝缘体层16上。随后,已经这样结构化覆盖层6,使得构造出接触部区域7,该接触部区域借助于第一凹槽布置8(沟槽)相对于剩余的覆盖层6绝缘。同时,在覆盖层6中已经构造出另外的蚀刻结构化部33,通过所述另外的蚀刻结构化部可以在之后的蚀刻步骤中蚀刻掉位于下方的牺牲氧化物,以便露出构件30。第一凹槽布置8的构造可以与蚀刻结构化部33的构造在同一个步骤中共同进行,由此得出特别成本有效的过程。[0053]在图4中示出根据本发明的实施方式的用于制造电接触部1的方法在第一步骤之后并且在蚀刻步骤之后的示意性示图。在该蚀刻步骤中,在第一步骤和第一中间步骤之间,已经通过蚀刻结构化部33(和第一凹槽布置8)蚀刻掉第二绝缘体26、第二绝缘体层16、第三绝缘体21和第三绝缘体层22的部分。通过移除该牺牲氧化物已经使微机电元件30露出。[0054]在图5中示出根据本发明的实施方式的用于制造电接触部1的方法在第二中间步骤之后的示意性示图。在此,在第一中间步骤中、在第二中间步骤之前,已经将第一绝缘体11(或者说电介质)布置在第一凹槽布置8(和蚀刻结构化部33)中。由此封闭构件30(例如包括谐振器)。有利地,可以同时进行构件30的封闭和凹槽布置8以第一绝缘体11的填充,使得在电接触部1电绝缘时几乎不产生附加耗费(因为构件30典型地本来就必须封闭)。同时,已经将第一绝缘体层17施加在覆盖层6上。在第二中间步骤中,已经在邻接于接触部区域7的第三接触区域18中移除第一绝缘体层17。[0055]在图6中示出根据本发明的实施方式的用于制造电接触部1的方法在第二步骤之后的示意性示图。在第二步骤中已经在接触部区域7中、在导体区域3中并且在附加区域15(硅层20)中构造开口9。在此,开口9已经在同一个步骤中被蚀刻到区域7、3、15中并且基本上垂直于晶片/芯片的表面(或垂直于主延展平面)延伸。开口9这样布置,使得所述开口在覆盖层6内部完全由接触部区域7围绕并且在导体层4内部完全由导体区域3围绕。[0056]在图7中示出根据本发明的实施方式的用于制造电接触部1的方法在第三步骤之后的示意性示图并且因此示出制成的系统40,包括mems构件30和电接触部1。在第三步骤中,已经将金属材料10引入开口9中(也引入接触部区域7、导体区域3和附加区域15中)。在此,金属材料10已经在导体区域3中布置在开口9的侧壁13上并且在接触部区域7中布置在开口9的另外的侧壁14上。因此,在金属材料10和导体区域3之间(或者在金属材料10和接触部区域7之间)存在大的接触面,这特别有利地引起在金属材料10和导体区域3之间的过渡部的电阻的最小化。[0057]特别有利地,根据本发明可以取消(在以金属材料10填充之前、即在第三步骤之前)绝缘体层在开口9中的附加施加以及这种绝缘体层(在开口底部处)的局部移除,因为接触部区域7之前已经相对于剩余的覆盖层6绝缘,并且导体区域3之前已经相对于剩余的导体层4绝缘。[0058]此外,在第三步骤中同时已经施加重布线(umverdrahtung)2,该重布线相应地由与金属材料10相同的材料组成。金属材料10这样布置,使得所述金属材料在重布线2和导体区域3以及附加区域15之间建立具有小电阻的导电连接。此外,导体区域3与mems构件30的部件连接。因此,总体上构造在重布线2和mems构件30的部件之间的电连接,该电连接具有非常低的电阻。[0059]在图8中示出根据本发明的另外的实施方式的系统40的示意性示图,所述系统包括用于接触构件30的电接触部1。与在图7中示出的实施方式不同的是,开口9仅布置在接触部区域7和导体区域3中,而不布置在soi晶片5的硅层20中(或者说不布置在附加区域15中)。这以有利的方式由此实现,不移除在之后的开口9下方的第三绝缘体层22,即不实施第三预步骤并且不构造第二接触区域23。相应地可能的是,在蚀刻步骤中,在第一步骤之后,保留第三绝缘体层22在导体区域3下方的氧化物或材料。这样开口9可以在第二步骤中仅构造在接触部区域7和导体区域3中并且向下通过第三绝缘体层22限界。相应地,金属材料10在开口9中仅构造在接触部区域7和导体区域3中。

本文地址:https://www.jishuxx.com/zhuanli/20240726/122364.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

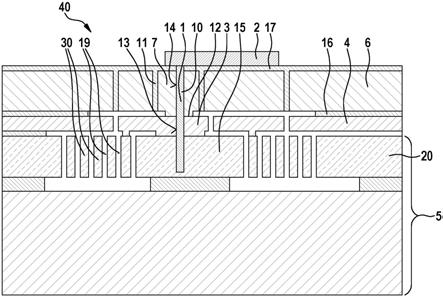

返回列表