适合高密度系统集成的SOCPMUT、阵列芯片及制造方法与流程

- 国知局

- 2024-07-27 12:38:59

适合高密度系统集成的soc pmut、阵列芯片及制造方法技术领域1.本发明涉及高密度单片集成的半导体传感器技术领域,具体涉及3d (3 dimensional)三维pmut架构与soc(system‑on‑chip)集成的新结构及加工技术。背景技术:2.超声诊断仪,通过其超声探头,向人体发射超声波,并利用其在人体器官、组织的传播过程中,由于声的反射、折射、衍射而产生的各种信息,将其接收、放大和进行信息处理,形成图像或血流多普勒,最终在显示器上显示。一台医用彩色超声诊断仪主要包括: 探头、主机、控制面板、显示器及其他附件。3.在人类社会进入大医疗时代,医学超声应用得到快速发展。从医学成像,如胎儿b超,到肝脏,肾脏扫描,超声扫描已遍及全世界。与其他成像技术相比,超声成像技术具有对患者无创无痛苦、实时性好、安全、价格低廉等优点,在预防、诊断、治疗疾病患者中有很高的使用率,广泛应用于消化科、妇科、产科、泌尿 科、胸科、小器官、儿科、心脏科、急诊等多种检临床检查, 且逐渐与其他临床科室结合,发展出消化科(超声内镜)、心 外科(血管内超声)等检查应用,目前超声已是不可或缺的检查方法。4.超声技术与产品正在快速进入人们的日常生活。智能手机是其中一个重要的应用。手机指纹识别不仅快捷,方便,也大大地提高了用户安全性。由于超声传感器具有宽视场,即使安装在手机的顶部或底部仍能够实现精确的距离测量,因此手机设计可以省略手机前面的光学接近传感器,方便实现手机全屏设计。5.汽车中装了超声测距传感器后,能保持驾驶与倒车,停车安全距离,十分方便。进而广之,mems超声波传感器已进入无人机及机器人等应用领域。在这类应用中,微型超声波传感器可以精确地追踪目标,形成阵列空间雷达,实时监测人体移动,位置和动作变化,与vr/ar无缝连接。6.超声波传感器在工业控制中也有广泛应用。例如,探测飞机机翼表面的形状改变,检测是否有结冰,从而影响飞行安全。超声波传感器安装在飞机发动机上,可以实时探测发动机引擎是否有裂纹,及时发现问题,进行维修,替换。7.传统超声探头是用压电陶瓷晶体机械切割、排列、金属互连布线的方法实现的,首先取一块压电陶瓷晶体,固定在支撑衬底上,沿x, y 方向进行机械切割。这种加工方式成品率低,容易造成机械损伤,成本难以管控,很难做到大规模生产。更重要的是,机械加工精度低,最小成品晶体的尺寸受到限制,达不到高分辨率医学成像对pmut日益缩小尺寸的要求。8.基于cmos 工艺的 mems (微机电系统)技术开始受到重视,被视为超声传感器的发展方向。半导体mems 超声传感器得益于cmos工艺的高精度,高成品率,是最有希望实现高分辨率医学超声阵列传感器的技术。但是,目前基于cmos工艺的 mems技术是平面工艺。在超声换能器阵列密度增加时,单元之间的互连,单元与外界互连所需要的金属引线长度与密度快速增加,引线所占用的芯片面积甚至远远超过换能器阵列所占芯片面积,由此也造成封装电路及系统体积的快速增加。此外,由于金属引线的增加,伴随金属引线的电阻,电容延迟效应,电压降,金属引线之间因为耦合而引起的电学干挠等副作用,开始影响换能器的工作性能,并随着阵列密度的增加而愈加严重。9.然而,pmut 的正常工作,需要诸多的辅助电路的支持。图1 是一个典型的pmut 系统的电路框图。不难看出,pmut工作需要有高压(通常10—25伏电压)脉冲驱动电路。高压源电路,它产生并输出直流高压,由脉冲调制电路转换成特定的脉冲驱动信号,通过pmut阵列产生特定频率的超声波发射出去。这是超声的发射过程。10.当超声被扫描物,例如人的不同器官,反射回来时,pmut接收到超声波,并通过压电效应将超声波转化为电学信号,然后输入到低噪声信号放大器,进一步进入可变增益控制电路作信号放大,进而由模拟/数字转换器电路,将模拟信号转化成数字信号,输出到微处理器,再通过超声成像算法形成超声图像。11.不管是在超声发射模式,还是在超声接收模式,pmut都需要多块cmos的模拟,数字电路配合其工作。如果pmut 系统电路框图中的不同电路都由分立的ic 封装电路块完成,实现这一系统将需要多块ic ,在印刷电路板上压焊互连,这一系统会有相当大的体积。对大型的超声系统,例如落地式超声扫描仪,这可能不是问题。但在今天,超声扫描仪的小型化,甚至便携式的呼声日益提高,超声扫描仪必须减小体积。这样的平面架构已不能满足要求。12.mems‑on‑cmos是把mems(micro electrical‑mechanical system)微电机系统传感器做在cmos 芯片上方,实现高密度单片集成的半导体传感器技术。pmut:(piezoelectric micromachined ultrasonic transducers )压电微机械超声换能器,也像其它mems 技术一样,希望借助pmut‑on‑cmos的技术路径,提高集成度,为高分辨率的超声扫描,超声指纹识别等应用提供高密度pmut 阵列。13.pmut‑on‑cmos,如图2(a)所示,可将原来的两个芯片,通过单片集成的方式,垂直叠加起来,从而缩小平面尺寸,减少封装ic的数目,减小系统体积。14.但是,到目前为止,这一看似直接,合理的方案并没有得到广泛采用,主要是因为,在现有平面工艺架构中,要实现pmut‑on‑cmos,会遇到一些新的技术挑战。15.首先, 现有工艺中,pmut阵列必须经过周边压焊块(或小型压焊块)完成pmut阵列与下方cmos电路的互连。其结果是金属布线面临两大限制。第一,如果希望每个单元有自己独立的顶层金属连接,如图2(b)所示,则必须增加额外数量的金属布线。其结果是金属布线降低了pmut单元的占空比(单元中可产生超声的面积与整个单元面积之比),金属布线同时占去阵列之外较大比例的芯片面积,额外金属布线产生的寄生电阻,电容,对速度,功耗等产生不良影响。第二,现今大多数pmut阵列的设计,为减少额外金属布线,由多个同列单元共用同一条顶层金属连线(common column connection),其结果是,这些单元的相互干挠(cross‑talk)变得严重,pmut阵列的主要性能参数,例如有效频率带宽,信噪比等,受到不良影响。16.另外,在cmos上方建造pmut,材料的选择及工艺加工过程都受到一定制约。例如,从材料机械性能,重复性,均匀性考虑,硅材料是很好的pmut的机械衬底层。但在cmos ic上方,由于硅材料生长条件的限制,例如硅外延的温度在1000度以上,根本没有办法在cmos 晶圆上形成单晶硅机械层。17.超声产品往高端发展的需求是无止境的。医学超声成像会要求越来越大的pmut阵列,达到更高的清晰度;指纹识别成像会要求越来多的pmut单元,达到更高的分辨率。但不幸的是,现今的pmut技术,在持续小型化的方向,已经遇到了的瓶颈,需要技术上的突破。18.pmut薄膜压电超声换能器最常用材料有aln (氮化铝) 和 pzt (锆钛酸铅,pb(zrti)o3, 简写pzt)。这些材料及其工艺制程与标准cmos 工艺相比,还有相当程度的差异。例如pzt 材料,必须有特殊的,与cmos工艺不同的,淀积设备,腐蚀与清洗设备,需要相当程度的投资。同时,pzt 材料会对cmos 工艺产生金属污染,影响cmos 产品的性能与可靠性。因此,全球只有为数很少的pmut 工艺生产线。在cmos 工艺基础上添加pmut 工艺,做出高性能,低成本的超声换能器还需要器件结构,工艺流程,系统设计上的不断创造,更新。aln (氮化铝)压电材料与pzt类似,也需要特殊机器设备,有额外的投资需求。19.一个典型的pmut压电超声换能器结构100如图3所示,包括:衬底材料160,一般可以是硅材料或二氧化硅材料,二氧化硅通常也会淀积在硅衬底上。20.空腔120,一般是在衬底材料上腐蚀形成的空腔体,保留空间给pmut 可以上下作机械振动,发射,或接受超声波。21.机械层130, 作为pmut 可振动薄膜的机械支撑,保证pmut 工作寿命。机械层130材质(厚度,比重,杨氏模量等参数)也会影响pmut 振动频率。22.氧化物层132,一般是cmos 工艺过程中在硅表面产生的二氧化硅层。除了对硅表面有保护作用外,氧化物层132 的厚度也会影响pmut 振动频率。23.压电层三明治堆叠结构中包含压电材料层115,被分别安置在所述压电层115下面和上面的相关联的电极层,下部电极112和上部电极114。24.压电材料层115最常用的材料是pzt 锆钛酸铅((pb(zrti)o3, 简写pzt)和氮化铝(aln)。25.pzt对应的下部电极112和上部电极114,通常是铂金pt 材料或铂金与钛金属的多层结构。氮化铝对应的下部电极112和上部电极114,通常是金属钼。下部电极112和上部电极114之间加电压,在压电材料中产生电场,从而引起压电材料的膨胀与压缩,进而产生沿着垂直方向的机械振动,发射超声波。这就是著名的压电效应。26.pmut 机械振动的频率与压电层三明治堆叠结构中各层材料的材质,机械层130,氧化物层132的材质,所有材料的厚度,空腔120的形状与尺寸有关。所有材料的机械应力对振动频率也有影响。27.高分辨率,高集成度的医疗应用pmut 超声探头,需要10‑50mhz兆赫的高频。对pmut 结构100中,不同结构的尺寸大小与其精度控制要求很高,例如空腔120尺寸的大小,空腔120尺寸变化范围的控制直接影响超声探头的工作频率,工作带宽等关键参数。目前常用的从晶圆背面腐蚀,形成空腔120结构的方法,其造成的空腔120结构尺寸的变化可能在5‑10微米,甚至更大。根本达不到高频,高分辨率的要求。同时,从晶圆背面腐蚀,形成空腔120结构的方法,很难做到同时形成不同的空腔120结构尺寸。这就限制了做单片多频超声探头的可能性,在应用上是一大限制。28.与空腔120尺寸的大小,空腔120尺寸变化范围的控制要求类似,pmut压电超声换能器结构100中的薄膜厚度及其控制也是相当关键。例如压电材料层115,机械层130,下部电极112,上部电极114等,其薄膜厚度及其控制,材料的比重,杨氏模量,甚至材料内部的机械应力,都直接影响超声探头的工作频率,工作带宽,超声输出功率,机电耦合系数等关键参数。29.现有 pmut 阵列技术与产品应用中,不管是用晶体切割的方法,还是用mems 半导体 ic 的方法,实现 pmut 与外围电路与系统的电学连接都面临很大挑战。图4是一个典型的pmut阵列芯片的俯视示意图。芯片中心是pmut 7 x 12二维阵列,芯片周边是压焊块,用以实现与电路封装管脚的电学连接。由于阵列中每个pmut单元都必须连接到压焊块,实现电学连接的金属布线都有引线宽度,引线间距的设计规则要求,其结果是,大部分的芯片面积实际被用于金属布线。金属布线所占用的芯片面积远远大于 pmut 阵列所占用的芯片面积,极不经济。同时,较长的金属布线长度,增加了电阻电容的寄生效应,对 pmut 阵列的工作频率,功耗等均有不良影响。布线长短不齐也会直接影响 pmut 阵列工作的均匀性。技术实现要素:30.为了解决现有超声换能器互连的上述缺陷,本发明提出一种具有突破性的3d架构的超声换能器与工艺流程,把pmut阵列,超声换能器高压驱动与控制cmos电路,超声接受的低噪声放大器电路等,垂直堆叠起来,再通过垂直引线孔实现连接,不再通过pmut阵列周边的压焊块实现pmut与cmos的连通,打开了传统超声换能器金属互连的瓶颈,大幅度实现超声换能器阵列的小型化,显著提升芯片集成度。31.为实现上述发明目的,本发明提供了一种适合高密度系统集成的soc pmut架构,pmut阵列堆叠在cmos上方;pmut与cmos的连接通过垂直链接孔,不再通过周边压焊块;cmos不再是单层平面cmos,而是通过混合键合方法,将两片有预制cmos的晶圆堆叠在一起,集成密度加倍;通过tsv,在芯片背面实现与印刷电路板连接。32.本发明实施例提供了一种适合高密度系统集成的soc pmut,其特征在于包括:第一晶圆和第二晶圆,所述第一晶圆布置硅衬底,所述硅衬底上方布置至少一cmos单元,所述至少一cmos单元的金属互连层通过金属引线孔与位于所述金属互连层上方的第二层金属布线垂直互连;所述硅衬底中布置实现所述金属互连层与所述硅衬底背面垂直互连的硅正反面穿孔tsv;所述第一、第二晶圆通过混合键合堆叠,第一、第二晶圆通过布置在两晶圆混合键合界面的键合金属块电学互连;所述第一晶圆混合键合界面布置的键合金属块与所述第二层金属布线电学互连;所述第二晶圆布置所述soc pmut的机械层,所述机械层下方布置至少一空腔体,所述机械层中布置支持所述soc pmut工作的至少一cmos辅助电路,所述cmos辅助电路的金属互连层通过金属互连孔与位于其下方的第二层金属垂直互连;所述第二层金属与所述第二晶圆混合键合界面布置的混合键合金属块电学互连;所述机械层上方布置所述soc pmut的下层金属层、压电材料层和上层金属层,所述cmos辅助电路的金属互连层(301)通过上层金属链接孔ztm与所述上层金属层垂直互连,通过下层金属链接孔zbm与所述下层金属层垂直互连。33.本发明实施例提供了一种阵列芯片,其特征在于包括多个所述的适合高密度系统集成的soc pmut,所述多个soc pmut分别通过所述上层金属链接孔ztm将所述上层金属层垂直连接到所述cmos辅助电路,再通过所述金属互连孔垂直连接到所述第二晶圆的第二层金属,然后通过两晶圆混合键合界面布置的混合键合金属块垂直连接到所述第一晶圆的第二层金属布线,继而分别通过所述两个金属引线孔垂直连接到所述cmos单元的金属互连层,再分别通过所述硅正反面穿孔tsv引到硅芯片背面接到印刷电路板。34.优选地,所述机械层采用与所述硅衬底相同的材料。35.优选地,所述机械层底层布置停止层金属结构,所述上层金属链接孔ztm、下层金属链接孔zbm通过所述停止层金属结构与所述cmos辅助电路的金属互连层电学互连。36.优选地,所述衬底材料在所述第二层金属布线上方还设置了至少一层金属布线,所述至少一层金属布线的各层金属布线通过金属引线孔垂直互连,所述至少一层金属布线的最下面一层金属布线通过金属引线孔与所述第二层金属布线垂直互连,所述至少一层金属布线的最上面一层金属布线与所述第一晶圆混合键合界面布置的键合金属块电学互连。37.本发明实施例还提供了所述适合高密度系统集成的soc pmut的制造方法的制造方法,其特征在于包括如下步骤:步骤1、准备第一晶圆,在表面生长二氧化硅,制作cmos单元;步骤2、在cmos单元上制作pmut单元,并集成cmos辅助电路,具体包括:步骤2‑1、低温淀积衬底材料,化学机械抛光形成平整的衬底材料表面;步骤2‑2、光刻腐蚀、金属淀积填充形成mos电路单元金属互连层与第二层金属布线之间的金属引线孔;步骤2‑3、淀积金属层,光刻腐蚀出第二层金属布线,去胶清洗;步骤2‑4、低温淀积衬底材料,化学机械抛光形成平整的衬底材料表面;步骤2‑5、光刻腐蚀出空腔,去胶清洗;步骤2‑6、准备第二晶圆,在表面生长二氧化硅,制作需要的cmos辅助电路,并与所述第一晶圆完成键合;步骤2‑7、对第二晶圆背面进行研磨、化学液体腐蚀、化学机械抛光减薄厚度;步骤2‑8、金属淀积出下层金属层;步骤2‑9、压电材料淀积出压电材料层;步骤2‑10、顶层金属淀积、光刻腐蚀形成上层金属层;步骤2‑11、光刻腐蚀、金属淀积填充形成金属链接孔;步骤2‑12、金属光刻腐蚀形成所需布线;步骤3、硅衬底反面光刻腐蚀穿通,金属淀积出硅正反面穿孔tsv。38.有益效果:现有 2d 平面超声换能器阵列设计与工艺中,金属布线所占用的芯片面积远远大于超声换能器阵列本身所占用的芯片面积,极不经济。同时,较长的布线长度,对超声换能器的工作频率、功耗、散热等重要指标均有不良影响,布线长短不齐也会直接影响超声换能器阵列工作的均匀性。本发明所提出的超声换能器通过垂直方向的多通道金属连线结构,实现超声换能器与cmos单元三维结构的金属互连,通过 tsv (through silicon via,硅正反面穿孔)延展到封装层面,不再需要通过阵列周边的压焊块与cmos联通,解除了传统超声换能器金属互连的瓶颈,极大地降低了金属互连所占的芯片面积,金属布线的长度减少10—100倍,减少了由此而引起的电学寄生效应对超声换能器阵列性能的不良影响。39.超声换能器阵列工作时,需要脉冲信号产生与控制电路,小信号放大器模拟电路等cmos辅助电路的支持。现阶段,这些辅助电路都采用分立封装,占据较大印刷电路板面积。如果能够把这些电路,部分地或全部地,集成到超声换能器 芯片中,则能够大幅提升系统集成度,对缩小系统体积,实现超声扫描仪的小型化有重大意义。同时,soc系统集成能够大幅提高系统速度,降低功耗。40.为此,本发明把超声换能器阵列的cmos辅助电路,通过有源晶圆堆叠及系统集成的方法,从通常的分立电路,通过金属布线3d垂直互连的方法,堆叠集成到超声换能器3d架构中,形成soc(system on chip)超声换能器的三维架构,把集成度的提升从芯片等级上升到系统等级。41.本发明提出的soc超声换能器3d架构不仅适用于pmut,同样也适用于cmut,尽管本发明具体实施例是针对pmut进行的示例。42.在本发明提出的soc超声换能器的3 d架构下,每一个超声换能器均可具有自己的顶层与底层金属连线,阵列的大小与几何布局可根据不同应用来调节,大大增加了超声换能器阵列工作的灵活性。43.超声系统的小型化,需要超声换能器封装的小型化。在现代半导体封装中,tsv (through silicon via,晶圆正反面通孔)是封装体积小型化的有效方法。本发明在设计超声换能器3d 架构与工艺流程时,充分考虑了3d 架构与tsv 工艺的兼容性。44.本发明所提出的三维架构的soc超声换能器,通过有源晶圆的直接键合,垂直方向的多通道金属连线结构,实现soc pmut 阵列及其cmos辅助电路的垂直堆叠,单片集成,并通过 tsv延展到封装层面,不再需要通过阵列周边的压焊块与cmos联通,解除了传统超声换能器金属互连的瓶颈,极大地降低了超声换能器金属互连所占的芯片面积,同时降低了金属布线的长度,显著降低了芯片尺寸和系统体积,同时减少因为金属布线引起的寄生电阻,电容相关的功耗,延迟,不均匀性,对提高产品性能、降低成本、改善良率等具有显著效益,能实现芯片小型化、高密度系统集成。本发明三维架构的超声换能器的工艺流程与半导体主流工艺、半导体主流设备、现有芯片封装工艺均具有良好的兼容性。本发明可以支持高分辨率医学超声面阵列,实现超声探头一机多频扫描,也非常适合手机指纹识别等高集成度,低成本商业应用。本发明能显著降低芯片及封装系统体积,适合进入人体的小型超声探头设计。附图说明45.图1为pmut 系统的电路框图;图2(a)为现有pmut‑on‑cmos 架构;图2(b)为现有pmut‑on‑cmos 架构金属连线示意图;图3为现有2d pmut 结构示意图;图4(a)为本发明实施例一的pmut结构示意图;图4(b)为本发明实施例一的pmut的局部结构示意图;图5为现有pmut阵列芯片结构示意图;图6为本发明实施例三的pmut阵列芯片结构示意图;图7为cmos单元制作流程图一;图8为cmos单元制作流程图二;图9为cmos单元制作流程图三;图10为本发明实施例四步骤2‑1对应工艺示意图;图11为本发明实施例四步骤2‑2对应工艺示意图;图12为本发明实施例四步骤2‑3对应工艺示意图;图13为本发明实施例四步骤2‑4对应工艺示意图;图14为本发明实施例四步骤2‑5对应工艺示意图;图15为本发明实施例四步骤2‑6第二片晶圆示意图;图16为本发明实施例四步骤2‑6制作cmos电路示意图;图17为本发明实施例四步骤2‑6键合示意图;图18为本发明实施例四步骤2‑7减薄工艺示意图;图19为本发明实施例四步骤2‑8‑步骤2‑10对应工艺示意图;图20为本发明实施例四步骤2‑10形成上层金属工艺示意图;图21为本发明实施例四步骤2‑11 pzt与底层金属刻蚀工艺示意图;图22为本发明实施例四步骤2‑11垂直孔洞刻蚀工艺示意图;图23为本发明实施例四步骤2‑11 ti/tin/al 淀积工艺示意图;图24为本发明实施例四步骤3的示意图。46.图25为本发明实施例的cmos单元放大示意图。具体实施方式47.以下以pmut为例,结合具体实施例对本发明技术方案进一步详细描述。48.实施例一如图4(a), 4(b)所示,本实施例提供一种适合高密度系统集成的 soc pmut,包括第一晶圆和第二晶圆,第一晶圆布置硅衬底材料160、双层金属布线的cmos单元160‑cmos,第二晶圆布置机械层130、下层金属层112、压电材料层115、上层金属层114、空腔体120、双层金属布线的cmos辅助电路300‑cmos。49.硅衬底160上方布置的cmos单元160‑cmos,其金属互连层201两端分别通过两个金属引线孔212与位于金属互连层201上方的两个第二层金属布线202垂直互连。硅衬底160上设置有贯穿整个硅衬底160的两个硅正反面穿孔tsv 162,实现cmos单元金属互连层201两端分别与硅衬底160背面垂直互连,接到背面tsv焊球163‑3,进而可以直接连接到印刷电路板。cmos单元160‑cmos结构如图25所示,属于本技术领域现有技术。50.机械层130中集成有soc cmos电路——cmos辅助电路300‑cmos。cmos辅助电路300‑cmos与其他结构之间的电学互连由cmos辅助电路的金属互连层301(即cmos辅助电路双层金属布线中的第一层金属布线)、第二层金属302(即cmos辅助电路双层金属布线中的第二层金属布线)、金属互连孔312实现,并都连接到垂直引线孔的etch‑stop 303。cmos辅助电路300‑cmos的结构根据具体电路需求设计,其基础结构类似于cmos单元160‑cmos的结构。51.在两晶圆混合键合界面分别布置键合金属块300‑1、300‑2,第一晶圆混合键合界面的键合金属块300‑1与第二层金属布线202连接,第二晶圆混合键合界面的键合金属块与机械层一侧cmos辅助电路第二层金属302连接,并最终与pmut阵列的金属链接孔163‑1、163‑2连接。52.上层金属链接孔ztm 163‑1和下层金属链接孔zbm 163‑2贯穿压电材料层115、下层金属层112、机械层130、氧化物层132,并都连接到停止层金属结构303。 停止层金属结构303是垂直引线孔163‑1,163‑2 刻蚀时利用的etch‑stop金属,材质上停止层金属结构 303 与cmos辅助电路的金属互连层301的金属材质一样。上层金属链接孔ztm 163‑1实现pmut 上层金属层114 与停止层金属结构303,cmos辅助电路300‑cmos 的垂直互连,下层金属链接孔zbm 163‑2实现下层金属层112与停止层金属结构303,cmos辅助电路300‑cmos 的垂直互连。53.因为上、下层金属链接孔经过高度不同的 pmut 顶层金属tm,压电材料 pzt,再垂直连接,其剖面形状近似z字型,故称z型孔。z型孔可以实现超过两个结点的电学连接,例如,上层金属链接孔ztm 163‑1实现上层金属层114与停止层金属结构303,cmos辅助电路300‑cmos垂直互连的同时,可以连接其它邻近pmut的上层金属。54.本实施例的适合高密度系统集成的pmut超声换能器,利用cmos金属互连层作为第一层金属布线,与第二层金属布线一起构成双层布线设计,不仅能够实现与cmos互连,还提供了双层金属布线密度,显著增加了 pmut阵列的互连性,可以实现多个超声换能器的串并联,为pmut 阵列设计提供了很多灵活性,同时大大减小金属布线的长度与占用面积,从而显著减小芯片面积。55.图中铝金属tsv pad 162‑2是cmos制程中需要特殊设计的铝结构,它构成tsv刻蚀的停止层金属结构,帮助 tsv 刻蚀停止在特定位置,同时形成tsv与其它cmos电路的电学连接。该结构可与cmos单元的金属互连层作为一个整体设置,也可单独设置并与cmos单元的金属互连层互连。56.图中键合金属块300‑1、300‑2分别位于衬底材料160侧和机械层130侧,是为了满足制造方法流程中晶圆键合的工艺需要而设置,通过键合金属块300‑1、300‑2的连接,实现晶圆与晶圆之间的电学连接,进而通过金属布线与金属链接孔,实现pmut阵列与tsv焊球从上到下的垂直连接。57.本实施例的适合高密度系统集成的pmut超声换能器,通过垂直走向的金属链接孔将压电层三明治堆叠结构中的金属电极垂直互连到第二层金属布线,再通过垂直走向的金属引线孔垂直互连到第一层金属布线(cmos单元的金属互连层),然后通过硅正反面穿孔tsv互连到硅芯片背面。采用上述垂直布线设计,可以把现有平面 pmut的压焊块及金属引线大部分省略,由垂直方向引向晶圆背面,实现了金属连线由 2d(二维)平面布线向 3d(三维)的过渡,可以显著减小芯片以及封装体积。58.本实施例的适合高密度系统集成的soc超声换能器,把超声换能器阵列的cmos辅助电路,从通常的分立电路,通过金属布线3d垂直互连的方法,单片集成到超声换能器3d架构中,形成soc(system on chip)的三维架构,在提升芯片集成度的同时,大幅提升系统集成度,把集成度的提升从芯片等级上升到系统等级,实现了系统级的小型化。59.实施例二本实施例提供一种适合高密度系统集成的soc超声换能器,与实施例一的架构相似,考虑soc pmut的整体设计,当分辨率要求较高,需要较大规模的阵列时,互连的实现可能需要多层布线。例如,当把人工智能算法也放进 soc pmut 超声设计时,cmos ic设计可能需要5—6 层金属布线。本发明工艺流程中,已特别考虑布线架构,工艺流程在布线层数上有很大弹性。因此本实施例在实施例一的基础上,在所述第二层金属布线的上方还设置了至少一层金属布线,所述至少一层金属布线的各层金属布线通过金属引线孔垂直互连,所述至少一层金属布线的最下面一层金属布线通过金属引线孔与所述第二层金属布线垂直互连,所述至少一层金属布线的最上面一层金属布线与所述第一晶圆混合键合界面布置的键合金属块300‑1电学互连。所述至少一层金属布线的每一层也分成两个金属布线,同层的两个金属布线分别通过两个金属引线孔与下一层的两个金属布线垂直互连。60.当cmos电路需要更小尺寸时,例如90纳米,金属可以由铝改为铜。这些在cmos范畴有标准做法去涵盖,在这就不去进一步阐述。61.实施例三本实施例提供一种垂直方向电学互连来取代传统平面布线方式,制作所述的适合高密度系统集成的超声换能器。soc pmut超声换能器分别通过所述上层金属链接孔ztm 163‑1将所述pmut上层金属层114,垂直连接到停止层金属结构303,及相应的cmos辅助电路300‑cmos第二层金属302;通过所述下层金属链接孔zbm 163‑2将所述下层金属层112,垂直连接到停止层金属结构303,及相应的cmos辅助电路300‑cmos第二层金属302,继而通过所述两个金属引线孔312垂直连接到cmos辅助电路300‑cmos中的任意器件。通过合理布线,可实现多个超声换能器的串、并联。62.cmos辅助电路300‑cmos经过键合金属块300‑1,300‑2可以连接到第一晶圆中的cmos单元160‑cmos, 再通过所述硅正反面穿孔tsv 162连接到硅芯片背面,继而连接到印刷电路板,实现电学互连。63.本实施例通过垂直方向电学互连,将pmut阵列,cmos高压辅助电路芯片,第二个cmos低噪声放大器控制器芯片,以及tsv等四层结构垂直叠加在一起,相比较传统平面工艺方式,本实施例极大地减小了芯片尺寸与系统体积。64.如图5所示,现有 pmut 阵列芯片产品,芯片中心是 pmut 二维阵列,芯片周边是压焊块,用以实现与电路封装管脚的电学连接以及与cmos辅助电路的压焊块的连接,现有pmut 阵列芯片与外围电路电学连接时,需要布置高密度的引线,每一根金属布线都有引线宽度,引线间距在设计规则下的尺寸要求,其结果是,大部分的芯片面积被用于金属布线,而不是有源pmut阵列本身,金属布线所占用的芯片面积远远大于 pmut 阵列所占用的芯片面积。如图6所示为采用本发明超声换能器构成的“7 x 12阵列”的芯片布局布线,采用本发明 3d 结构的超声换能器,不再需要通过阵列周边的压焊块与cmos连通,与现有的平面pmut‑on‑cmos互连架构相比,极大地降低了金属互连所占的芯片面积和布线长度。65.实施例四本实施例提供实施例一的适合高密度系统集成的pmut超能换能器的制造方法,工艺流程包括三个部分。66.第一部分为 cmos 电路的工艺流程,例如 pmut 脉冲产生与控制电路的工艺流程,该部分可以采用业界标准流程,但同时需要考虑与3d pmut工艺,与3d tsv (through silicon via,硅正反面穿孔)工艺的整体兼容。67.第二部分,首先根据 soc 电路框图的分工,在第二片晶圆上进行所选择的 cmos 电路的制作。视soc要求而定,第二片晶圆所采用的cmos制程与第一片晶圆可能完全不同;下一步进行晶圆与晶圆的键合,减薄。其后是pmut 3d 阵列的工艺流程,其中包括pmut单元的制作,金属互连,晶圆与晶圆之间的特殊互连等。本实施提出的soc pmut 结构,基于混合键合(hybrid bonding)技术。hybrid bonding的键合界面主要还是二氧化硅oxide,但也有金属结构(300‑1)在晶圆1一侧,和金属结构(300‑2)在晶圆2一侧。晶圆键合的界面同时有氧化硅‑氧化硅界面与金属‑金属界面,在氧化硅实现键合的同时,当二氧化硅以fusion bond 键合到一起时,两片晶圆通过界面金属结构300‑1、300‑2实现电学连接。键合界面由oxide与金属混合形成,故名混合键合,hybrid bonding。68.第三部分为 3d tsv (through silicon via,硅正反面穿孔)工艺流程,重点是 tsv 怎样与 3d 架构整合,成为soc整体工艺的一部分。69.实际上,整个工艺流程的三大部分不是截然分开的,三大工艺部分彼此融合,整体优化。例如,空腔体的形成,实际上是cmos工艺的一部分。而 tsv 所需要的铝金属着落层(landing pad)也是在cmos 工艺中形成的。这是统筹设计的结果。70.具体包括如下步骤:步骤1、准备第一晶圆,在表面生长100纳米左右的二氧化硅形成硅衬底,在硅衬底上制作cmos单元。cmos电路工艺如图7‑9所示,采用业界标准流程实现。如图7包括如下步骤,(a)准备初始材料p型硅,(b)形成二氧化硅缓冲层,(c)光刻胶涂敷,(d)n型井刻蚀,(e)腐蚀n‑井二氧化硅层,(f)、(g)扩散或离子注入形成n‑井,(h)去除二氧化硅缓冲层。如图8进一步包括如下步骤,(a)晶体管栅氧化、多晶硅淀积,(b)多晶硅栅光刻、腐蚀,(c)光刻胶涂敷,(d)n + 源/漏区、n‑井连接区光刻,(e)源/漏区离子注入,(f)去除光刻胶。如图9进一步包括如下步骤,(a)p+ 源/漏区、 p‑忖底连接区形成(经过光刻,离子注入,去胶,褪火工艺等),(b)ild 电学隔离层形成,包括非掺杂二氧化硅淀积、掺杂二氧化硅淀积、回流、contact 金属接触孔光刻、腐蚀等步骤,(c)金属互连层形成,包括接触金属溅射、铝金属淀积、金属层光刻、腐蚀、去胶等步骤。71.soc整体设计中,当分辨率要求较高,需要较大规模的阵列时,互连的实现可能需要多层布线。例如,当把人工智能算法也放进 pmut‑on‑cmos 超声设计时,cmos ic设计可能需要5—6 层金属布线。本发明工艺流程中,已特别考虑布线架构,工艺流程在布线层数上有很大弹性。72.步骤2、在cmos单元上进一步制作pmut单元,并集成cmos辅助电路,具体包括:步骤2‑1、如图10,首先要指出在设计中需要特别考虑的结构停止层金属结构303,它在混合键合工艺中,是结构163‑1、结构163‑2的干法腐蚀的停止层金属结构(drie etch‑stop layer)。但在工艺中,金属结构303实质上是cmos第一层金属布线的一部分。cmos电路的金属介质隔离层 imd (inter‑metal dielectric)通过淀积800纳米左右的二氧化硅( sio2),然后进行cmp (chemical mechanical polish),形成平整的sio2 表面,利于后续光刻涂胶等工艺;步骤2‑2、如图11,光刻形成金属布线层之间的金属引线孔 via, 等离子干法腐蚀形成via孔,去胶,清洗,再进行金属钛/氮化钛溅射,热衬底金属铝淀积填满 via 互连孔(如果via孔较小,可以用金属钨的化学气相淀积取代铝,做via孔);接着淀积金属层,光刻腐蚀出第二层金属布线,去胶清洗;低温淀积sio2衬底材料,化学机械抛光形成平整的衬底材料表面;低温二氧化硅 sio2 淀积(等离子增强化学气相淀积,pecvd)温度在250—300度,sio2 厚度在 3 微米左右。然后进行化学机械抛光,形成平整的sio2 表面。配合 pmut‑on‑cmos 的特殊工艺步骤, 我们在介质层(类似于cmos工艺中的钝化层)中引入二氧化硅‑氮化硅‑二氧化硅夹层结构,在需要形成空腔体120的部分,在空腔体底部二氧化硅下方淀积一层氮化硅,二氧化硅的腐蚀速度远高于氮化硅腐蚀速度,从而很容易采用二氧化硅干法腐蚀,腐蚀停止在氮化硅层,这种做法形成空腔体,能精确控制空腔体的深度,有利于实现器件小型化。73.步骤2‑3、如图12, 光刻腐蚀二氧化硅空腔体:涂敷光刻胶,光刻形成空腔体 cavity 图形,等离子化学气相腐蚀sio2,形成空腔体,深度在 2 微米左右。然后去胶,清洗。74.步骤2‑4、如图13,光刻腐蚀形成混合键合所需要的键合金属块300‑2,涂敷光刻胶,光刻形成图形,等离子化学气相腐蚀sio2,直至第二层金属铝。然后去胶,清洗。所形成的键合金属块300‑2的小孔深度较浅,在0.2‑0.3微米。75.步骤2‑5、如图14,通过金属淀积与cmp的方法,形成300‑2金属小块(mini‑pad)。相同的方法,在另一晶圆上也形成300‑1mini‑pad。 两片晶圆上的mini‑pad 的位置是精确设计的,在晶圆键合时,键合金属块300‑1与300‑2能形成对接,互连。76.步骤2‑6、如图15‑17,准备第二片晶圆,在表面生长100纳米左右的二氧化硅形成硅衬底,在硅衬底上制作需要的cmos电路,并与所述第一晶圆完成键合。cmos电路制作工艺同步骤1,采用业界标准流程实现。77.在准备第二片晶圆时,有一些特殊的考虑。晶圆初始材料,starting material,是p‑/p+ 外延片。外延层的厚度与pmut 机械层最后厚度要求相关。 p‑/p+ 层的浓度差希望在一个数量级以上,便于化学减薄时能够较好控制剩余晶圆的厚度。78.当cmos制程完成后,根据空腔体深度的设计要求(由压电材料最大的垂直方向位移决定),决定是否调整 sio2 的厚度,光刻腐蚀sio2 空腔体,达到不同的空腔体深度。79.本实施的一个特别的优点是,可以在键合前,在两个晶圆上分别形成空腔体,键合后会有两个空腔体。对准的两个空腔体合二为一,结合后的空腔体有较大的深度,可以输出更大功率的超声。对于一般应用,单一空腔体的设计就能满足要求,不必设计多个空腔体。从soc设计的角度,空腔体放置在机械层一侧为佳。简单起见,后面的工艺流程中仅描述单一空腔体,空腔体布置在机械层。80.半导体业界最近开发了混合界面键合技术:hybrid bonding。这一技术在键合界面,存在少部分的金属(键合金属块300‑1、300‑2),例如金属铜cu。在晶圆一与晶圆二键合时,大部分的二氧化硅实现键合的同时,键合金属块300‑1、300‑2对准接触,cu与 cu之间也实现了电学连接。81.本实施例中,我们首次将hybrid bonding技术用于pmut应用,并采用 soc方案将其技术潜力极大地发挥出来。对sio2表面进行等离子处理后,将晶圆sio2面对面,对准,加压加热,褪火,完成二氧化硅之间的fusion bonding的同时,实现金属300‑1,300‑2的连接,完成混合键合,hybrid bonding。82.混合界面键合hybrid bonding技术的优点是,键合的同时就实现了两片晶圆之间的电学互连,不再需要较大深度的z型金属连接孔的刻蚀。工艺相对简单,便捷。但是,hybrid bonding 对键合界面的平整度要求很高,当oxide 与 cu之间有哪怕小于一纳米的微小台阶时,键合也可能出现电学连接可靠性问题。83.步骤2‑7、如图18,键合完成后,在第二片晶圆背面进行研磨,将厚度减薄到小于100微米。然后进行化学液体腐蚀,进一步减薄晶圆到5—8微米,最后进行化学机械抛光cmp (chemical mechanical polishing),剩余晶圆厚度在 2‑5 微米。84.业界在机械层130结构部分,常用的材料是氧化硅,氮化硅,多晶硅,或者是其多层薄膜组合。所有这些材料都不是单晶材料,换言之,由于分子结构的杂序形态,这些材料的机械性能参数,以及薄膜中的机械应力,都会受到工艺制作条件的影响,可控性与制造重复性都存在问题。更头疼的是,杂序形态的薄膜,由于内部剩余应力,以及表面电荷的影响,pmut 薄膜初始状态不是水平的,甚至有粘连状态。本实施例提出的晶圆键合与减薄的方法,把硅单晶体引入机械层,由于硅是高质量,高强度的单晶体,机械层的机械参数重复性最佳,内部机械应力也降到最低,均匀性,制造重复性好。导电的硅材料,也能有效释放电荷,减少粘连。85.步骤2‑8、如图19,金属淀积出下层金属层:采用钛金属 ti 与铂金 pt 的多层结构,厚度分别是20纳米和100纳米。钛金属ti增加了金属层与硅及氧化硅的粘附性,铂金 pt则是最好的导电层之一,可提高压电效率。ti 金属用溅射方法形成,而铂金 pt则采用大电流高温电子枪,在真空中蒸发形成。86.步骤2‑9、如图19,压电材料淀积出压电材料层;压电材料,可以是pzt, 或者是aln 等其它压电材料。这里我们以pzt为代表做叙述。pzt淀积:通过溅射方法形成,pzt (锆钛酸铅,pb(zrti)o3,简写pzt),是事先按特殊的原子比例混合准备好的固体靶材。在高真空下,高电压产生的等离子体将 pzt 靶材溅射,淀积到晶圆表面。溅射同时,硅衬底施加一定温度让pzt再结晶,形成所需要的压电晶体。pzt 淀积的厚度在1 微米左右。aln 材料也是由溅射方法形成,溅射时工作温度可以更低(小于400度,甚至更低),对后续工艺集成中减少温度对既有金属的影响更有利。87.本实施例中针对pzt描述工艺细节。就器件及工艺架构而言,作适当调整,本实施完全适用于氮化铝pmut。本实施的架构也能够适用于cmut的soc设计,达到与pmut类似的性能提升。88.步骤2‑10、如图20,顶层金属淀积、光刻腐蚀形成上层金属层; pzt顶层金属淀积也采用铂金 pt, 其厚度在100纳米,0.1微米。铂金 pt是惰性金属,比较难用液体腐蚀的方法成形,本实施例采用等离子干法气相腐蚀方法的方法刻蚀顶层金属。89.步骤2‑11、如图21‑23,光刻腐蚀、金属淀积填充形成金属链接孔;因金属链接孔采用z型孔,首先进行pzt刻蚀,仅腐蚀pzt,如图21区域13, pzt 刻蚀采用国际先进的氯化氢氟化氢等离子干法气相腐蚀方法,该方法不仅腐蚀均匀性好,腐蚀后 pzt 材料的边缘整齐,并有一定的斜坡,方便后续工艺步骤。aln 材料的刻蚀可以用磷酸,或者对应的等离子干法腐蚀,工艺过程需要相对调整。然后腐蚀pzt与底层金属,如图21区域14,该步骤同时进行 pzt 和下层金属的刻蚀,采用等离子干法气相腐蚀。如图22,再光刻腐蚀z型孔垂直孔洞zia,3d 垂直方向电学连接的关键结构之一,就是形成z型孔垂直孔洞zia,其作用是把pmut 的上层金属层、下层金属层在垂直方向连接到停止层金属结构303,再通过cmos辅助电路的第一层金属布线301,金属引线孔321,第二层金属布线302等,连接到电路的其它部分。 形成zia光刻孔后,继续腐蚀机械层、二氧化硅层,停止在停止层金属结构303,去胶,清洗。如图23,表面绝缘处理,用溅射方法清理连接孔底部后,接着采用ti/tin/al 淀积,其中ti/tin 采用溅射方法形成,铝采用热衬底淀积方法,以提高铝金属填充,进入zia 孔洞。最后金属光刻腐蚀形成所需布线;当zia尺寸较小(<1微米)时,可以cvd 钨代替铝,更好地填入zia。90.步骤2‑12、金属光刻腐蚀形成所需布线;步骤3、如图24,硅衬底正反面光刻腐蚀穿通,金属淀积出硅正反面穿孔tsv。具体包括如下步骤:(a)pmut 晶圆正面保护:形成空腔,盖玻璃保护层(b)硅衬底研磨减薄(c)压焊块,划片槽选择刻蚀减薄(d)背面金属层(e)激光打孔至压焊块(f)溅射 (ti/cu) ,镀铜(g)刻蚀背面布线(h)镀镍金 (ni/au),刻蚀球焊区(i)形成背面球焊阵列。91.本实施例以铝金属tsv pad 162‑2 做 tsv 腐蚀的停止层金属结构 (etch stop landing pad),利用tsv焊阵列实现 soc pmut 阵列直接焊接到印制电路板上,体积小,外部引线少,对系统小型化很有帮助。92.至此,通过两片有预制cmos电路的有源晶片的键合,金属链接孔垂直方向连接,多层金属布线增加布线效率,tsv 将金属互连从晶圆正面引到背面,本实施例完成了适合高密度系统集成的 pmut soc 单元的所有制造工艺制程完成,最大程度降低了金属布线所占芯片面积,减小了芯片尺寸,减小系统体积。93.本实施例的pmut soc 单元的制造工艺流程与半导体主流工艺与设备兼容,垂直方向连线与现有芯片bga(ball grid array)封装工艺兼容,具有广泛的适应性。94.如何有效地将超声换能器工作的cmos辅助电路集成于soc三维架构,需作以下的考虑:由于pmut需要高压脉冲控制信号产生超声信号,因而从系统集成角度,让高压脉冲控制信号电路与 pmut 单片/阵列集成在同一晶圆上,实现最近距离互动较为合理。同理,辅助高压脉冲电路的部分,如高压源电路,脉冲调制电路等也应该放在同一块晶圆上。95.当 pmut 接受到超声波,并将其转化成电学信号时,需要经过模拟小信号放大器,增加信号幅度,降低噪声。再经过可变增益控制电路进一步提高信噪比。换句话讲,超声的接受与放大,所需要的cmos电路与超声发射所需要的高压脉冲电路完全不同,从soc 系统分类的角度,将超声接受及其信号放大的相关电路放在同一晶圆上较为合理。96.在做soc 系统分类时,一个考虑的重点是cmos工艺的综合流程互补性,全局成本。首先,应该尽可能将工艺流程相近,设计规则相近的电路放在同一晶圆上面。例如,高压脉冲电路,产生高压的源电路,高压调整电路等,通常都用设计规则较大的cmos工艺。高压电路所需要用到的晶体管,一般也需要较大的几何尺寸,来保证有足够的击穿电压。另一方面,高信噪比的模拟放大器,利用设计规则较小的先进制程较容易实现,高分辨率的模拟‑数字转换器也需要先进工艺制程,将需要先进制程的设计放置在同一晶圆较为合理。97.同时, 在先进制程上做高压器件相对成本比较高。在同一个cmos制程中同时使用高压,电压电路,需要较复杂的工艺制程,也需要较多的光罩层数。最终导致芯片成本较高,产品的良率因工艺复杂也相应降低。98.在做 soc 系统分类时,需要考虑的因素与系统集成的内容紧密相关。99.本发明的最大收益者将是智能型超声扫描仪。尤其是添加了人工智能功能的便携式扫描仪。

本文地址:https://www.jishuxx.com/zhuanli/20240726/122932.html

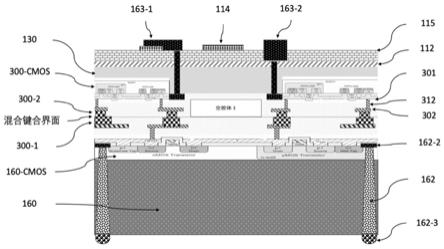

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。