一种MEMS器件的应力缓冲封装结构的制作方法

- 国知局

- 2024-07-27 12:44:51

一种mems器件的应力缓冲封装结构技术领域1.本发明涉及芯片封装技术领域,更具体地说,它涉及一种mems器件的应力缓冲封装结构。背景技术:2.mems器件中诸如陀螺仪、加速度计、谐振器等对机械应力非常敏感,原因是应力可以改变mems敏感结构的刚度以及谐振频率,使得敏感结构与外界应力或热应力之间形成我们不期望的耦合作用,因而如何降低mems器件本身的内部应力并降低外界应力对mems器件的影响是提高mems器件性能的关键。3.封装应力主要来源于mems芯片与封装材料之间因热膨胀系数不匹配而产生的热应力,外界应力主要来自mems器件的smt以及机械振动、机械冲击导致的pcb载体应力状态发生变化。这些应力最终会传递至mems芯片,造成mems芯片产生不正常形变,表现为mems传感器零位和刻度因子的漂移,更严重的导致mems器件功能性失效。4.现有降低或隔离应力采用的方法大多以增加封装结构的局部柔性实现在应力传递路径上对本应传递至mems芯片的应力进行释放,一般有以下方法:1)采用低杨氏模量的软胶粘接mems芯片,将应力在软胶层基本释放掉,杨氏模量越小应力释放效果越好;2)采用单点或单边支撑的悬梁结构粘接或固定mems芯片在底层结构上,可以释放绝大部分从基层结构上传的应力,例如cn201410306360、cn112225168a、cn110546516a等专利中所示;3)在mems芯片与底层结构之间增设柔性平台,柔性平台一般通过多个支撑梁悬挂支撑在底层结构上,起到应力隔离作用,例如cn201911000389.9、ep1571454b1等专利中所示。5.虽然上述方法可以较好的隔离应力,但也存在结构强度低或是刚性低的不足,不适用于抗高过载应用。技术实现要素:6.针对现有技术存在的不足,本发明的目的在于提供一种mems器件的应力缓冲封装结构,其通过在应力缓冲垫板的正面形成三维化图形特征,不仅能够实现mems芯片的粘接固定,大幅度减小mems芯片与封装管壳之间的应力耦合,而且能够给mems芯片提供足够的粘片强度,大幅改善粘片胶及粘片胶应力的一致性。7.为实现上述目的,本发明提供了如下技术方案:一种mems器件的应力缓冲封装结构,包括封装管壳和mems芯片,所述封装管壳内固定设置有用于承载所述mems芯片的应力缓冲垫板,所述应力缓冲垫板与mems芯片之间设置有粘片胶;所述应力缓冲垫板包括基片,所述基片上与所述mems芯片相对的端面设置有至少两个高度不相同的凸出部。8.进一步地,所述凸出部包括凸台和凸点,且所述凸点的高度大于所述凸台的高度。9.进一步地,所述基片上设置有多个凸点圈,所述凸点圈由一个或者多个分布于圆形区域内的所述凸点组成。10.进一步地,所述基片上设置有四个所述凸点圈,且四个所述凸点圈分别设置于所述基片的四个顶角处;所述凸台设置于所述基片的中心。11.进一步地,所述基片上设置有三个所述凸点圈,所述凸台与三个所述凸点圈分别设置于所述基片的四个顶角处。12.进一步地,所述粘片胶同时覆盖所述基片、凸台和凸点圈来形成整面粘接,或者所述粘片胶覆盖多个所述凸点圈来形成多点粘接,或者所述粘片胶覆盖所述凸台以及多个所述凸点圈来形成多点粘接,或者所述粘片胶覆盖所述凸台来形成单点粘接。13.进一步地,所述mems芯片与凸点抵接。14.进一步地,所述基片的厚度为100μm~1000μm,所述凸台与基片的高度差为30μm~200μm,所述凸点与凸台的高度差为5μm~30μm。15.进一步地,所述凸点的直径为10μm~50μm,形成所述凸点圈的圆形区域的直径为300μm~900μm。16.进一步地,所述应力缓冲垫板的材料是硅,采用深反应离子蚀刻工艺多次蚀刻后一体成型。17.综上所述,本发明具有以下有益效果:1、在应力缓冲垫板的正面形成三维化图形特征,不仅能够实现mems芯片的粘接固定,大幅度减小mems芯片与封装管壳之间的应力耦合,而且能够给mems芯片提供足够的粘片强度,大幅改善粘片胶及粘片胶应力的一致性;2、具有三维化图形特征的应力缓冲垫板可以固定粘片胶至特定的形貌,该特定的形貌可以使封装结构能够较好释放封装应力的同时兼具较高的粘片强度。附图说明18.图1为实施例1中一种mems器件的应力缓冲封装结构的结构示意图;图2为实施例1中封装管壳的结构示意图;图3为实施例1中应力缓冲垫板的结构示意图一;图4为实施例1中应力缓冲垫板的结构示意图二;图5为实施例2中应力缓冲垫板的结构示意图;图6为实施例3中一种mems器件的应力缓冲封装结构的结构示意图;图7为实施例4中一种mems器件的应力缓冲封装结构的结构示意图;图8为实施例5中一种mems器件的应力缓冲封装结构的结构示意图。19.图中:1、封装管壳;11、封装底板;12、第一台阶层;13、第二台阶层;14、内焊盘;15、密封腔;2、封装盖板;3、第一粘片胶;4、应力缓冲垫板;41、基片;42、凸台;43、凸点圈;431、凸点;5、第二粘片胶;51、凸台粘胶点;52、凸点圈粘胶点;6、mems芯片;7、金属线;8、第三粘片胶;9、asic芯片。具体实施方式20.以下结合附图对本发明作进一步详细说明。21.本具体实施例仅仅是对本发明的解释,其并不是对本发明的限制,本领域技术人员在阅读完本说明书后可以根据需要对本实施例做出没有创造性贡献的修改,但只要在本发明的权利要求范围内都受到专利法的保护。22.实施例1:一种mems器件的应力缓冲封装结构,参照图1至图4,其包括封装管壳1和mems芯片6,封装管壳1内固定设置有用于承载mems芯片6的应力缓冲垫板4,应力缓冲垫板4与mems芯片6之间设置有粘片胶;应力缓冲垫板4包括基片41,基片41上与mems芯片6相对的端面设置有至少两个高度不相同的凸出部;基片41与至少两个高度不相同的凸出部配合,使得应力缓冲垫板4的正面形成三维化图形特征,该特征用以固定粘片胶至特定形貌,不仅能够实现mems芯片的粘接固定,大幅度减小mems芯片与封装管壳之间的应力耦合,而且能够给mems芯片提供足够的粘片强度,大幅改善粘片胶及粘片胶应力的一致性。23.参照图1和图2,本实施例中封装管壳1的作用是提供密封腔并引出电信号,封装管壳1可以是陶瓷管壳、金属管壳或者塑料管壳,在此不做限制;具体地,本实施例中封装管壳1为陶瓷管壳,其包括封装底板11、第一台阶层12以及第二台阶层13,第一台阶层12上设置有内焊盘14;mems芯片6与内焊盘14之间通过金属线7连接引出电信号,第二台阶层13上焊接有封装盖板2,使得封装管壳1内形成密封腔15;mems芯片6置于密封腔15内,能够对mems芯片起到保护作用;具体地,本实施例中第一台阶层12的厚度为0.3mm~2mm,第二台阶层13的厚度为0.2mm~1mm;对于第二台阶层13,其表面可以制作金属化图案,用于与封装盖板2的合金焊料进行金属熔融封盖,也可以制作可伐合金环,用于与封装盖板2进行平行缝焊,在此不做限制。24.参照图1至图4,本实施例中凸出部包括凸台42和凸点431,且凸点431的高度大于凸台42的高度;具体地,本实施例中mems芯片6安装到位后与凸点431接触,即较高的凸点431对mems芯片6起到支撑和定位作用,而凸台42与mems芯片6之间存在间隙;在其他可选的实施例中,基片41上也可以设置三个或者更多不同高度的凸出部,在此不做限制。25.参照图1至图4,优选地,本实施例中基片41上设置有多个凸点圈43,凸点圈43由一个或者多个分布于圆形区域内的凸点431组成;具体地,本实施例中凸点圈43内设置有三个凸点431,且三个凸点431围绕圆心沿周向均布设置;采用凸点圈43,一方面能够提高对mems芯片6的支撑强度,并大幅改善粘片胶及粘片胶应力的一致性,另一方面能够提高mems芯片的粘接稳固性,大幅减小mems芯片与封装管壳之间的应力耦合;当然,在其他可选的实施例中,凸点圈43的多个凸点431的分布区域也可以为三角形、方形或者其它形状,在此不做限制。26.参照图1至图4,优选地,本实施例中基片41上设置有四个凸点圈43,且四个凸点圈43分别设置于基片41的四个顶角处,而凸台42设置于基片41的中心;采用上述的布局方式,有利于提高支撑强度和应力释放的均匀性;当然,凸台42以及多个凸点圈43的布局方式可以根据需要进行调整,在此不做限制;凸台42的截面形状可以为圆形、矩形或者正多边形等,具体地,本实施例中凸台42的截面形状为矩形;本实施例中基片41的截面形状同样为矩形,且凸台42的面积为基片41面积的1/50~1/10,而基片41面积与mems芯片6的面积相等,从而有利于兼顾应力缓冲/释放效果以及粘接强度。27.参照图1至图4,优选地,本实施例中基片41的厚度为100μm~1000μm,凸台42与基片41的高度差为30μm~200μm,凸点431与凸台42的高度差为5μm~30μm;即,凸点431与凸台42之间形成第一高度差,凸台42与基片41之间形成第二高度差,上述两个高度差使得应力缓冲垫板4的正面形成三维化图形特征;优选地,本实施例中凸点431的直径为10μm~50μm,形成凸点圈43的圆形区域的直径为300μm~900μm。28.参照图1至图4,本实施例中应力缓冲垫板4的材料为硅,其采用深反应离子蚀刻工艺多次蚀刻而成,使得应力缓冲垫板4一体成型;具体地,可取双抛硅片,通过第一次涂胶、曝光、显影等步骤将设计好的凸点图形转移至硅晶圆正面的光刻胶上,通过第一次深反应离子刻蚀(drie)将凸点图形以外区域下刻5μm~30μm,形成第一高度差,去胶后进行第二次喷胶、曝光、显影等将凸点图形和凸台图形转移至光刻胶,再进行第二次drie将凸点和凸台图形以外区域下刻30μm~200μm,形成第二高度差,至此完成硅片正面三维化图形的加工,最终切割晶圆即可得到应力缓冲垫板4。29.参照图1至图4,本实施例中应力缓冲垫板4与封装管壳1之间通过第一粘片胶3进行固定,而mems芯片6与应力缓冲垫板4之间通过第二粘片胶5进行固定;优选地,第一粘片胶3采用高杨氏模量、热良导体的粘胶,例如环氧导电银浆,将应力缓冲垫板4整面粘接至封装底板11上,使得封装结构具备足够的基础粘片强度和较低热阻;本实施例中第二粘片胶5采用低杨氏模量粘胶,例如硅胶,在粘接好的应力缓冲垫板4上涂覆若干点状粘胶,点状粘胶的高度应高于凸点431,将mems芯片6放置在应力缓冲垫板4上并施加一定压力使得mems芯片6背面与应力缓冲垫板4上的凸点431接触,以此固定mems芯片6的位置,而凸点431在后续引线键合等工序中还起到对mems芯片6的支撑作用;第二粘片胶5固化后实现mems芯片6背面与应力缓冲垫板4正面的整面粘接,第二粘片胶5的形貌由应力缓冲垫板4的三维化图形特征决定,即凸台42处的胶厚等于应力缓冲垫板4的第一高度差,凸台42以外区域的胶厚等于凸点431高度(第一高度差与第二高度差之和),也就是第二粘片胶5在凸台42处的胶厚远小于凸台42以外区域的胶厚。30.参照图1至图4,根据力学原理,对于mems芯片6、第二粘片胶5以及应力缓冲垫板4构成的多层结构,从应力缓冲垫板4传递至mems芯片6的应力大小取决于中间层(即第二粘片胶5)的形貌,第二粘片胶5的面积越小、厚度越厚,则隔离应力的效果越好,因此理想的应力隔离结构是中心单点支撑结构或者最大程度加厚粘胶层,但也存在粘接强度不足的缺点,会导致封装结构在承受冲击时晃动过大,甚至失效;本实施例中,位于中心的凸台42处的粘胶面积远小于基片41的面积,且厚度薄,具有中心单点支撑结构的特征,即通过小面积降低作用于mems芯片的弯矩,通过薄厚度增强切向刚度;凸台42以外区域的粘胶通过大厚度降低作用于mems芯片的弯矩,以此减小mems芯片6与封装管壳1之间的应力耦合,最终使得该封装结构兼具较好的应力缓冲或者释放效果,以及较高的粘接强度。31.实施例2:一种mems器件的应力缓冲封装结构,参照图5,以实施例1为基础,本实施例与实施例1的区别在于:本实施例中基片41上设置有一个凸台42和三个凸点圈43,且凸台42与三个凸点圈43分别设置于基片41的四个顶角处,基片41、凸台42以及凸点431的高度递增,在应力缓冲垫板4正面构成另外一种三维化图形特征。32.实施例3:一种mems器件的应力缓冲封装结构,参照图1至图4以及图6,以实施例1为基础,本实施例与实施例1的区别在于:本实施例中用于粘接mems芯片6的第二粘片胶没有采用整面粘接,而且多点粘接,具体为五个粘胶点,包括凸台粘胶点51和凸点圈粘胶点52;五个粘胶点的位置和形貌由凸台42和凸点圈43的位置和形貌决定,即凸台粘胶点51的面积约为凸台42的面积,胶厚等于第一高度差,凸点圈粘胶点52的直径约为凸点圈43的直径,胶厚为第一高度差与第二高度差之和;与实施例1相比,能够提高应力缓冲或者释放效果。33.参照图6,本实施例中将asic芯片9通过第三粘片胶8固定在mems芯片6上,形成机械电子系统的堆叠集成封装。34.实施例4:一种mems器件的应力缓冲封装结构,参照图1至图4以及图7,以实施例1为基础,本实施例与实施例1的区别在于:本实施例中用于粘接mems芯片6的第二粘片胶没有采用整面粘接,而且多点粘接,具体为四个凸点圈粘胶点52;四个凸点圈粘胶点52的位置和形貌由凸点圈43的位置及形貌决定,即四个凸点圈粘胶点52的直径约为凸点圈直径,胶厚为第一高度差与第二高度差之和,和值越大、凸点圈直径越小则四个粘胶点的应力释放越好;同时,本实施例中第二粘片胶由低杨氏模量的软胶改为较高杨氏模量的硬胶(例如环氧胶等),硬胶杨氏模量一般为1~5gpa,能够增强粘接结构的刚性;本实施例中的封装结构具有较高粘片强度、较好应力释放效果、足够的谐振反作用力支撑等优点,适合mems振荡器、mems陀螺等高品质因子谐振器件的封装。35.实施例5:一种mems器件的应力缓冲封装结构,参照图1至图4以及图8,以实施例3为基础,本实施例与实施例3的区别在于:本实施例中第二粘片胶由低杨氏模量的软胶五点粘接改为较高杨氏模量的硬胶(例如环氧胶等)单点粘接,粘胶点为凸台粘胶点51;粘胶的位置和形貌由凸台42的位置和形貌决定,即凸台粘胶点51的面积约为凸台面积,胶厚为第一高度差;本实施例中mems芯片封装结构为中心单点支撑结构,凸点431与mems芯片6之间无固定连接,但可以起到一定的垂直支撑作用,减小凸台42面积可以改善应力隔离效果,增大凸台42面积可以增加粘片强度,取折中优化则可以兼顾应力隔离和粘片强度。36.参照图8,同时,本实施例中asic芯片9通过第三粘片胶8固定在封装管壳1的封装底板11上,形成机械电子系统的平铺式集成封装。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123373.html

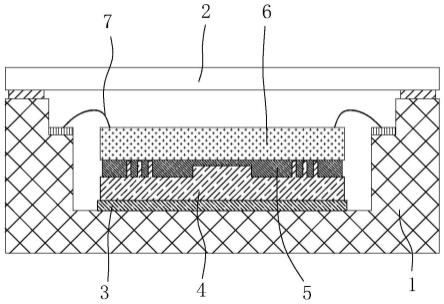

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。