一种三明治式微机电系统的圆晶级真空封装腔及封装方法

- 国知局

- 2024-07-27 12:47:54

1.本发明属于mems器件封装技术领域,更具体地,涉及一种三明治式微机电系统的圆晶级真空封装腔及封装方法。背景技术:2.mems器件不同于其他集成电路的典型特征是器件一般包含传感、三维结构、运动模块。空气水汽等对大型器件的影响微乎其微,但是对于微小型器件的影响变得更为明显。为了隔绝空气对微电子器件的影响,一般考虑对器件进行真空封装。3.目前对于微电子器件的发展,封装是工艺流程中至关重要的一环。但是现行的成熟工艺大多为密封封装,这是由于真空封装中,泄漏率的存在使得空气始终会向器件内部泄漏。由于微电子器件的体积限制,腔体内部的气压往往上升过快。4.为了解决这一问题,可以提升封装的质量,从而降低封装器件的泄漏率。在目前的封装技术条件下,一般能够将封装泄漏率控制在10e-10pa m3/s以下,但是更低的泄漏率在现有的封装工艺水平下难以达到。而在这种泄漏率水平下,对于一个真空封装的微电子器件,其气压上升至一千帕,所花时间不会超过100小时。这样一个寿命水平显然无法满足目前对真空封装的要求。5.对于泄漏率而言,真空封装好的器件,其内外压力差越大,泄漏率就越大;其内外压力差越小,泄漏率就越小。6.考虑到封装工艺技术的限制,期待采用其他方式完成泄漏率的控制。此处对于三明治式三层封装采用的是缓冲腔设计。7.公开号为cn 101723308 a的中国专利公开报道了一种mems圆片级真空封装方法,该发明提供了一种通过硅片深刻蚀作为倒模制作玻璃上盖,设计了缓冲腔,利用在真空下进行阳极键合,形成整个真空封装。公开号为cn 101554987a的中国专利公开报道了一种微机电系统的圆片级真空封装工艺,通过沉积牺牲层维持内部空间和缓冲腔,刻蚀释放孔完成后去除牺牲层后完成封盖的沉积形成封装。公开号为cn 101554988a的中国专利公开报道了一种微机电系统的圆片级真空封装方法,该方法通过沉积吸气剂以及缓冲腔设计,保证真空封装的长时间维持。公开号为cn 101049904a的中国专利公开报道了一种真空封装方法及其装置,该发明通过在一个封装空间的外围设计了一个或多个缓冲的过渡空间,以降低真空封装泄漏率,从而延长整个真空封装器件的寿命。8.然而,上述封装方式存在如下技术问题:所有的这些设计均为针对双层微机电系统的设计,兼容性不高,其中大多数专利针对对象是管壳封装,器件更大,其封装键合方式繁琐,成本过高。技术实现要素:9.针对现有技术的缺陷,本发明的目的在于提供一种三明治式微机电系统的圆晶级真空封装腔及封装方法,旨在解决现有技术中由于微电子器件内部腔体气压上升速度过快导致器件寿命缩短的问题。10.本发明提供了一种三明治式微机电系统的圆晶级真空封装腔,包括:上盖板、下盖板和位于所述上盖和所述下盖之间的中间层,所述中间层包括主腔体、第一层封装环、第二层封装环、缓冲腔和贯通孔;主腔体位于中心,用于为工作器件提供真空工作环境;第一层封装环环绕设置在主腔体外,且第一层封装环在上盖板和下盖板位置处一一对应,以保证上盖板和下盖板上刻蚀的凹槽;在第一层封装环外设置有缓冲腔,且缓冲腔上下对应以便于贯穿通孔链接;在缓冲腔外环绕设置有第二层封装环,且第二层封装环的位置对于上盖板和下盖板而言一一对应,以保证键合的对顶强度以及器件的规则性,从而方便圆片级键合之后的切片;贯通孔设置在所述缓冲腔的中间位置,用于保证避开其他应力集中的位置。11.更进一步地,在主腔体与上盖板和下盖板接触的位置沉积大量吸气剂,用于维持所述主腔体的气体压强。12.更进一步地,在缓冲腔底部沉积有吸气剂,用于延缓所述缓冲腔的压强上升的速度。13.更进一步地,通过磁控溅射的方式在所述缓冲腔(7)和所述主腔体(6)完成ti基吸气剂的沉积。14.更进一步地,通过控制所述缓冲腔(7)的大小来控制对器件的寿命延长效果,代价是整体器件的大小,其漏率规律满足腔体压强随时间变化如下:其中pex表示环境压强,pt表示主腔体的压强,l表示泄漏率,v表示腔体体积,ma表示参考气体的气体分子量,mb表示工作环境中泄漏气体的气体分子量。封装环内外的压强差影响腔体的压强上升速度;更大的缓冲腔能够降低缓冲腔内部压强上升的速度,使得主腔体和缓冲腔的压强差更小,从而降低主腔体压强上升速度,延长主腔体真空寿命。15.更进一步地,上盖板、下盖板以及中间层的材料可以采用高纯硅片、碳化硅或soi硅片。16.本发明还提供了一种基于上述的圆晶级真空封装腔的封装方法,包括下述步骤:17.在第一层封装环和第二层封装环之间进行干法或者湿法刻蚀,使得缓冲腔的体积增大;18.采用干法或者湿法在第一层封装环和第二层封装环之间蚀刻出所述贯通孔;19.在主腔体的底部或者侧壁沉积吸气剂。20.更进一步地,可以通过增大下盖板的封装环宽度以保证整体的键合效果。其中,受对准精度所限,误差对于两层封装环都有影响,因此封装环指的是每层封装环,每层封装环下盖板的宽度需要比上层封装环宽2μm,保证对封装时对准的补偿。21.更进一步地,下盖板的封装环处的硅片衬底需要保证一定的宽度,确保整个键合过程中的对顶强度,达到良好的键合效果。其中,键合时的封装环最好保证在5μm以上,保证键合的强度。因此,下盖板的封装环宽度保证大于7μm,上盖板的封装环宽度保证大于5μm。下盖板总保证比上盖板宽2μm,补偿键合时的对准误差。22.更进一步地,在缓冲腔的底部或者侧壁沉积吸气剂,从而延缓主腔体压强上升的速度,提升整个器件的寿命。23.更进一步地,所述键合方法包括但不限于晶圆直接键合,阳极键合,共晶键合,要求其键合之后的漏率达到美军标mld-std-883e标准,最好是能够达到10e-10水平。24.在本发明实施例中,对于封装时上盖板与下盖板的封装环位置保持一致;若上盖与中间层先键合,再与下盖键合,则保证上盖的封装环宽度,以确保与下盖键合时候的对顶强度。若下盖与中间层先键合,再与上盖键合,则保证下盖的封装环宽度,以确保与上盖键合时候的对顶强度。25.通过本发明所构思的以上技术方案与现有技术相比,具有以下有益效果:26.(1)本发明通过在正常真空封装的器件的封装环外,加入了新的封装环,以构筑缓冲腔,使得气体先进入缓冲腔,在缓冲腔内积累,引起压强上升之后,再向主腔体内渗透。将主腔体压强和外界环境压强的压强差,转变为主腔体-缓冲腔-外界环境的压强台阶,从而降低主腔体内部压强上升的速度。27.(2)本发明通过将对三明治式mems器件的设计,将下盖主腔体和缓冲腔位置蚀刻出腔室,增大了主腔体和缓冲腔的空间。相比较于双层器件封装,双层器件一般在器件的主腔体上方沉积吸气剂,下方一般为器件的功能模块,无法沉积。而在本发明中,主腔体下方以及缓冲腔的下方均可以沉积吸气剂,真空寿命得到极大提升。对于缓冲腔,通过贯穿通孔链接,增大了缓冲腔的整体体积,延缓了缓冲腔的气压上升速度。28.(3)本发明通过缓冲腔的设计,延长了主腔体的寿命,从而改进了现有的真空封装解决方案,即通过大量的吸气剂来维持主腔体的寿命。从而降低了对吸气剂的要求,降低了对吸气剂的研究成本。29.(4)本发明提供的整体三明治式mems器件的真空键合方法,通过贯通孔的设计,平衡了上下键合面的键合漏率,兼容性强且操作简单易行,无需苛刻的条件,能够实现较好的寿命指标,实用性强。附图说明30.图1为本发明实施例提供的三明治式微机电系统真空封装的缓冲腔的结构示意图;31.图2为本发明实施例提供的三明治式微机电系统真空封装的缓冲腔的上层整体封装示意图;32.图3为本发明实施例提供的三明治式微机电系统真空封装的缓冲腔的中层整体封装示意图;33.图4为本发明实施例提供的三明治式微机电系统真空封装的缓冲腔的下层整体封装示意图;34.图5为本发明实施例提供的三明治式微机电系统真空封装的缓冲腔的下盖和中间层键合,其整体再与上盖键合的封装过程示意图。35.其中,1为上层,2为中层,3为下层,4为第一层封装环,5为第二层封装环,6为主腔体,7为缓冲腔,8为中层贯通孔,9为吸气剂。具体实施方式36.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。37.本发明提供了一种用于在完成三明治式mems器件真空封装过程中为保证封装寿命而设计的缓冲腔及其封装方法,通过对封装环进行单独处理,可以解决微电子器件内部腔体气压上升速度过快的问题。38.对于需要真空封装的微电子器件而言,其寿命与其腔体的压强直接相关,过高的压强会影响器件性能甚至无法正常工作。因此,对于真空封装,其寿命指标是十分重要的。为了提升器件的寿命,即降低气体向主腔体内泄漏的速度,需要良好的键合水平,优秀的吸气剂充当气体泵浦,存储泄漏气体。在本发明中,提出了一种器件结构上的设计,通过创建一个缓冲腔,使得气体首先向缓冲腔内泄漏,被吸气剂吸附,之后才会向主腔体内泄漏,从而延长了器件的寿命。为了保证缓冲腔体的体积,平衡吸气剂的压力以及吸气剂的沉积量,采用贯通孔连接三层键合器件的上下层缓冲腔,形成一个整体的腔体。39.图1示出了本发明实施例提供的三明治式微机电系统的圆晶级真空封装腔,为了便于说明,仅示出了与本发明实施例相关的部分,详述如下:40.本发明实施例提供的圆晶级真空封装腔包括:最内部的主腔体,用以提供工作器件的真空工作环境。其盖板位置沉积大量吸气剂,用以主腔体的气体压强维持。环绕主腔体为第一层封装环,其封装环在上下盖板位置处一一对应,以保证上下盖板上刻蚀的凹槽,即缓冲腔上下对应,以便于贯穿通孔链接。其贯穿通孔位置应在缓冲腔的中间位置,以保证避开其他应力集中的位置。通过在缓冲腔底部沉积吸气剂,用以延缓缓冲腔的压强上升的速度。缓冲腔外环绕为第二层封装环,与第一层封装环相似,我们也需要保证第二层封装环的位置对于上下盖板而言一一对应,以保证键合的对顶强度,以及器件的规则性,从而方便圆片级键合之后的切片。41.如图2所示,对于器件的上层,形状一般为方形,其主腔体的上层与缓冲腔的上层沉积吸气剂,此处采用ti基吸气剂,ti表面沉积20nm的au以充当牺牲层,防止ti吸气剂氧化,并在键合加温时完成吸气剂的激活,用以保证缓冲腔的腔体压强上升不会太快。其中缓冲腔和主腔体之间的封装环,保持窄于中间层封装环的宽度,其差值与器件制作时的光刻精度相关,以保证键合时,上层的封装环能完整附着在中间层的封装环上。42.如图3所示,对于器件的中间层,一般包括器件的主要运动模块,或者是其他需要真空环境才能正常工作的模块,保证器件功能的正常实现。与器件的上层封装环匹配,需要保证中间层的封装环的宽度,宽于上层的缓冲腔和主腔体之间的封装环,一般可保持差值在2μm以上,其差值与器件制作时的光刻精度相关,以保证键合时,上层的封装环能完整附着在中间层的封装环上。另外,中间层的缓冲腔的位置,需要蚀刻出贯穿通孔,其位置一般在器件缓冲腔的长边的居中位置,以保证避免器件的应力集中。43.如图4所示,对于器件的下层,作为最初的封装模块,其封装环的宽度是最宽的,以满足键合顺序:下层-中层,键合好的器件再与上层键合。下层的封装环需要保证与中间层键合时的压力,二次键合的时候,需要保证与上层封装环键合时的压力。同样,与器件的上层一样,需要在主腔体和缓冲腔的下部沉积吸气剂。同样沉积ti-au吸气剂,用以保证缓冲腔的腔体压强上升不会太快。44.本发明提供的缓冲腔技术与现有技术相比,实现了圆晶级真空封装腔从双层圆片级封装到三明治式微机电系统的真空封装的突破。通过上下层同时沉积吸气剂,延缓了缓冲腔的真空度上升的速度。利用中间层的贯穿通孔,提升了缓冲腔的体积,平衡了由于上下键合面的漏率不同带来的缓冲腔上下层的吸气剂压力差异。另外对于吸气剂,本发明中的吸气剂能力更好,通过吸气剂的牺牲层,保证了吸气剂在工作前,不会出现工艺步骤中的损耗;且在键合时,能够同时完成吸气剂的激活,工艺步骤更简单。其封装工艺也更加简单,相比较于没有缓冲腔的设计,制作工艺并没有特别的变化,因此相对于现有技术,工艺兼容性有相当的优势。而封装步骤中的工艺兼容性,能保证更好的封装效果,保证更低的器件漏率。45.本发明还提供了一种基于上述缓冲腔的真空封装方法,包括如下步骤:46.对于器件的上盖,通过干法刻蚀或者湿法刻蚀,完成缓冲腔的蚀刻,通过掩膜光刻和电子束热蒸发,完成封装环的沉积。通过电子束热蒸发或者磁控溅射,在缓冲腔的底部或者下盖的中央位置,完成吸气剂的沉积。47.对于器件的中间层,通过干法或者湿法刻蚀,在多层缓冲腔的夹层硅片位置,完成贯穿刻蚀,贯通孔不需很大,仅仅起到连通上下盖板的作用。注意不要影响到器件的键合位置。48.对于器件的下盖,通过干法刻蚀或者湿法刻蚀,完成缓冲腔的蚀刻,通过掩膜光刻和电子束热蒸发,完成封装环的沉积。通过电子束热蒸发或磁控溅射,在缓冲腔的底部或者下盖的中央位置,完成吸气剂的沉积。49.对于上盖-中间层-下盖的键合顺序,决定了封装环的衬底宽度,为了保证器件的键合精度和键合强度,需要给出键合的余量。50.优选地,上盖板、中间层和下盖板可以采用高纯硅材料;硅作为半导体产业中被广泛应用的材料,在微尺寸下,硅的强度仍然能够保持,在器件尺寸很小的情况下,封装环的尺寸更小,而高纯硅能够保证器件的键合强度。51.优选地,本发明方法还包括利用在上下盖以及缓冲腔的内壁沉积吸气剂,延长缓冲腔的压强上升时间,外界气体始终在向器件内部泄漏或者是渗透,吸气剂具体作用在于,将泄漏进入器件内部的气体,包括水汽和空气,通过物理吸附或者化学吸附,将气体吸附在吸气剂表面,并通过扩散,将吸气剂表面的气体向吸气剂底部输运,维持吸气剂表面的吸附能力。通过这种方式,能较长时间的维持缓冲腔的压强水平。更低的缓冲腔压强水平,能够使得缓冲腔内的气体向主腔体泄漏的速度更慢,从而减缓主腔体压强上升的速度,从而维持器件的寿命。52.优选地,当下盖先于中间层键合,然后再与上盖键合,则下盖的封装环需要留出余量,其值与键合设备的对准精度相关。例如光刻和键合对准精度为2um,则上下封装环的设计时,可以将其下层拓宽2um,以保证键合过程中,中间层和下层能精准对齐,防止封装环悬空。53.当上盖先于中间层键合,然后再与下盖键合,则上盖的封装环需要留出余量,其值与键合设备的对准精度相关。54.进一步优选地,对缓冲腔和主腔体的吸气剂选择ti基吸气剂,吸气剂展现了对氧气和氢气和水汽有良好的吸附能力。ti表面沉积20nm的au以充当牺牲层,防止ti吸气剂氧化,并在键合加温时完成吸气剂的激活,通过电子束热蒸发或者磁控溅射沉积,例如磁控溅射沉积过程的工艺参数为:气体流量ar为20sccm,功率控制在250w,溅射时压强为1mtorr,温度控制在25℃。55.优选地,晶圆键合可以通过硅硅直接键合或者金金热压键合或者铜铜热压键合,完成键合。对于硅硅直接键合,键合结果能够达到体硅强度,但是需要硅与硅的表面粗糙度十分光滑。由于在下层和中间层的键合之前经历的工艺步骤很少,对键合表面的影响更低,能够保证封装键合的质量,因此选择硅硅直接键合的方式,得到更低的漏率和更高的键合强度。而金金热压键合或者铜铜热压键合,对键合表面的粗糙度更加包容,而且键合效果也佳,能够满足更低的漏率,因此应用于中间层和上层的键合中,且在键合过程中,通过加热环境能够完成吸气剂的激活,简化工艺流程。56.本发明提出的缓冲腔是针对零级封装的设计;采用缓冲腔将主腔体与外界的气压差减小,以台阶形式上升;并将上下两个腔体通过贯穿通孔打通,使得缓冲腔的体积得到提升,由于上下键合方式选择不同,两个键合面存在不相同的漏率。通过贯穿通孔,连接上下两个缓冲腔室,使其平衡上下缓冲腔中两个吸气剂面的压力,增强其减缓主腔体气压上升速度的效果,在三层键合的下层向下刻蚀凹坑,扩大主腔体的体积,并在底部沉积吸气剂,增大吸气剂的体积,延长器件寿命。57.为了更进一步的说明本发明实施例,现参照附图并结合具体实例详述如下:58.(1)如图2所示,对于真空封装的器件的下层,首先在硅片内表面涂覆光刻胶充当掩膜,经历光刻以及显影,利用等离子体的深刻蚀,将主腔体以及缓冲腔的腔体刻蚀出来。一般而言,封装环的宽度可以设定在10um-15um,使得能够得到良好的键合效果,良好的漏率和更小的器件尺寸。之后利用磁控溅射或者电子束热蒸发,以磁控溅射为例,其工艺参数为:气体流量ar为20sccm,功率控制在250w,溅射时压强为1mtorr,温度控制在25℃,完成ti基吸气剂的沉积,之后再完成au牺牲层的沉积,保护ti,整个过程均在磁控溅射镀膜机中进行,其内部真空度保证了ti吸气剂在被au层保护之前不被氧化。如果采用电子束热蒸发,则原理相同。59.(2)如图3所示,首先在硅片内表面涂覆光刻胶充当掩膜,经历光刻以及显影,利用等离子体的深刻蚀,将主腔体和工作模块以及链接上下缓冲腔的贯穿通孔刻蚀出来。贯穿通孔位置一般在中间层的两层封装环的中间,目的是为了避免应力集中。针对不同的器件而言,贯穿通孔位置不同,但是核心思想为避免应力集中,保证器件的键合质量和本身强度。60.(3)如图4所示,对于真空封装的器件的上层,首先在硅片内表面涂覆光刻胶充当掩膜,经历光刻以及显影,利用等离子体的深刻蚀,将主腔体以及缓冲腔的腔体刻蚀出来;一般而言,封装环的宽度可以设定在10um-15um,使得能够得到良好的键合效果,良好的漏率和更小的器件尺寸。然后利用相同工艺,依靠掩膜以及光刻显影,完成键合层的au层沉积。之后利用磁控溅射或者电子束热蒸发镀ti吸气剂,以磁控溅射为例,其工艺参数为:气体流量ar为20sccm,功率控制在250w,溅射时压强为1mtorr,温度控制在25℃,完成ti基吸气剂的沉积,之后再完成au牺牲层的沉积,保护ti,整个过程均在磁控溅射镀膜机中进行,其内部真空度保证了ti吸气剂在被au层保护之前不被氧化。如果采用电子束热蒸发,则原理相同。61.(4)如图5所示,将制作好的器件下层与中间层,利用硅硅直接键合方式,在键合机下进行对准,键合温度350℃,键合压力6000mbar,键合时间为一个小时,键合成为一个整体,之后在中间层的封装环位置,沉积au,做好与器件上层进行金金直接键合的准备。同样,将其与器件上层在键合机中进行对准,键合温度450℃,键合压力7000mbar,键合时间一个小时。在键合过程中,由键合机内部分子泵抽真空,完成封装之后,键合机真空度即为器件初始真空度。而键合的加热过程,能够同时完成ti基吸气剂表面的au牺牲层的消耗扩散,从而露出被保护的ti吸气剂,简化了工艺流程,保证了吸气剂的性能。62.(5)由于键合顺序为下层和中层先键合,键合成型之后,再与上层键合。工艺中保证下层缓冲腔的封装环宽度大于上层缓冲腔封装环宽度,因此,在器件设计时,需要考虑给器件的下层余量,其大小与光刻和键合的对准精度相关。例如,若光刻和对准过程中,误差为2um,则设计时下层封装环的宽度应比上层大2um,以保证在产生误差时,中间层与下层的封装环,总是能够完整受力,不会因为误差产生悬空部分,从而确保良好的键合效果。同理,中间层与上层键合时,也应考虑这一点。63.本发明为三明治式真空封装的键合技术,与现有技术相比,对于吸气剂方面,利用牺牲层,提升了吸气剂的性能;对于器件设计方面,利用缓冲腔的设计,降低了吸气剂的压力,增大了对键合效果的容忍度,在下盖刻蚀出凹坑,增大了主腔体的体积,并在下盖位置沉积吸气剂,大幅增大了吸气剂的体积。同时通过中间层的贯穿通孔的设计,能够将器件的上下缓冲腔链接,平衡缓冲腔上下的吸气剂的压力。在追求更低的漏率显得很困难的时候,该技术能够明显提升器件的寿命。同时,这种技术的优势体现在,由于该技术仅仅通过增加了缓冲腔以及扩大了主腔体的体积,以及主腔体和缓冲腔中吸气剂的沉积,完成延缓主腔体气体的泄露因此,并没有与现行的mems工艺冲突,兼容性良好。对微机电系统表现为良好的普适性,很多器件的封装,都能通过这种方式获得寿命提升,应用意义大。64.本领域的技术人员容易理解,以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123638.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

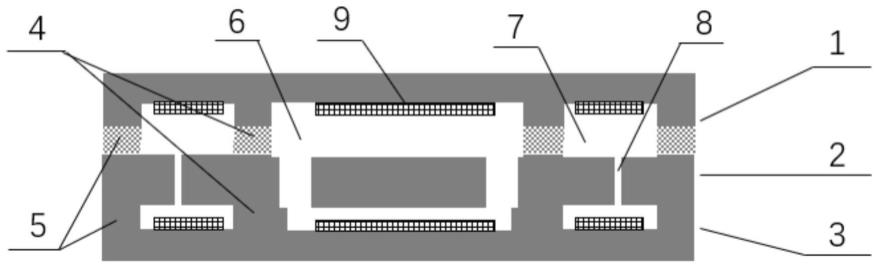

返回列表