一种器件芯片、微机电系统及其封装结构的制作方法

- 国知局

- 2024-07-27 12:51:48

1.本发明涉及微观机械系统技术领域,尤其是一种器件芯片、微机电系统及其封装结构。背景技术:2.微机电系统(mems, micro-electro-mechanical system),也叫做微电子机械系统、微系统、微机械等,指尺寸在几毫米乃至更小的高科技装置。3.微机电系统是使用半导体技术制造的并以形成机械和电子部件的器件。常见的微机电系统有谐振器、加速器、压力传感器、致动器、反射镜、加热器以及打印机喷头等。4.相关的微机电系统由器件芯片(mems芯片)和控制芯片(cmos芯片,cmos是complementary metal oxide semiconductor,互补金属氧化物半导体的缩写。它是指制造大规模集成电路芯片用的一种技术或用这种技术制造出来的芯片)组成,其中,器件芯片主要包括基衬底、盖衬底以及器件层,盖衬底与基衬底对应间隔设置,器件层设于基衬底和盖衬底之间;器件层包括电极、相互连接的连接部和致动部,其中,连接部分别与基衬底和盖衬底固定连接,电极与基衬底固定连接并和盖衬底电性耦合连接;电极靠近致动部设置,以驱动致动部动作。5.上述器件芯片的器件层,特别是电极部分,受到基衬底和盖衬底的挤压,容易导致电学性能变差,从而影响致动部的动作。技术实现要素:6.本发明的目的在于提供一种器件芯片、微机电系统及其封装结构,旨在解决现有技术中器件层受挤压后电学性能变差而影响致动部动作的问题。7.本发明是这样实现的,第一方面提供了一种器件芯片,其包括:基衬底、盖衬底以及器件层,其中,所述盖衬底与所述基衬底间隔设置,所述器件层设置在所述基衬底和所述盖衬底之间;所述器件层包括电极、连接部以及致动部,所述连接部分别与所述基衬底和所述盖衬底固定连接,所述电极与所述基衬底固定连接并与所述盖衬底电连接,所述致动部与所述连接部耦合;所述致动部与所述电极之间设置有间隙,以使在所述致动部和所述电极之间形成电容;所述电极用于接收电信号,并根据所述电信号驱动所述致动部;所述电极上设置有凹槽,所述凹槽沿所述电极的厚度方向延伸,且所述凹槽的开口朝向所述盖衬底。8.其中一些实施例中,所述电极的中间部分与所述盖衬底电连接。9.其中一些实施例中,所述凹槽位于所述电极之中间部分的一侧,或者,所述凹槽相对于所述电极之中间部分对称设置。10.其中一些实施例中,所述凹槽呈环形,所述凹槽环绕所述电极的中间部分设置。11.其中一些实施例中,所述间隙的宽度大于所述凹槽的宽度。12.其中一些实施例中,所述凹槽的宽度在0.7~2.0um之间,所述间隙的宽度在1~3um之间。13.其中一些实施例中,所述基衬底和所述盖衬底为硅基衬底,所述器件层的材质为单晶硅。14.其中一些实施例中,所述盖衬底上设置有硅通孔,所述硅通孔沿所述盖衬底的厚度方向设置,且所述硅通孔设置在所述电极的上方,所述盖衬底通过所述硅通孔与所述电极电连接。15.另一方面,本发明提供了一种微机电系统,其包括:控制芯片、引线以及上述任一项所述的器件芯片,其中,所述基衬底与所述控制芯片固定连接;所述引线分别与所述盖衬底和所述控制芯片固定连接并电性耦合。16.再一方面,本发明提供了一种封装结构,其包括:基板、封装胶以及上述微机电系统;所述控制芯片固定在所述基板上;所述封装胶将所述器件芯片和所述控制芯片包覆在所述基板上。17.本发明所提供的器件芯片、微机电系统及其封装结构,在电极上沿厚度方向设置有凹槽,解决了现有技术中器件层受挤压后电学性能变差而影响致动部动作的问题。附图说明18.图1是本发明实施例提供的器件芯片的结构示意图;图2是本发明实施例提供的drie刻蚀法的深度与宽度比图;图3a和图3b是本发明实施例提供的一种器件层中凹槽和间隙的drie刻蚀法的示意图;图4a至图4d是本发明实施例提供的另一种器件层中凹槽和间隙的drie刻蚀法的示意图;图5是本发明实施例提供的微机电系统和封装结构的结构示意图;图6是是本发明实施例提供的封装结构的数据;图7是本发明实施例提供的器件芯片与未设置凹槽的器件芯片的对比实验数据。19.附图标记:1-器件芯片、11-基衬底、12-盖衬底、13-器件层、131-电极、132-连接部、133-致动部、134-锚点、135-凹槽、136-间隙、121-硅通孔、2-控制芯片、3-引线、4-基板、5-封装胶、a-凹槽光刻胶、b-间隙光刻胶。具体实施方式20.为了使本发明的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本发明进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本发明,并不用于限定本发明。21.本实施例的附图中相同或相似的标号对应相同或相似的部件;在本发明的描述中,需要理解的是,若有术语“上”、“下”、“左”、“右”等指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此附图中描述位置关系的用语仅用于示例性说明,不能理解为对本专利的限制,对于本领域的普通技术人员而言,可以根据具体情况理解上述术语的具体含义。22.以下结合具体实施例对本发明的实现进行详细的描述。23.参阅图1所示一种器件芯片1,包括:基衬底11(handle wafer)、盖衬底12(cap wafer)以及器件层13(device layer)。24.其中,基衬底11位于下方,盖衬底12位于上方并与基衬底11间隔对置,器件层13设置在基衬底11和盖衬底12之间。25.器件层13包括电极131、连接部132以及致动部133,其中,连接部132分别与基衬底11和盖衬底12固定连接。可以理解的是,连接部132令基衬底11、器件层13以及盖衬底12三者固定,从而使得基衬底11、器件层13以及盖衬底12共同组成了器件芯片1。26.电极131与基衬底11固定连接,且电极131与盖衬底12电连接。致动部133与电极131之间设置有间隙136,以使在致动部133和电极131之间形成电容,其中,致动部133和电极131之间形成的电容为敏感电容。电极131用于接收电信号以驱使致动部133动作。27.电极131上设置有凹槽135,凹槽135沿电极131的厚度方向延伸,且凹槽135的开口朝向盖衬底12。28.需要说明的是,器件层13设置在基衬底11和盖衬底12之间,电极131与基衬底11固定连接,电极131与盖衬底12电连接,可以理解的是,为了实现电极131与盖衬底12的电连接需要使用导电的材质将电极131与盖衬底12连接,即电极131的上下两端分别由基衬底11和盖衬底12固定,因此,电极131会受到来自基衬底11和盖衬底12的挤压。29.可以理解的是,由于电极131受到基衬底11和盖衬底12的挤压,电极131容易受到外界应力的影响,导致电学性能变差,从而影响了致动部133的动作。30.在电极131上沿厚度方向设置有凹槽135,解决了器件层13受挤压后电学性能变差而影响致动部133动作的问题。31.更具体地,凹槽135沿电极131的厚度方向进行设置,且凹槽135的开口朝向盖衬底12,可以理解的是,凹槽135本身并未贯通器件层13,因此凹槽135的存在不会令电极131整体的电学连接失去效力,即不会令器件层13失去本身的正常运行功能。32.可以理解的是,电极131的中间部分与盖衬底12电连接。凹槽135设置在电极131上,并且凹槽135的目的是吸收来自基衬底11和盖衬底12的挤压力。33.具体地,凹槽135被配置为一个,其位于电极131之中间部分的一侧。34.或者,凹槽135被配置为多个,多个凹槽135相对于电极131的中间部分呈对称设置。可以理解的是,这些凹槽135互不连接,由于电极131的中间部分处于这些凹槽135的中心位置,因此,电极131整体呈平衡状态。35.需要说明的是,在加工凹槽135的过程中,对于其外形无需过于精准控制。36.参阅图1所示,凹槽135呈环形,其环绕电极131的中间部分设置。可以理解的是,环形的凹槽135的中心为电极131的中间部分,因此电极131整体呈平衡状态。37.电极131靠近致动部133设置,电极131与致动部133之间留有间隙136以构成敏感电容,从而利用电容量的变化以驱动致动部133动作。电极131与致动部133之间的间隙136大于凹槽135的宽度。38.基衬底11和盖衬底12为硅基衬底。器件层13由单晶硅制成,器件层13中的致动部133可以是谐振体、梁、臂、静电马达等微机械结构,连接部132位于器件层13的边缘,器件层13可在晶圆上加工成型。39.器件层13中的凹槽135和间隙136,凹槽135的宽度在0.7~2.0um之间,间隙136的宽度在1~3um之间。40.如图1所示,基衬底11、器件层13、盖衬底12自下至上层叠设置,器件层13中的连接部132分别与基衬底11和盖衬底12固定了连接。在本实施例中,连接部132位于器件层13的边缘,连接部132藉由锚点134分别与基衬底11和盖衬底12固定。电极131藉由锚点134与基衬底11固定连接,电极131和盖衬底12电性耦合连接,电极131驱动致动部133动作。41.其中,一种锚点134的结构形式为玻璃硅键合,即硅-玻璃键合结构,sog(silicon on glass),指通过机械或化学方法将硅(单晶、多晶、多孔)与玻璃进行粘合后形成的层合材料。42.连接部132与基衬底11和盖衬底12玻璃硅键合,电极131与基衬底11玻璃硅键合。43.或者,器件层13分别与基衬底11和盖衬底12之间设置一层埋氧化层(soi wafer,soi全称为silicon-on-insulator,即绝缘衬底上的硅,该技术是在顶层硅和背衬底之间引入了一层埋氧化层),保留连接部132与基衬底11和盖衬底12之间的氧化物,以使得连接部132与基衬底11和盖衬底固定。44.上述两种锚点结构的固定方式具有较强的机械强度和可靠性。45.参阅图1所示,盖衬底12上贯穿开设有硅通孔121。硅通孔技术(tsv,through-silicon-via)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的最新技术。与以往的ic封装键合和使用凸点的叠加技术不同,tsv能够使芯片在三维方向堆叠的密度最大,外形尺寸最小,并且大大改善芯片速度和低功耗的性能。46.硅通孔121与电极131电性耦合连接,如图1所示,硅通孔121与电极131的中部电性耦合。盖衬底12上贯穿开设有硅通孔121,可使得电极131通过硅通孔121与外部电路形成讯号导通结构。47.在一实施例中,硅通孔121与电极131共晶键合(eutectic bonding),利用共晶键合与硅通孔121技术,在盖衬底12形成电性导通。48.凹槽135和间隙136的加工方法为drie刻蚀法。49.具体地,drie的全称是deep reactive ion etching,即深反应离子刻蚀,是一种主要用于微机电系统的干法腐蚀工艺,需要说明的是,drie刻蚀法刻蚀出的蚀刻深宽比具有一定的极限,即刻蚀的凹槽135的宽度越窄,刻蚀深度就越浅。参阅图2所示,当宽度0.7um,刻蚀深度可达46um;当宽度2.0um,刻蚀深度可达70um。50.更具体地,设置在电极131上的凹槽135不能贯通电极131,而间隙136则需要贯通器件层13将电极131和致动部133分隔开来,即间隙136的深度要大于凹槽135的深度,因此,间隙136的宽度要大于凹槽135的宽度。51.更具体地,凹槽135的最大宽度范围为0.7~2.0um,间隙136的最大宽度范围为1~3um。52.可以理解的是,器件层13的厚度可以在一定范围内变化,间隙136需要贯通器件层13,因此器件层13越厚,间隙136的宽度就越大。53.以下提供使用drie刻蚀法在器件层13上加工凹槽135和间隙136的方案:一种方案,采用drie刻蚀法将凹槽135和间隙136一次成型,利用drie刻蚀法的刻蚀深宽比极限,凹槽135设计为较小的宽度,间隙136设计为较大的宽度,例如,器件层13的厚度为20um,刻蚀深宽比为20:1,凹槽135的宽度为0.8um,间隙136的宽度》1um,如此,可以确保凹槽135只刻蚀到16um深度,无法刻穿;而间隙136可以完全刻穿,实现结构设计意图。54.参阅图3a和图3b所示:第一步,根据器件层13的厚度设计凹槽135和间隙136的宽度。55.具体地,凹槽135不能够贯通器件层13,间隙136则需要贯通器件层13,由于drie刻蚀法中蚀刻深宽比具有一定的极限,因此间隙136的宽度大于凹槽135的宽度。56.例如:当器件层13的厚度为20um时,刻蚀深宽比20:1,凹槽135的宽度为0.8um,间隙136的宽度》1um,如此,可以确保凹槽135只刻蚀到16um深度,无法刻穿;而间隙136可以完全刻穿,实现结构设计意图。57.第二步,如图3a所示,在器件层13的晶圆上涂覆凹槽光刻胶a。58.具体地,光刻胶又称光致抗蚀剂,是指通过紫外光、电子束、离子束、x射线等的照射或辐射,其溶解度发生变化的耐蚀剂刻薄膜材料。59.第三步,如图3b所示,进行drie刻蚀。60.凹槽135的宽度为0.8um,间隙136的宽度3um,如此,可以确保凹槽135只刻蚀到16um深度,无法刻穿;而间隙136可以完全刻穿,实现结构设计意图。61.再有,使用drie刻蚀法中刻蚀较小宽度的槽时刻蚀速度较慢,刻蚀较大宽度的槽时,刻蚀速度快,因此可以通过控制刻蚀时间,来确保凹槽135和间隙136的深度,以实现结构设计意图。62.参阅图3a和图3b所示,先进行光刻胶的设置,在器件层13的晶圆上涂覆凹槽光刻胶a,然后,进行drie刻蚀。其中,凹槽135的宽度为0.8um,间隙136的宽度3um,通过控制刻蚀时间,可以确保凹槽135只刻蚀16um深度,无法刻穿,而间隙136可以完全刻穿,实现结构设计意图。63.另一种方案,采用drie刻蚀法,将凹槽135和间隙136分别加工成型。先刻蚀凹槽135,再刻蚀间隙136。先进行凹槽光刻胶a的设置,在器件层13的晶圆上涂覆凹槽光刻胶a,然后,进行drie刻蚀,其中,凹槽135的宽度为0.8um,刻蚀16um深度;然后,冲洗掉凹槽光刻胶a,刻蚀间隙136,在刻蚀出凹槽135的晶圆上再次涂覆间隙光刻胶b,然后,进行drie刻蚀,其中,间隙136的宽度3um,将晶圆刻穿,以实现结构设计意图。具体地:第一步,如图4a所示,在器件层13的晶圆上涂覆凹槽光刻胶a。64.第二步,如图4b所示,进行凹槽135的刻蚀,其中,凹槽135的宽度为0.8um,刻蚀16um深度。65.第三步,冲洗掉凹槽光刻胶a。66.第四步,如图4c所示,在刻蚀出凹槽135的晶圆上再次涂覆间隙光刻胶b。67.第五步,如图4d所示,进行间隙136的刻蚀,其中,间隙136的宽度3um,将晶圆刻穿。68.上述方案是先刻蚀凹槽135,再刻蚀间隙136;可以理解的是,间隙136的刻蚀和凹槽135的刻蚀可以步骤调换,即先刻蚀间隙136再刻蚀凹槽135。69.在一些实施例中,基衬底11和盖衬底12为硅基衬底11,器件层13的材质为单晶硅。70.具体地,衬底是具有特定晶面和适当电学,光学和机械特性的用于生长外延层的洁净单晶薄片,硅基衬底11即使用硅材质制成的衬底,具有低成本、大尺寸、高质量、导电等优点。71.具体地,单晶硅即硅原子以一种排列形式形成的物质,更具体地,器件层13是由晶圆制成的,晶圆是由单晶硅为原材料制成的薄片,本发明提供的实施例通过drie蚀刻法在晶圆上进行蚀刻,以生成间隙136和凹槽135。72.在一些实施例中,盖衬底12上设置有硅通孔121。73.具体地,硅通孔技术(tsv,throughꢀ‑silicon-via)是通过在芯片和芯片之间、晶圆和晶圆之间制作垂直导通,实现芯片之间互连的最新技术,与以往的ic封装键合和使用凸点的叠加技术不同,tsv能够使芯片在三维方向堆叠的密度最大,外形尺寸最小,并且大大改善芯片速度和低功耗的性能。74.更具体地,硅通孔121沿盖衬底12的厚度方向设置,且硅通孔121设置在电极131的上方,硅通孔121与电极131电性耦合连接,硅通孔121与电极131的中间部分电性耦合,盖衬底12上贯穿开设有硅通孔121,即盖衬底12通过硅通孔121与电极131电连接,可使得电极131通过硅通孔121与外部电路形成讯号导通结构。75.在一些实施例中,致动部133为谐振梁、谐振臂以及静电马达中的任意一种。76.具体地,谐振梁和谐振臂均属于谐振器的一种,谐振梁和谐振臂在接收到电极131的电容变化后,会将这种变化放大,并跟随这种变化产生自身的振动。77.更具体地,静电马达基于电荷的吸引和排斥,当间隙136处的电容发生变化时,静电马达会产生振动。78.可以理解的是,致动部133与电极131间隔间隙136设置,用于根据电极131的电容变化而进行振动,谐振梁、谐振臂以及静电马达均能实现该目标。79.在一些实施例中,连接部132设置在基衬底11和盖衬底12的边缘位置。80.具体地,连接部132的数目为一个以上,基衬底11和盖衬底12形状大小接近,即基衬底11的边缘位置和盖衬底12的边缘位置是一一对应的,而连接部132即沿着两者的边缘位置均匀设置,从而实现基衬底11、器件层13以及盖衬底12的整体连接。81.更具体地,连接部132通过锚点134与基衬底11和盖衬底12固定连接,电极131通过锚点134与基衬底11固定连接。82.需要说明的是,锚点134是一种连接结构,在本发明提供的实施例中,锚点134的结构形式包括硅-玻璃键合结构和埋氧化层。83.更具体地,硅-玻璃键合结构是指通过机械或化学方法将硅与玻璃进行粘合后形成的层合材料。84.更具体地,埋氧化层即绝缘衬底上的硅,保留连接部132与基衬底11和盖衬底12之间的氧化物,以使得连接部132与基衬底11和盖衬底12固定。85.需要说明的是,上述两种锚点134结构的固定方式具有较强的机械强度和可靠性。86.参阅图5所示,一实施例,其提供了一种微机电系统,该微机电系统包括控制芯片2、引线3(wire)以及上述实施例中的器件芯片1。87.其中,器件芯片1固定在控制芯片2上,该器件芯片1中的基衬底11背离盖衬底12的一侧与控制芯片2固定连接。在一实施例中,基衬底11背离盖衬底12的一侧与控制芯片2粘接。引线3分别与器件芯片1中的盖衬底12和控制芯片2固定并电性耦合(wire bond)。更具体地,引线3的一端与盖衬底12的硅通孔121焊接并电连通,另一端与控制芯片2焊接并电连通。88.再参阅图5所示,又一实施例,其提供了一种封装结构,该封装结构包括基板4(pcb / substrate)、封装胶5以及上述实施例中的微机电系统。89.其中,微机电系统中控制芯片2背向基衬底11的一侧与基板4倒装焊接(flip chip),封装胶5将微机电系统中的器件芯片1和控制芯片2耦合,并且封装胶5将微机电系统中的器件芯片1和控制芯片2包覆在基板4上。其中,封装胶5优选环氧树脂封装胶。90.图6是上述封装结构所用材料之表格。其中,基板4使用fr材料,其厚度为100um,粘胶使用芯片胶水,其厚度为20um,控制芯片2的材质为硅,其厚度为75um,基衬底11的材质为硅,其厚度为200um,氧化硅凸台的材质为氧化硅,其厚度为2um,器件层13的材质为硅,其厚度为20um,硅凸台的材质为硅,其厚度为2um,盖衬底12的材质为硅,其厚度为30um,封装胶5的材质为环氧树脂,其厚度为900um,凹槽135厚度为15um,间隙136的厚度为3um。91.本实施例中的封装结构采用图6中的材料和尺寸,电极131处有/无凹槽135时,间隙136处的原始电容为4.7222,对该装结构施加20摄氏度温度载荷后,如图7所示,升温20摄氏度后,电极131处无凹槽135的情况下,间隙136处的电容变为4.7073,变化量为-0.317%;升温20摄氏度后,电极131处设置凹槽135的情况下,间隙136处的电容变为4.7147,变化量为-0.1586%。由此不难看出,当电极131处设置凹槽135时,间隙136处的电容变化较小,对电学性能影响较小,确保了致动部133的动作稳定性。92.以上所述仅为本发明的较佳实施例而已,并不用以限制本发明,凡在本发明的精神和原则之内所作的任何修改、等同替换和改进等,均应包含在本发明的保护范围之内。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123819.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

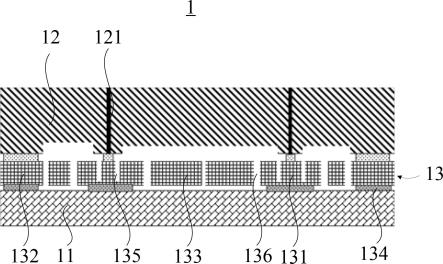

返回列表