用于制造电声模块的改进方法与流程

- 国知局

- 2024-07-27 12:51:52

1.本公开涉及用于制造电声模块的改进方法。背景技术:2.众所周知,现今存在着许多超声波传感器可供使用,它们被设计成发射和接收频率高于20khz的声波。除了电声类型的换能器之外,超声波传感器通常还包括电路,该电路被设计成驱动换能器,以及放大由换能器自身在接收到声学回波信号后所生成的电信号。换能器可以包括例如压电类型的致动器,其在不同的时间段中既用作声学发射器又用作声学接收器。3.如果我们分别将由换能器发射的声学信号(或波束)和(例如在声学刺激信号被障碍物反射后)撞击在换能器上的声学信号(或波束)标示为“声学刺激信号”和“声学响应信号”,则众所周知,例如在声像图(sonographic)领域,需要能够聚焦声学刺激信号。为了控制声学刺激信号在空间中的发出,公知技术设想提供多个换能器,换能器中的每一个换能器发出球面声波,并且用相对于彼此适当相移的驱动信号来控制这些换能器,以使得由换能器所生成的声学刺激信号的总和将形成具有所期望的空间分布的声学波束。4.如此而言,为了提高性能,尤其是关于回声的放大,有必要将通常由布置成阵列的对应mems(微机电系统)器件所形成的换能器布置得尽可能靠近电子电路,并且尤其是靠近负责放大由换能器所生成的电信号的电子电路部分。出于这个原因,形成精确地包括换能器和电子电路的所谓的电声模块是已知的。5.如此而言,由于每个换能器都耦接到相应的专用集成电路(asic),该asic形成与换能器相关联的接收器和驱动电路,因此有必要管理存在于换能器和与其相连的asic之间的数千个连接,从而控制由不同通道所引入的延迟(每个通道被理解为由换能器、对应的驱动电路和对应的接收器形成)以及存在于不同通道之间的抖动。6.如此而言,目前已知的是设想加工第一半导体晶片和第二半导体晶片的制造工艺,以便在第一晶片中形成多个换能器,以及在第二晶片中形成多个asic。接下来,将第一晶片和第二晶片耦接在一起,以使得换能器耦接到对应的asic。然而,该工艺的特征在于灵活性降低,因为它设想采用一种既用于驱动电路又用于接收电路的单个的制造技术。此外,这种制造工艺使得不可能测试asic——如果不是在完成工艺本身之后。7.为了克服上述限制,us 2020/0024131描述了一种制造方法,该方法设想形成预先已被单片化(即,被分离)并包括对应电子电路的管芯组件,以便形成一种重构晶片,该重构晶片此外包括一个再分布区域;然后,该方法设想将重构晶片耦接到包括单个半导体本体和多个压电致动器的晶片(被称为mems晶片),然后,首先通过研磨,接下来通过干式选择性蚀刻去除半导体本体的一部分,以使得剩余的半导体材料将形成多个近似于不可变形的衬底,每个衬底界定相应的多个凹部,在凹部上给出承载换能器的对应膜。此外,mems晶片包括多个导电柱,该导电柱电耦接到换能器;从而得到mems晶片和重构晶片之间的耦接,以使得导电柱被设置成与再分布区域的导电焊盘电接触,导电焊盘进而又电连接到形成在重构晶片的管芯中的集成电路。根据一个变形,多个半导体本体代替mems晶片而被提供在粘合材料带上,半导体本体中的每一个半导体本体包括相应的换能器和导电柱。然后将重构晶片耦接到由半导体本体和由粘合材料带所形成的整体(ensemble)。然后去除粘合材料带,并且存在于半导体本体之间的间隙填充有由环氧树脂形成的间隙区域。接下来,去除半导体本体的部分半导体材料,以便形成不可变形的衬底;该操作设想再次执行研磨,然后进行干式选择性蚀刻。8.不幸的是,us 2020/0024131中提出的解决方案的实际实施成为问题。事实上,设想将重构晶片与mems晶片耦接的解决方案会遭受所谓的翘曲现象,这会在局部导致一些导电柱与再分布区域的对应导电焊盘之间没有形成正确的电接触。9.设想将由半导体本体和由粘合材料带所形成的整体耦接到包括管芯的重构晶片的解决方案要求间隙区域由以令人满意的方式经受住在后续蚀刻步骤期间出现的高温的材料形成。不幸的是,目前还没有可用的完全满足上述需要的材料。10.此外,us 2020/0024131中描述的两种解决方案都设想在包括重构晶片的堆叠件(替代地,mems晶片或由多个半导体本体和由间隙区域形成的整体)上执行干法蚀刻;在这两种情况下,堆叠件都必须被布置在所谓的卡盘上,并且必须被适当地冷却,以便保证蚀刻均匀;然而,堆叠件中的温度均匀性的控制成为问题。技术实现要素:11.本公开提供了用于制造mems器件的工艺的至少一个实施例,其将至少部分地克服如上面所讨论的缺点。12.在至少一个实施例中,一种用于制造电声模块的方法,包括:形成组件,包括介电涂层区域;相对于彼此横向交错的多个单元部分,多个单元部分中的每一个第一单元部分包括被布置在介电涂层区域中的至少一个相应的管芯;以及电耦接到管芯的再分布结构,介电涂层区域和再分布结构被布置在彼此上;所述方法还可以包括形成晶片,该晶片包括厚度等于初始厚度的半导体本体,以及相对于彼此横向交错的多个相应单元部分,多个相应单元部分中的每一个相应单元部分包括被布置成与半导体本体接触的相应的支撑区域以及与支撑区域接触的多个相应的致动器;将晶片的半导体本体的厚度减小到最终厚度;然后选择性地去除部分半导体本体,以便从晶片开始单片化多个换能结构,多个换能结构中的每一个环能结构包括相应的半导体衬底,该半导体衬底接触对应的支撑区域(39)并被由支撑区域的对应部分界定的多个相应腔体穿过,该对应部分形成与对应的一个致动器机械耦接的对应膜;然后将换能结构耦接到组件的再分布结构。附图说明13.为了更好地理解本公开,现在参考附图仅通过非限制性示例的方式描述其优选实施例,其中:14.图1是电声模块的示意性横截面图;15.图2是重构晶片的示意性俯视图,其中一部分被去除;16.图3是沿着图2中所示的截面线iii-iii截取的图2中所示的重构晶片的一部分的示意性横截面图;17.图4-图8是在本制造工艺的连续步骤期间的半导体晶片的示意性横截面图;18.图9-图11是在本制造工艺的连续步骤期间的包括重构晶片和换能结构的组件的示意性横截面图;19.图12-图15是在本制造工艺的变形的连续步骤期间的半导体晶片的示意性横截面图;20.图16-图18是在本制造工艺的另一个变形的连续步骤期间的半导体晶片的示意性横截面图;以及21.图19是在本制造工艺的另一个变形的步骤期间的包括重构晶片和换能结构的组件的示意性横截面图。具体实施方式22.本工艺源于本技术人的观察。具体地,本技术人已经注意到,考虑到电声模块,对应的半导体衬底的机械模式振动如何具有与半导体衬底的厚度成反比的截止频率,其中膜伸出到该半导体衬底上的凹部延伸。因此,为了防止由膜的激发所引入的衬底的振动干扰电声模块的操作,截止频率显著高于(例如,一个数目级)膜敏感的最大频率(例如,后者为10mhz)是有利的。此外,厚度减小使得能够用例如硅树脂材料完全填充凹部,以改进声波的传输。23.因此半导体衬底和膜的总厚度不大于例如50微米(μm)是有利的。24.话虽如此,以下描述的是用于制造电声模块1的工艺,如图1中所示。25.首先应该说的是,电声模块1仅作为示例而包括第一管芯2和第二管芯4,在其内部分别形成有例如由已知类型asic构成的第一集成电路6和第二集成电路8。第一集成电路6和第二集成电路8中的每一个集成电路包括相应的发射电路和相应的接收电路,在第一集成电路6的情况下,它们分别被标示为10和12,并且在第二集成电路8的情况下,被标示为14和16。26.尽管未详细示出,但是在第一集成电路6和第二集成电路8中的每一个集成电路中,对应的发射电路和接收电路电连接到对应的多个金属凸块,分别被标示为18和20,并且还已知为微凸块。再次以本身已知的方式,凸块18、20电连接到对应的管芯的所谓的末级金属化。27.电声模块1还包括涂层区域22,该涂层区域22例如是环氧树脂并且包覆第一和第二管芯2、4以及对应的凸块18、20的一部分。涂层区域22由第一表面s1和第二表面s2来界定。第一和第二管芯2、4的凸块18、20伸出到第一表面s1上。此外,延伸穿过涂层区域22的是被称为“穿塑孔”(tmv:through mold via)类型的多个垂直连接区域24,每个垂直连接区域24由金属材料制成并且伸出到第一表面s1和第二表面s2上。28.电声模块1还包括再分布结构26,其包括介电区域28、多个导电路径30(被定性地示出)以及多个内部焊盘32和外部焊盘34。29.介电区域28例如是聚酰亚胺(或者例如聚酰胺或玻璃纤维树脂),并且与第一表面s1接触地延伸。除了由第一表面s1界定之外,介电区域28还由第三表面s3界定。30.内部焊盘32是金属材料(例如铜以及诸如镍的阻隔材料),并伸出到第一表面s1上,以便接触第一管芯2或第二管芯4的对应凸块18、20。外部焊盘34由金属材料(例如铜)制成,并伸出到第三表面s3上。此外,例如铜的导电路径30将每个内部焊盘32连接到对应的外部焊盘34,或者连接到在对应的垂直连接区域24的第一表面s1上伸出的部分。在这种连接中,在垂直连接区域24的第二表面s2上伸出的部分被设计为电连接到pcb(印刷电路板),未示出。31.电声模块1还包括多个金属材料柱36,其从第三表面s3在垂直于第一、第二和第三表面s1、s2、s3的方向上延伸。例如,每个柱36具有近似圆柱形的形状。此外,每个柱36在相应的第一端处接触对应的外部焊盘34。32.电声模块1还包括结构38,在下文中被称为换能结构38。33.换能结构38包括由第四表面s4界定的多层区域39,第四表面s4以一定距离面向第三表面s3和第五表面s5。34.举例来说,多层区域39包括钝化层41a、第一介电层41b、半导体层41c和第二介电层41d,现在参考图1中的电声模块1所假定的取向来描述它们。钝化层41a、第一介电层41b、半导体层41c和第二介电层41d可以被称为多层结构或多层区域。35.详细而言,保护层41a形成第四表面s4,并且例如是氮化硅。此外,第一介电层41b在与其直接接触的钝化层41a下方延伸,并且例如是氧化硅。半导体层41c在与其直接接触的第一介电层41b下方延伸。第二介电层41d例如是氧化硅。此外,第二介电层41d在与其直接接触的半导体层41c的下方延伸,并形成第五表面s5。36.换能结构38还包括半导体衬底42,其在与其直接接触的第二介电层41d下方延伸。此外,半导体衬底42的下方由第六表面s6界定,并横向界定向下开口的多个腔体52,此外该半导体衬底42的顶部由第二介电层41d的对应部分界定。37.更详细地,每个腔体52具有例如圆柱形的形状。此外,多层区域39的伸出到对应的腔体52上的部分作用为膜(标示为40),而半导体衬底42作用为(近似地)不可变形的框架,膜40被固定到该框架。38.在这并不意味着失去一般性的情况下,图1中示出了四个膜40。例如,在俯视图中,半导体衬底42可以具有矩形包壳。39.如先前所提及的,由多层区域39和半导体衬底42形成的整体的厚度(标示为wtot)不大于50μm。此外,多层区域39的厚度以及因此膜40的厚度也可以被包括在例如5μm和7μm之间,在这种情况下,半导体衬底42的厚度(标示为wend)例如被包括在43μm和47μm之间。40.换能结构38还包括多个金属材料的焊盘50(例如,由alcu区域和由ti、cu和ni的堆叠件形成的凸块下金属化来形成),被称为驱动焊盘50。在这方面,为了简化表示,驱动焊盘50被示为在钝化层41a上延伸,即使每个驱动焊盘50的至少一部分可以在钝化层41a内部延伸。41.每个驱动焊盘50接触对应的柱36。因此,每个柱36被插入在对应的外部焊盘34和对应的驱动焊盘50之间。42.电声模块1还包括密封区域53,其例如由苯并环丁烯(bcb)制成并且在多层区域39和再分布结构26的介电区域28之间延伸,以便横向界定封闭腔体55,此外,该封闭腔体55由第三和第四表面s3、s4界定。柱36在封闭腔体55内延伸。另外,密封区域53延伸以便横向围绕与其直接接触的多层区域39。43.电声模块1还包括多个致动器56。举例来说,电声模块1包括用于每个膜40的致动器56。每个致动器56在封闭腔体55中延伸,与对应的膜40接触。换言之,每个致动器56由对应的膜40承载。44.更详细地,每个致动器56包括相应的压电区域70和相应的保护区域72,以及电连接到对应的驱动焊盘50的一对电极(未示出)。保护区域72覆盖压电区域70,并且例如,它可以是与钝化层41a的材料相同的材料,例如,它可以与钝化层41a形成单个单块区域,该单块区域包覆压电区域70和对应的电极。此外,在保护区域72和第三表面s3之间存在距离w,例如被包括在3μm和5μm之间。45.如先前所提及,并且在这并不意味着失去一般性的情况下,每个致动器56电耦接到一对驱动焊盘50,并且因此电耦接到第一管芯2或第二管芯4的一对对应凸块。具体地,该电耦接通过对应的柱36、以及对应的外部焊盘34、对应的导电路径30和对应的内部焊盘32获得。以这种方式,例如,假设致动器56连接到第一管芯2,它能够以第一时间间隔接收由第一管芯2的发射电路10所生成的电命令信号,这导致与上述致动器56机械耦接的膜40的对应变形,从而生成声波。此外,在与第一时间间隔不同的第二时间间隔中,由于(例如)撞击在其上的声学回波信号的膜40的变形致使致动器56的对应变形,其生成电响应信号,该电响应信号由第一管芯2的接收电路12接收,接收电路12可以对其进行处理,然后通过对应的垂直连接区域24将对应的输出信号提供给外部计算机(未示出)。46.换言之,在本示例中,致动器56的一部分以及因此对应的膜40的一部分电耦接到第一管芯2,而致动器56的另一部分以及因此对应的膜40的另一部分电耦接到第二管芯4。在这并不意味着失去一般性的情况下,每个膜40都连接到对应的管芯的发射电路和接收电路。47.综上所述,电声模块1可以根据下文描述的工艺来制造。48.如图2中所示,以本身已知的方式形成组件74,在下文中称为asic组件74。49.asic组件74包括多个单元部分76,单元部分76彼此相同并且横向交错(在图2中以虚线仅突出显示了其中一个);术语“单元”精确地指代这些部分表示彼此相同并在空间中重复的单元(相当于基本部分)这一事实。多个单元部分76可以被称为第一单元部分。50.详细地,单元部分76在图3中被示出并在下文中进行描述——限于与图1中所示的不同之处。此外,除非另有说明,否则图1中已经示出的元件标示为相同的附图标记。51.更详细地,单元部分76与电声模块1的在第二表面s2和第三表面s3之间延伸的部分相同,如图1中所示,但是在下文中强调了不同之处。52.在这里用122标示的涂层区域在asic组件74的单元部分76之间共享;即,该涂层区域形成asic组件74的单个区域。此外,再分布结构的介电区域(在这里分别标示为128和126,并且在下文中分别被称为组件介电区域128和组件再分布结构126)在asic组件74的单元部分76之间共享。此外,第一、第二和第三表面在asic组件74的单元部分76之间共享;即,它们各自分别表示第一晶片表面s1'、第二晶片表面s2'和第三晶片表面s3'的一部分。53.此外,在单元部分76上延伸的是(例如玻璃的)支撑件75(图2中未示出),其在asic组件74的单元部分76之间共享。此外,以直接接触的方式在每个外部焊盘34下方延伸的是对应的初步接触元件37a,其是导电材料(例如,铜、镍和snagcu合金的堆叠件)。此外,初步接触元件37a被设计为形成对应的柱36,如在下文所解释。初步接触元件37a例如由对应的凸块形成,并且因此具有大致的圆柱形形状。54.在这并不意味着失去一般性的情况下,asic组件74的制造可以通过所谓的fowlp(扇出晶片级封装)类型的加工技术以本身已知的方式来执行。在这方面,单元部分76的第一和第二管芯2、4可以采用所谓的晶片级制造技术以本身已知的方式来制造,晶片级制造技术使得能够从同一半导体晶片(未示出)开始制造多个管芯,然后通过切割操作将所述管芯彼此分离。在可能的测试步骤之后,如此形成的管芯通过与组件再分布结构126的耦接而再次机械地耦接在一起,从而精确地形成asic组件74。55.在实践中,asic组件74由在先前单片化之后固定在一起的管芯组件来形成,以使得所述组件与晶片的形状具有第一近似,在某种意义上,它可以被设置在适当加工的半导体晶片的顶部,如下文所述。换言之,asic组件74表示一种重构晶片。此外,asic组件74的管芯共享单个再分布结构,该结构由组件再分布结构126精确地形成。56.此外,本制造工艺设想了半导体材料的晶片80的加工,如图4中所示,在下文中被称为mems晶片80。57.详细地,mems晶片80包括半导体本体82,其由设计为形成第五表面s5的相应的第一本体表面sa和相应的第二本体表面sb界定。半导体本体82具有至少等于例如400μm(例如等于775μm)的厚度wstart,以使得能够用现今的机械处理mems晶片80,而不会有损坏mems晶片80的风险。58.参考图4中mems晶片80所假定的取向,在第一本体表面sa上方延伸的是彼此相同的多个相应单元部分84(其中两个在图4中被示出)。多个相应单元部分84可以被称为第二单元部分。59.除了下文概述的不同之处,每个单元部分84与换能结构38相同。具体地,单元部分84没有半导体衬底42并且在半导体本体82上延伸,以使得相应的第二介电层41d在第一本体表面sa上延伸。此外,每个单元部分84包括多个相应的初步接触元件37b,其以直接接触的方式覆盖在对应的驱动焊盘50上,并且该初步接触元件37b是导电材料(例如,铜、镍和金的堆叠件)。此外,mems晶片80的初步接触元件37b例如由具有近似圆柱形的形状的对应的凸块形成,并且被设计成如下文所解释地与asic组件74的初步接触元件37a一起形成对应的柱36。60.假设具有平行于第一本体表面sa和第二本体表面sb的平面xy的正交参考系xyz,初步接触元件37b延伸到沿轴线z测量的高度,该高度大于致动器56的保护区域72延伸到的高度。61.再次如在图4中可以看到的,单元部分84相对于下面的半导体本体82而相对于彼此横向交错,以使得单元部分84的多层区域39横向界定腔体90(在下文中被称为晶片腔体90)。晶片腔体90还在第一本体表面sa下方、半导体本体82内部分地延伸。晶片腔体90可以被称为晶片凹部。62.接下来,如图5中所示,将mems晶片80以使第一本体表面sa面向支撑件200的取向设置在例如由第一带形成的支撑件200上。具体地,mems晶片80的初步接触元件37b接触支撑件200。63.然后,如图6中所示,从第二本体表面sb开始对半导体本体82进行研磨,以便均匀地减小其厚度。具体地,在研磨结束时,半导体本体82具有前述厚度wend。此外,半导体本体82在顶部处由第三本体表面sc界定,第三本体表面sc将形成第六表面s6。64.然后,如图7中所示,例如通过光刻或激光烧蚀,在半导体本体82上形成光刻胶掩模202。掩模202横向界定多个第一工艺开口204以及第二工艺开口206,每个第一工艺开口204在一定距离处覆盖对应的致动器56,第二工艺开口206在一定距离处覆盖晶片腔体90。65.接下来,如图8中所示,通过掩模202执行干式蚀刻,以便选择性地去除半导体本体82的伸出到第一工艺开口204上或第二工艺开口206上的部分。66.具体地,去除半导体本体82的伸出到第一工艺开口204上的部分导致第二介电层41d的与第一工艺腔体204垂直对齐的部分暴露,并且因此形成腔体52,并且释放膜40。腔体52可以被称为凹部。在这方面,第二介电层41d作用为干法蚀刻的停止层。67.此外,由于半导体本体82的伸出到第二工艺开口206上的部分被插入在晶片腔体90和第二工艺开口206之间,其去除需要将半导体本体82单片化成被腔体52穿过的对应换能结构38的多个半导体衬底42。在实践中,mems晶片80被分成形成对应换能结构38的多个管芯,此外,这些换能结构38耦接到对应的初步接触元件37b。68.接下来,以本身已知的方式(并且因此未被示出)例如通过所谓的等离子灰化工艺去除掩模202。69.然后,如图9中所示,换能结构38从支撑件200被去除并且机械和电耦接到asic组件74。70.特别地,每个换能结构38耦接到asic组件74的对应单元部分76。间隙299横向分开换能结构38。具体地,间隙299由半导体衬底42和多层区域39横向界定,并且伸出到组件再分布结构126的第三晶片表面s3'的下方部分上。71.更详细地,以本身已知的方式,将换能结构38的每个初步接触元件37b焊接到asic组件74的对应单元部分76的对应初步接触元件37a以便形成对应的柱36,因此柱36可以是不同的材料。在这方面,在图9中,每个柱36被示出为通过并置换能结构38的对应初步接触元件37b和对应单元部分76的对应初步接触元件37a形成,即便可以设想利用焊膏(未示出)涂敷换能结构38的上述对应初步接触元件37b和对应单元部分76的上述初步接触元件37a中的至少一个的至少一部分进行焊接。在随后的图中,柱36反而作为一个整体而被示出。72.更详细地,为了形成柱36,可以实现相对于asic组件74而临时保持换能结构38的技术,并且因此可以使用随后在焊接期间蒸发的固定材料。此外,可以应用不使用助焊剂的焊接技术来防止任何可能的污染。73.如图10中所示,在机械耦接之后,间隙299至少部分地填充有接合区域92,该接合区域92被设计为形成密封区域53并且该接合区域92例如是bcb(苯并环丁烯)。在将换能结构38耦接到asic组件74之前,在asic组件74上形成接合区域92的变形在任何情况下都是可能的。74.在这并不意味着失去一般性的情况下,接合区域92因此在由多层区域39横向界定的间隙299的部分中延伸,直到组件再分布结构126的下方部分被接触,从而横向封闭每个换能结构38的对应封闭腔体55。75.实际上,asic组件74、换能结构38和接合区域92形成多管芯组件94。76.接着,如图11中所示,去除asic组件74的支撑件75(可能甚至在换能结构38耦接到asic组件74之前进行去除)并且多管芯组件94被翻转并被布置在第二带229上。然后,沿着穿过接合区域92的切割线99(在图11中用虚线示意性地指出)执行切割操作,这需要从多管芯组件94开始对多个电声模块1进行单片化。接合区域92的剩余部分形成密封区域53。77.即使未详细示出或描述,在执行切割操作之前,也可以执行另外的操作,诸如在asic组件74的垂直连接区域24上执行球附着操作。78.根据图12中所示的不同实施例,在mems晶片80的半导体本体82内延伸的是多个埋置介电区域86,其例如是氧化硅,并且共面。例如,mems晶片80可以包括与单元部分84的数目相等的埋置介电区域86的数目,该埋置介电区域86在距第一本体表面sa一定距离处延伸。此外,每个埋置介电区域86横向界定与电声模块1的膜40的数目相等的半导体本体82(图12中以虚线示出)的部分88的数目,以下称为填充部分88。此外,埋置介电区域86相对于覆盖晶片腔体90横向交错。79.在这种情况下,如图13中所示,制造工艺设想mems晶片80以与参考图5所述相同的方式被布置在支撑件200上。80.然后,如图14中所示,从底部表面sb开始对半导体本体82进行机械研磨,以暴露埋置介电区域86。81.半导体本体82的剩余部分现在由第四本体表面sd界定。因此埋置介电区域86和填充部分88伸出到第四体表面sd上。82.接下来,如图15中所示,执行蚀刻,其中埋置介电区域86(现在被暴露)作用为硬掩模。以这种方式,除了半导体本体82的下方部分之外,填充部分88被选择性地去除,直到作用为蚀刻停止层的换能结构38的第二介电层41d的下方部分被暴露。因此形成腔体52,并且因此膜40被释放。83.此外,半导体本体82的插入在埋置介电区域86之间并覆盖晶片腔体90的部分被去除;这种去除需要以与参考图8描述的相同的方式将半导体本体82单片化成对应的换能结构38的多个半导体衬底42。然后该工艺如参考图9-图11描述的那样进行。84.根据图16中所示的另一变形,在参考图6描述的研磨之后,对mems晶片80进行机械加工,以便为每个单元部分84形成对应的多个凸块300,凸块300在第三本体表面sc上延伸。在这种情况下,柱36可以不存在,并且因此保护区域72可以接触支撑件200。85.此外,每个单元部分84包括多个相应的tsv(硅通孔)类型的垂直导电连接件,被称为tsv 302。每个tsv 302将对应的驱动焊盘50电连接到对应的凸块300,并且因此延伸穿过半导体本体82和多层区域39两者。tsv 302因此伸出到第三本体表面sc上。86.然后,如图17中所示,在半导体本体82上(通过沉积和光刻/激光烧蚀)形成掩模(在这里标示为402),其再次界定第一工艺开口204和第二工艺开口206,并且此外涂覆整个凸块300,以便在随后的蚀刻工艺中保护它们。87.然后,如图18中所示,该工艺以与参考图8所述相同的方式进行,以便形成腔体52,释放膜40,并将在这里标示为338的换能结构单片化。接下来,掩模402被去除。88.然后,如图19中所示,换能结构338从支撑件200被去除并且机械和电耦接到asic组件74。89.具体地,每个换能结构338耦接到asic组件74的对应单元部分76;间隙(在这里标示为399)横向分开换能结构338。90.相对于图9中所示的,换能结构338被倒置;即,它们具有第六表面s6,凸块300布置在第六表面s6上,面向asic组件74。91.更详细地,每个换能结构338的每个凸块300接合到asic组件74的对应单元部分76的对应初步接触元件37a,以便形成对应的柱,在这里用336指明,参考图9所述的柱36表达的相同考虑适用于该柱。92.然后,制造工艺以与参考图9所示的实施例所描述的相同方式进行。93.本制造工艺所提供的优点从前面的描述中清楚地显现出来。94.具体地,本工艺设想在与包括asic的重构晶片执行耦接之前,对mems晶片80的半导体本体进行机械加工以减小厚度并释放膜。换言之,换能结构首先从mems晶片开始被单片化,然后分别耦接到asic组件74;以这种方式,不执行晶片对晶片类型的接合,从而减少了翘曲现象,并且在包括asic组件74和换能结构38的堆叠件上不执行蚀刻。95.最后,很明显,可以对本文描述和说明的制造工艺进行修改和变形,而不偏离如所附权利要求中定义的本公开的范围。96.例如,初步接触元件37a、37b可以具有与已经描述的形状不同的形状;例如,即使未被示出,但是除了前面讨论的圆柱形部分之外,它们中的每一个都可以包括被布置在圆柱形部分上的相应的尖端或叶片部分。97.可以使用其他导电接触元件代替凸块18、20,诸如对应的柱。更一般地,本文描述的所有导电接触元件仅作为示例而被提供。98.此外,可以设想形成asic组件74的初步接触元件37a,但不形成mems晶片80的初步接触元件37b,在这种情况下,asic组件74的初步接触元件37a被接合到驱动焊盘50。同样,可以设想形成mems晶片80的初步接触元件37b,但不形成asic组件74的初步接触元件37a,在这种情况下,mems的初步接触元件37b晶片80接合到外部焊盘34。99.同样,在图16-图19中所示的实施例的情况下,可以不形成asic组件74的初步接触元件37a,在这种情况下,柱336通过将凸块300焊接到外部焊盘34来获得。替代地,可以存在初步接触元件37a,但是不存在凸块300,在这种情况下,初步接触元件37a被设置为与对应的tsv 302接触。100.此外,每个电声模块可以包括与所示的管芯不同的多个管芯,在这种情况下,制造工艺被相应地修改。发射电路和接收电路可以形成在不同的管芯中。在这种情况下,可以使用不同的技术来形成发射电路和接收电路。101.一般来说,致动器可以是不同于已描述的类型的致动器。例如,致动器可以实现电容类型的致动机制,而不是压电类型的致动机制。102.如先前所提及,由多层区域39和半导体衬底42形成的整体的厚度wtot也可以小于50μm;例如,厚度wtot可以不超过30μm。103.此外,图16-图19中所示类型的实施例也是可能的,但是其中使用图12中所示类型的埋置介电区域代替掩模402,凸块300在该埋置介电区域内部延伸。104.最后,在存在埋置介电区域86的实施例中,研磨可以使得后者不被暴露,更确切地为保持被半导体本体82的一部分掩盖,然后在随后的蚀刻操作期间被去除。105.一种用于制造电声模块(1)的方法,可以被概括为包括:形成组件(74),其包括介电涂层区域(122);相对于彼此横向交错的多个单元部分(76),多个单元部分中的每一个单元部分包括被布置在介电涂层区域(122)中的至少一个相应的管芯(2,4);以及电耦接到管芯(2、4)的再分布结构(126),介电涂层区域(122)和再分布结构(126)被布置在彼此上;所述方法还可以包括形成晶片(80),该晶片(80)包括厚度等于初始厚度(wstart)的半导体本体(82),以及相对于彼此横向交错的多个相应单元部分(84),多个相应单元部分(84)中的每一个相应单元部分包括被布置成与半导体本体(82)接触的相应支撑区域(39)和与支撑区域(39)接触的多个相应致动器(56);将晶片(80)的半导体本体(82)的厚度减小到最终厚度(wend);然后选择性地去除部分半导体本体(82),以便从晶片(80)开始单片化多个换能结构(38;338),多个换能结构中的每一个换能结构包括相应的半导体衬底(42),其接触相应的支撑区域(39)并被由支撑区域(39)的对应部分界定的多个相应的腔体(52)穿过,该对应部分形成与对应的一个致动器(56)机械耦接的对应膜(40);然后将换能结构(38;338)耦接到组件(74)的再分布结构(126)。106.形成晶片(80)可以包括形成晶片腔体(90),其在支撑区域(39)之间延伸,并且此外部分地延伸到半导体本体(82)中;并且选择性地去除部分半导体本体(82)可以包括:去除与支撑区域(39)的对应部分接触的半导体本体(82)的第一部分,以便形成所述腔体(52),以及去除半导体本体(82)的伸出到晶片腔体(90)上的第二部分,以便单片化该换能结构(38;338)。107.在减小厚度之后,半导体本体(82)可以由相应的内表面(sa)和相应的外表面(sc)界定,支撑区域(39)接触内表面(sa);所述方法可以包括在半导体本体(82)的外表面(sc)上形成掩模(202;402),并且以通过所述掩模(202)执行蚀刻的方式去除半导体本体(82)的所述第一和第二部分。108.对于每一个相应单元部分(84),晶片(80)可以包括在半导体本体(82)内延伸的对应埋置介电区域(86),所述方法还可以包括:通过所述减小晶片(80)的半导体本体(82)的厚度来暴露埋置介电区域(86);然后使用埋置介电区域(86)作为掩模而去除半导体本体(82)的所述第一和第二部分。109.再分布结构(126)可以包括介电再分布区域(128),其可以由与介电涂层区域(122)相对的相应外表面(s3')界定;并且组件(74)的每个单元部分(76)还可以包括多个第一焊盘(34),第一焊盘(34)伸出到介电再分布区域(128)的外表面(s3')上;以及多个导电再分布路径(30,32),其延伸穿过介电再分布区域(128)并将第一焊盘(34)电耦接到所述至少一个管芯(2,4);并且晶片(80)可以包括多个第二焊盘(50),其被布置在支撑区域(39)上,并电耦接到致动器(56),所述方法还可以包括对于从以下之间执行至少一个步骤:对于组件(74)的每一个单元部分(76),形成多个第一导电接触元件(37a),其从对应的一个第一焊盘(34)相对于介电再分布区域(128)在相反方向上延伸;并且对于晶片(80)的每一个单元部分(84),形成多个第二导电接触元件(37b),其从对应的一个第二焊盘(50)相对于半导体本体(82)在相反方向上延伸;以及将换能结构(38)耦接到组件(74)的再分布结构(126)可以包括:通过在可以执行形成第一和第二导电接触元件(37a、37b)的步骤的情况下执行将每一个第一导电接触元件(37a)焊接到对应的第二导电接触元件(37b)的步骤来形成电接触(36),每一个电接触(36)在对应的第一焊盘(34)和对应的第二焊盘(50)之间延伸;如果可以执行形成第一导电接触元件(37a)的步骤,然而可以不执行形成第二导电接触元件(37b)的步骤,将每一个第一导电接触元件(37a)焊接到对应的第二焊盘(50);如果可以执行形成第二导电接触元件(37b)的步骤,然而可以不执行形成第一导电接触元件(37a)的步骤,将每一个第二导电接触元件(37b)焊接到相应的第一焊盘(34)。110.再分布结构(126)可以包括介电再分布区域(128),该介电再分布区域(128)可以由与介电涂层区域(122)相对的相应外表面(s3')界定,组件(126)的每一个单元部分(76)74)还可以包括多个第一焊盘(34),其伸出到介电再分布区域(128)的外表面(s3')上;以及多个第一导电再分布路径(30,32),其延伸穿过介电再分布区域(128)并将第一焊盘(34)电耦接到所述至少一个管芯(2,4);并且在厚度减小之后,半导体本体(82)可以由相应的内表面(sa)和相应的外表面(sc)界定,支撑区域(39)接触内表面(sa);所述方法还可以包括形成多个硅通孔(302),其延伸穿过半导体本体(82),直到外表面(sc),并且可以电耦接到致动器(56),以及从其之间执行至少一个步骤:对于组件(74)的每一个单元部分(76),形成多个第一导电接触元件(37a),其从对应的第一焊盘(34)相对于介电再分布区域(128)在相反方向上延伸;并且对于晶片(80)的每个单元部分(84),在半导体本体(82)的外表面(sc)上形成对应的多个第三导电接触元件(300),每个第三导电接触元件(300)可以电耦接到对应的硅通孔(302);以及将换能结构(338)耦接到组件(74)的再分布结构(126)可以包括在每个第一焊盘(34)和对应的硅通孔(302)之间形成对应的电接触(336),其包括对应的第一导电接触元件(37a)和/或第三导电接触元件(300)。111.将换能结构(38;338)耦接到组件(74)的再分布结构(126)可以包括将换能结构(38;338)横向交错布置并由间隙(299;399)隔开;所述方法还可以包括在间隙(299;399)中形成接合区域(92),该接合区域(92)为每个换能结构(38;338)横向界定对应的封闭腔体(55),此外该封闭腔体还可以由对应的支撑区域(39)和介电再分布区域(128)的对应部分来界定;然后沿着横穿接合区域(92)的切割线来执行切割操作。112.所述初始厚度(wstart)可以至少等于400μm,并且所述最终厚度(wend)与支撑区域(39)的厚度之和可以不大于50μm。113.每个支撑区域(39)可以包括至少一个介电层(41d)。114.致动器(56)可以是压电类型的。115.可以组合上述各种实施例以提供另外的实施例。如果需要,可以修改实施例的各方面以采用各种专利、申请和出版物的概念以提供其他的实施例。116.可以根据以上详细描述对实施例进行这些和其他改变。一般而言,在以下权利要求中,所使用的术语不应被解释为将权利要求限制为在说明书和权利要求中公开的特定实施例,而应被解释为包括所有可能的实施例及这些权利要求所享有的等同物的全部范围。因此,权利要求不受本公开的限制。

本文地址:https://www.jishuxx.com/zhuanli/20240726/123830.html

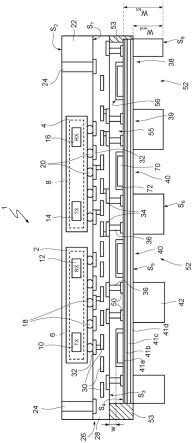

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。