基于SOI硅晶圆的平板电容式MEMS器件制造封装方法及MEMS器件与流程

- 国知局

- 2024-07-27 13:06:13

本发明涉及平板电容式mems器件,具体涉及一种基于soi硅晶圆的平板电容式mems器件制造封装方法及mems器件。

背景技术:

1、目前,常见的平板电容式mems器件,由于平板电容结构特性,上下极板往往分别利用两个硅晶圆单独制造,再利用键合工艺键合在一起,这种方式对键合的对准精度要求较高,而且依赖于键合工艺强度,一旦强度降低,容易造成器件失效。

2、另外,现有电信号的封装通常采用外接引线的方式,随着mems器件结构的逐渐复杂化,采用外接引线的方式已经满足不了mems器件的电信号封装需求。tsv作为一种新型的电信号连接方式,受到广泛关注。

3、目前已有通过填充深孔的方式形成导电通路制造tsv晶圆,但是,存在深孔填充不完全和掺杂离子引入复杂等问题,导致成品率下降。同时,tsv晶圆较为孤立,需要将mems器件通过键合工艺键合到tsv上,对键合的对准精度和键合强度要求较高。

技术实现思路

1、针对平板电容式mems器件制作工艺复杂的问题,本申请提供一种基于soi硅晶圆的平板电容式mems器件制造封装方法及mems器件,利用soi晶圆的顶层硅和衬底硅分别制作平板电容式mems器件的上下极板,实现器件晶圆和封装晶圆二合一,省去了键合工艺,降低对准难度,同时将封装用的tsv作为平板电容式器件下极板,融入到整体制造中。

2、本发明提供的技术方案如下:

3、本发明提供一种基于soi硅晶圆的平板电容式mems器件制造封装方法,包括步骤:

4、提供一soi硅晶圆,所述soi硅晶圆自上而下依次包括顶层硅、埋氧层和衬底硅;

5、通过涂光刻胶将平板电容式mems器件的下极板图案涂于衬底硅上,利用光刻胶作为掩膜,刻蚀衬底硅,于衬底硅上形成多个底部深孔;

6、将所述soi硅晶圆热氧化处理,使所述衬底硅的表面、顶层硅的表面及底部深孔的孔壁分别形成氧化硅层,并于所述衬底硅的氧化硅层上及顶层硅的氧化硅层上分别沉积非晶硅或多晶硅,形成表面沉积层,及填充所述底部深孔形成粘结柱;

7、去除衬底硅表面沉积层和顶层硅表面沉积层中的非晶硅或多晶硅,并于衬底硅的氧化硅层上沉积氮化硅,形成氮化硅层;

8、刻蚀衬底硅表面的氮化硅层和氧化硅层,使衬底硅暴露,且暴露的衬底硅中不存在粘结柱;

9、于暴露的衬底硅表面制作金属凸点;

10、于衬底硅的表面沉积一层惰性保护层,所述惰性保护层覆盖衬底硅表面的氮化硅层和金属凸点;

11、于顶层硅的氧化硅层上刻蚀平板电容式mems器件的上极板图案,并继续刻蚀顶层硅至埋氧层,顶层硅被刻蚀成多个分离体;

12、腐蚀顶层硅上的氧化硅层、各分离体上的氧化硅层、暴露的埋氧层及分离体与衬底硅之间的埋氧层,使分离体释放,形成平板电容式mems器件的上极板;

13、去除衬底硅表面的惰性保护层,使金属凸点暴露,金属凸点对应的衬底硅形成平板电容式mems器件的下极板。

14、进一步优选地,利用深反应离子刻蚀工艺对衬底硅进行刻蚀,形成底部深孔。

15、进一步优选地,利用低压化学气相沉积工艺于所述衬底硅的氧化硅层上及顶层硅的氧化硅层上分别沉积非晶硅或多晶硅,及填充所述底部深孔。

16、进一步优选地,利用反应离子刻蚀工艺去除衬底硅表面沉积层和顶层硅表面沉积层中的非晶硅或多晶硅。

17、进一步优选地,利用等离子增强化学气相沉积工艺于衬底硅的氧化硅层上沉积氮化硅,形成氮化硅层。

18、进一步优选地,利用反应离子刻蚀工艺刻蚀衬底硅表面的氮化硅层和氧化硅层,使衬底硅暴露。

19、进一步优选地,使用剥离工艺于暴露的衬底硅表面制作金属凸点。

20、进一步优选地,利用反应离子刻蚀工艺于顶层硅的氧化硅层上刻蚀平板电容式mems器件的上极板图案,并继续刻蚀顶层硅至埋氧层。

21、进一步优选地,利用氢氟酸腐蚀顶层硅上的氧化硅层、各分离体上的氧化硅层、暴露的埋氧层及分离体与衬底硅之间的埋氧层。

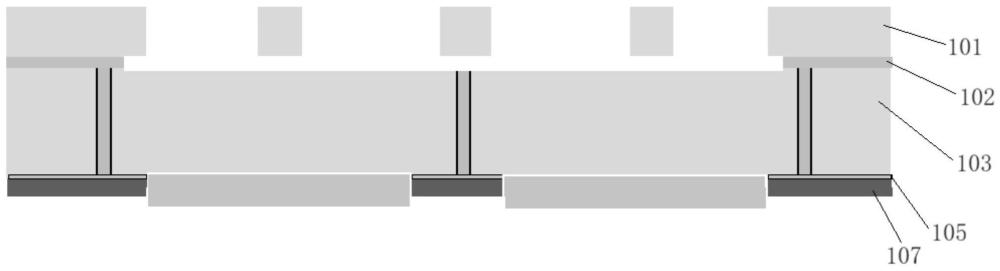

22、本发明还提供一种平板电容式mems器件,包括:soi硅晶圆;

23、所述soi硅晶圆自上而下依次包括顶层硅、埋氧层和衬底硅;

24、所述顶层硅经刻蚀,埋氧层经腐蚀,形成平板电容式mems器件的上极板;

25、所述衬底硅经刻蚀形成平板电容式mems器件的下极板;

26、所述衬底硅于各下极板之间开设有底部深孔,所述底部深孔的孔壁形成有氧化硅层,所述底部深孔的孔内填充有非晶硅或多晶硅,以形成各下极板之间的粘结柱;

27、所述衬底硅的表面相对于粘结柱叠加设置有氧化硅层和氮化硅层,所述衬底硅的表面相对于下极板设置有金属凸点,所述氧化硅层和氮化硅层于相邻金属凸点之间形成绝缘隔离层。

28、依据上述实施例的平板电容式mems器件制造封装方法及平板电容式mems器件,利用soi晶圆的顶层硅制作平板电容式mems器件的上极板,利用soi晶圆的衬底硅制作平板电容式mems器件的下极板,实现器件晶圆和封装晶圆二合一,省去了键合工艺,降低对准难度,本申请将封装用的tsv作为平板电容式器件下极板,融入到整体制造中,且将tsv的硅通孔中填充非晶硅或多晶硅,使硅通孔形成粘结柱,达到粘连功能,而非导电功能,避免在硅通孔填充不完全和掺杂离子引入复杂等问题,大大提升了tsv的成品率。

技术特征:1.一种基于soi硅晶圆的平板电容式mems器件制造封装方法,其特征在于,包括步骤:

2.如权利要求1所述的平板电容式mems器件制造封装方法,其特征在于,利用深反应离子刻蚀工艺对衬底硅进行刻蚀,形成底部深孔。

3.如权利要求1所述的平板电容式mems器件制造封装方法,其特征在于,利用低压化学气相沉积工艺于所述衬底硅的氧化硅层上及顶层硅的氧化硅层上分别沉积非晶硅或多晶硅,及填充所述底部深孔。

4.如权利要求1所述的平板电容式mems器件制造封装方法,其特征在于,利用反应离子刻蚀工艺去除衬底硅表面沉积层和顶层硅表面沉积层中的非晶硅或多晶硅。

5.如权利要求1所述的平板电容式mems器件制造封装方法,其特征在于,利用等离子增强化学气相沉积工艺于衬底硅的氧化硅层上沉积氮化硅,形成氮化硅层。

6.如权利要求1所述的平板电容式mems器件制造封装方法,其特征在于,利用反应离子刻蚀工艺刻蚀衬底硅表面的氮化硅层和氧化硅层,使衬底硅暴露。

7.如权利要求1所述的平板电容式mems器件制造封装方法,其特征在于,使用剥离工艺于暴露的衬底硅表面制作金属凸点。

8.如权利要求1所述的平板电容式mems器件制造封装方法,其特征在于,利用反应离子刻蚀工艺于顶层硅的氧化硅层上刻蚀平板电容式mems器件的上极板图案,并继续刻蚀顶层硅至埋氧层。

9.如权利要求1所述的平板电容式mems器件制造封装方法,其特征在于,利用氢氟酸腐蚀顶层硅上的氧化硅层、各分离体上的氧化硅层、暴露的埋氧层及分离体与衬底硅之间的埋氧层。

10.一种平板电容式mems器件,其特征在于,包括:soi硅晶圆;

技术总结一种基于SOI硅晶圆的平板电容式MEMS器件制造封装方法及平板电容式MEMS器件,利用SOI晶圆的顶层硅制作平板电容式MEMS器件的上极板,利用SOI晶圆的衬底硅制作平板电容式MEMS器件的下极板,实现器件晶圆和封装晶圆二合一,省去了键合工艺,降低对准难度,本申请将封装用的TSV作为平板电容式器件下极板,融入到整体制造中,且将TSV的硅通孔中填充非晶硅或多晶硅,使硅通孔形成粘结柱,达到粘连功能,而非导电功能,避免在硅通孔填充不完全和掺杂离子引入复杂等问题,大大提升了TSV的成品率。技术研发人员:胡嘉豪受保护的技术使用者:上海镭望光学科技有限公司技术研发日:技术公布日:2024/6/23本文地址:https://www.jishuxx.com/zhuanli/20240726/124931.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表