时间数字转换器、处理周期信号的方法和信号处理系统与流程

- 国知局

- 2024-07-30 09:36:34

时间数字转换器、处理周期信号的方法和信号处理系统1.要求优先权本专利申请涉及2021年9月30日提交的名称为“time-to-digital converter (tdc) architecture for measuring phase differences among multiple clocks”(“用于测量多个时钟之间相位差的时间-数字转换器(tdc)体系结构”)的印度临时专利申请,申请号:in 202141044473,并且要求该临时专利申请的优先权,其全文以与本文描述一致的程度并入本文。2.本专利申请还涉及2022年5月10日提交的名称为“time-to-digital converter(tcd) to operate with input clock signals with jetter”(“利用具有抖动的输入时钟信号操作的时间数字转换器(tdc)”)的美国专利申请,申请号:us 17/662669,并且要求该美国专利申请的优先权,其全文以与本文描述一致的程度并入本文。3.相关申请本技术涉及与us 17/662669同日提交的名称为“counter design for a time-to-digital converter (tdc)”)(“时间数字转换器(tdc)的计数器设计”)的共同未决的美国专利申请,发明人debasish behera(德巴斯什·布哈拉)等人,其全部内容并入本文。4.本技术涉及us 17/662669同日提交的名称为“time-to-digital converter (tdc) measuring phase difference between periodic inputs”(“用于测量周期输入之间的相位差的时间数字转换器(tdc)”)的共同未决的美国专利申请,发明人debasish behera(德巴斯什·布哈拉)等人,其全部内容并入本文。技术领域5.本公开的实施方案总体涉及时间数字转换器(tdc),并且更具体地,涉及利用具有抖动的输入时钟信号操作的tdc。背景技术:6.tdc通常用于测量一对事件之间的时间间隔。测量值通常被量化为对应的数字值。这些事件通常是对应信号对的电压或逻辑电平变化。tdc应用于电子设备诸如锁相环(pll)、定时卡、tof(飞行时间)测量设备,诸如辐射探测器、诊断设备等中。7.tdc通常接收周期性输入信号,并且生成表示对应时刻的相位差的连续数字值。每个数字值表示两个周期性输入的(相同方向的)对应边沿之间的时间差。周期信号的示例包括时钟信号等。8.抖动通常与作为输入提供给tdc的时钟信号一起出现。抖动是指被引入至时钟信号的附加噪声分量,表现为与期望/标称周期的偏差。如相关技术中众所周知的,由于开关噪声、串扰、热噪声等原因而引入抖动。9.本公开的各方面涉及适于利用具有抖动的时钟信号来操作的tdc。技术实现要素:10.鉴于此,本技术提供一种时间数字转换器、处理周期信号的方法和信号处理系统。11.本技术公开一种时间数字转换器,所述时间数字转换器包括:计数逻辑,所述计数逻辑用于分别针对作为输入信号接收的第一周期信号和第二周期信号生成第一计数序列和第二计数序列,所述第一计数序列表示在时间尺度上出现具有所述第一周期信号的第一方向的第一边沿序列的相应时刻,所述第二计数序列表示在所述时间尺度上出现具有所述第二周期信号的所述第一方向的第二边沿序列的相应时刻;以及核心逻辑,所述核心逻辑用于通过处理所述第一计数序列和所述第二计数序列来识别所述第一周期信号和所述第二周期信号中的任一者中是否存在抖动。12.可选的,所述核心逻辑进行操作以在不存在抖动的情况下根据第一方法并且在存在抖动的情况下根据第二方法,来生成所述第一周期信号与所述第二周期信号之间的相位差序列。13.可选的,其中所述第二周期信号具有所述第一周期信号的频率的整数倍频率,其中所述核心逻辑还进行操作以:生成窗口边界序列,所述窗口边界序列标识在所述第一周期信号和所述第二周期信号二者中已出现所述第一方向的边沿的相应时刻,其中两个连续边界之间的持续时间构成窗口序列的对应窗口;从每个窗口中所述第二计数序列的相应计数子序列中减去所述第一计数序列的相应第一计数以生成每个窗口中的时间差序列,其中每个时间差具有对应符号和量值,其中所述第一方法包括通过在单独的累加器中合计正时间差和负时间差来计算所述相位差序列中的每个相位差,其中所述第二方法包括通过将所述正时间差和所述负时间差两者合计到单个累加器中来计算所述相位差序列中的每个相位差。14.可选的,其中当所述整数倍为一时以及当所述整数倍大于1时,所述时间数字转换器能够操作。15.可选的,其中所述核心逻辑包括:输入分析器模块,所述输入分析器模块用于根据所述第一计数序列和所述第二计数序列来生成所述窗口边界序列;以及输出发生器模块,所述输出发生器模块用于生成所述窗口序列中的每个窗口中的值序列中的一个值,其中所述值指示所述窗口的对应相位差。16.可选的,其中所述输出发生器模块包括:减法单元,所述减法单元用于为每个窗口生成所述时间差序列;正最小值发生器,所述正最小值发生器用于选择表示包含在所述时间差序列中的正值中的最小值的正最小值;负最大值发生器,所述负最大值发生器用于选择表示包含在所述时间差序列中的负值中的最大值的负最大值;第一累加器,所述第一累加器用于接收覆盖对应窗口的所述正最小值的序列,并且将所述正最小值的序列中的值相加以生成第一累加值;第二累加器,所述第二累加器用于接收覆盖所述对应窗口的所述负最大值的序列,并且将所述负最大值的所述序列中的值相加以生成第二累加值;以及抖动检测器模块,所述抖动检测器模块用于接收所述第一累加值和所述第二累加值,并且生成指示是否存在所述抖动的抖动存在信号,其中如果所述第一累加器和所述第二累加器二者的累加值都已超过相应阈值,则所述抖动检测器模块确定存在所述抖动。17.可选的,其中所述输出发生器模块包括:第一累加器输出模块,所述第一累加器输出模块用于接收所述第一累加值和所述第二累加值,并且当确定不存在抖动时,生成所述第一累加值和所述第二累加值的最小量值作为所述对应窗口的累加相位差。18.可选的,其中当确定存在所述抖动时,所述第一累加器和所述第二累加器中的一者被重置为边界值,其中所述重置的累加器此后累加每个窗口中具有较低量值的所述正最小值和所述负最大值中的一者,其中所述第一累加器输出模块将所述重置的累加器中的累加值转发为所述累加相位差。19.可选的,其中所述输出发生器模块还包括:窗口计数器,所述窗口计数器用于计数直至所述窗口的预先确定数量,其中所述第一累加器和所述第二累加器在所述窗口计数器计数直至所述窗口的所述预先确定数量时以及当所述抖动检测器模块检测到存在抖动时被重置,当确定存在抖动时,所述重置的累加器用于在再次检查后续时间差的抖动之前,对所述预先确定数量的所述窗口进行累加操作。20.可选的,还包括第二累加器输出模块,所述第二累加器输出模块用于确定在所述预先确定数量的窗口结束时接收到的所述第一累加值和所述第二累加值的较低量值,并且当不存在抖动时提供所述较低量值作为累加相位差,所述第二累加器输出模块用于当存在抖动时,将跨越所述预先确定数量的窗口数的所述重置的累加器的输出转发为所述累加相位差。21.本技术还公开一种在时间数字转换器中处理周期信号的方法,所述方法包括:分别接收第一周期信号和第二周期信号的第一计数序列和第二计数序列,所述第一计数序列表示在时间尺度上出现具有所述第一周期信号的第一方向的第一边沿序列的相应时刻,所述第二计数序列表示在所述时间尺度上出现具有所述第二周期信号的所述第一方向的第二边沿序列的相应时刻;以及检查所述第一计数序列和所述第二计数序列,以识别所述第一周期信号和所述第二周期信号中的任一者中是否存在抖动。22.可选的,当所述第一周期信号具有与所述第二周期信号相同的频率时,所述检查包括:从所述第二计数序列的对应计数中减去所述第一计数序列中的每个计数以形成差值序列;以及检查在所述差值序列中是否存在足够数量的正值和负值,以指示在所述两个周期信号中的一者中是否存在抖动。23.可选的,当所述第二周期信号具有所述第一周期信号的频率的整数倍频率时,所述检查包括:生成窗口边界序列,所述窗口边界序列标识在所述第一周期信号和所述第二周期信号二者中已出现所述第一方向的边沿的相应时刻,其中两个连续边界之间的持续时间构成窗口序列的对应窗口;从每个窗口中所述第二计数序列的相应计数子序列中减去所述第一计数序列的相应第一计数以生成每个窗口中的差值序列;识别所述差值序列中的正最小值和负最大值;将窗口序列的所述正最小值累加作为第一累加值,并且将所述窗口序列的所述负最大值累加作为第二累加值,当不存在抖动时,选择所述第一累加值和所述第二累加值的较小量值作为所述对应窗口的累加相位差。24.可选的,其中所述检查对所述第一累加值和所述第二累加值两者是否都已超过相应阈值进行检查,以推断是否存在抖动。25.可选的,当存在抖动时,还包括:将所述第一累加器和所述第二累加器中的一者重置为边界值,此后继续所述重置的累加器累加每个窗口中具有较低量值的所述正最小值和所述负最大值中的一者,其中所述重置的累加器转发所述累加值作为所述累加相位差。26.本技术还公开一种信号处理系统,所述信号处理系统包括:tdc,所述tdc用于生成表示作为输入信号接收的第一周期信号与第二周期信号之间的相应时刻的相位差的输出序列,其中所述tdc可操作用于识别所述第一周期信号和所述第二周期信号中的任一者中是否存在抖动,并且执行校正动作以减轻抖动在所述相位差的测量中的影响;以及处理模块,所述处理模块用于处理所述输出序列。27.可选的,还包括包含所述tdc的锁相环,并且所述处理模块进行操作,以使由所述输出序列表示的所述第一周期信号与所述第二周期信号之间的任何相位差最小化。28.可选的,其中所述tdc包括:计数逻辑,所述计数逻辑用于分别针对所述第一周期信号和所述第二周期信号生成第一计数序列和第二计数序列,所述第一计数序列表示在时间尺度上出现具有所述第一周期信号的第一方向的第一边沿序列的相应时刻,所述第二计数序列表示在所述时间尺度上出现具有所述第二周期信号的所述第一方向的第二边沿序列的相应时刻;以及核心逻辑,所述核心逻辑用于通过处理所述第一计数序列和所述第二计数序列来识别所述第一周期信号和所述第二周期信号中的任一者中是否存在抖动;其中所述核心逻辑进行操作以在不存在抖动的情况下根据第一方法并且在存在抖动的情况下根据第二方法,来生成所述第一周期信号与所述第二周期信号之间的所述输出序列。29.可选的,其中所述第二周期信号具有所述第一周期信号的频率的整数倍频率,其中所述核心逻辑还进行操作以:生成窗口边界序列,所述窗口边界序列标识在所述第一周期信号和所述第二周期信号二者中已出现所述第一方向的边沿的相应时刻,其中两个连续边界之间的持续时间构成窗口序列的对应窗口;从每个窗口中所述第二计数序列的相应计数子序列中减去所述第一计数序列的相应第一计数以生成每个窗口中的时间差序列,其中每个时间差具有对应符号和量值,其中所述第一方法包括通过在单独的累加器中合计正时间差和负时间差来计算所述输出序列中的每个输出,其中所述第二方法包括通过将所述正时间差和所述负时间差两者合计到单个累加器中来计算所述输出序列中的每个输出。30.可选的,其中当所述整数倍为一时以及当所述整数倍大于1时,所述tdc能够操作。31.本技术公开的时间数字转换器可以最小化在检测到抖动时,抖动对相位差测量的影响,提供相当准确的相位差。附图说明32.将参考下文简要描述的附图来描述本公开的示例性实施方案。33.图1是其中可以实现本公开的若干方面的示例性设备的框图。34.图2是示出在一个实施方案中的一对输入时钟中的抖动的时序图。35.图3a是示出根据本公开的一方面的时间数字转换器(tdc)利用具有抖动的输入时钟信号操作的方式的流程图。36.图3b是在本公开的一个实施方案中实现的核心逻辑的框图。37.图4a是在本公开的一个实施方案中实现的输入分析器模块的框图。38.图4b是在本公开的一个实施方案中实现的输出发生器模块的框图。39.图5是示出在本公开的一个实施方案中用于生成每个相位差值的唯一计数发生器和窗口标识模块的具体实施细节的框图。40.图6是示出在本公开的一个实施方案中针对具有相同频率的一对输入时钟生成信号unique-count和信号window-identifier的方式的时序图。41.图7是示出在本公开的一个实施方案中针对具有大于一的整数相关倍频率的一对输入时钟生成信号unique-count和信号window-identifier的方式的时序图。42.图8a是示出在本公开的一个实施方案中tdc针对具有相同频率的一对输入时钟的操作的时序图。43.图8b是示出在本公开的一个实施方案中tdc针对具有整数相关的频率的一对输入时钟的操作的时序图。44.图9a是示出在本公开的一个实施方案中,当在输入时钟中的任一者中存在抖动时,用于检测抖动的tdc的操作的时序图。45.图9b是示出在本公开的一个实施方案中,在任一输入时钟中存在抖动的情况下tdc的操作的时序图。46.图10是示出在本公开的一个实施方案中相位差样本累加的方式的时序图。47.图11是在本公开的一个实施方案中的信号处理系统的框图,其中可以并入根据本公开的若干方面实现的设备。48.在附图中,相似的参考标号通常表示相同、功能相似和/或结构相似的元件。元件在其中首次出现的附图由对应参考标号中最左边的数字表示。具体实施方式49.1.概述根据本公开的一个方面提供的时间数字转换器(tdc)识别作为输入接收的两个周期信号中的任一者中是否存在抖动。在一个实施方案中,通过分别检查作为输入信号接收的第一周期信号和第二周期信号的第一计数序列和第二计数序列来检测抖动,其中该第一计数序列表示在时间尺度上出现具有该第一周期信号的第一方向的第一边沿序列的相应时刻,该第二计数序列表示在该时间尺度上出现具有该第二周期信号的该第一方向的第二边沿序列的相应时刻。50.根据本公开的另一方面,tdc在不存在抖动的情况下根据第一方法并且在存在抖动的情况下根据第二方法来生成相位差。在一个实施方案中,第一方法需要通过在单独的累加器中合计正时间差和负时间差来计算相位差,而第二方法通过将正时间差和负时间差两者合计到单个累加器中来计算相位差。因此,当识别出存在抖动时,tdc有利地生成相位差,而不考虑由抖动引入的噪声中的至少一些噪声。51.根据本公开的另一方面,当两个周期信号具有相同频率时或者当这两个周期信号中的一者具有另一周期信号的频率的整数倍频率时,tdc也能够操作。52.在一个实施方案中,处理第一计数序列和第二计数序列的tdc的核心逻辑可以包含输入分析器和输出发生器。该输入分析器模块根据第一计数序列生成窗口边界序列。该输出发生器生成指示这两个周期信号中较慢的一者的每个时钟周期的对应相位差的值。53.在一个实施方案中,该输出发生器包括:减法单元,该减法单元用于生成时间差序列;正最小值发生器,该正最小值发生器用于选择表示包含在时间差序列中的正值中的最小值的正最小值;负最大值发生器,该负最大值发生器用于选择表示包含在时间差序列中的负值中的最大值的负最大值;第一累加器,该第一累加器用于接收覆盖对应窗口的正最小值的序列,并且将该正最小值的序列中的值相加以生成第一累加值;第二累加器,该第二累加器用于接收覆盖对应窗口的负最小值的序列,并且将该负最小值的序列中的值相加以生成第二累加值,以及抖动检测器模块,该抖动检测器模块用于接收第一累加值和第二累加值,并且生成指示是否存在抖动的抖动存在信号,其中如果第一累加器和第二累加器都已超过相应阈值,则该抖动检测器模块确定存在抖动。54.tdc还可以包括累加器输出模块,该累加器输出模块用于接收第一累加值和第二累加值,并且当确定不存在抖动时,生成第一累加值和第二累加值的最小量值作为直至对应窗口的累加相位差。55.当确定存在抖动时,将两个累加器中的一者重置为边界值(例如,0),并且此后,重置的累加器累加每个窗口中具有较低量值的正最小值和负最大值中的一者,其中该累加器输出模块将重置的累加器中的累加值转发为累加相位差。56.下文参考用于例示的示例来描述本公开的若干方面。然而,相关领域的技术人员将认识到,可以在没有一个或多个具体细节的情况下或者使用其他方法、部件、材料等来实践本公开。在其他情况下,未详细示出众所周知的结构、材料或操作以避免模糊本公开的特征。此外,所描述的特征/方面可以各种组合来实践,但为了简明起见,本文中仅描述了其中一些组合。57.2.示例性设备图1是在一个实施方案中根据本公开的若干方面实现的时间数字转换器(tdc)的框图。tdc 100被示为包含计数逻辑105和核心逻辑110。tdc 100被示为经连接以接收输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)以及测量时钟clk-meas(103)。输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)表示要针对其使用tdc 100测量(确定)相位差的周期性输入。“相位差”是指两个周期信号之间的相位角的差。信号名称标号后括号内的标号代表图中对应的路径编号,后续描述中,也按此规则进行。58.根据本公开的一个方面提供的路径115提供了表示在对应时刻的(累加)相位差的值。59.计数逻辑105内部包含用于输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)中的每一者的计数器。计数逻辑105经连接以接收输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)。测量时钟clk-meas(103)表示应用于计数逻辑105中的计数器的测量时钟。在一个实施方案中,这些计数器中的每个计数器被设计为在测量时钟clk-meas(103)的每个周期(例如,在每个上升沿)递增一个计数。然而,在另选实施方案中,可以采用其他计数惯例,诸如对于测量时钟clk-meas(103)的每个时钟周期将计数器递减1或某个其他固定值,这对于本领域技术人员将是显而易见的。测量时钟clk-meas(103)的频率至少部分地或基本上确定了分辨率,利用该分辨率可以生成两个事件(诸如输入时钟的上升沿)之间的时间差。60.计数逻辑105被示为分别针对输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)生成信号count-1(104-1)和信号count-2(104-2)。信号count-1(104-1)和信号count-2(104-2)中的每个计数序列表示在相同时间尺度上出现对应输入时钟的预先指定方向(上升或下降)边沿的相应时刻。术语“相同时间尺度”意味着每个计数表示从共同开始时间的相应相对持续时间。例如,每个输入时钟的计数器在同一时间(例如,在重置后)并且以相同频率开始计数(例如,从零开始)。计数逻辑105能够以已知的方式实现。在本公开的一个实施方案中,由计数逻辑105中的计数器生成的计数为36位宽,并且这些计数器的时间分辨率是62.5皮秒(ps)。61.在一个实施方案中,计数逻辑105如与2022年5月10日提交的名称为“counter design for a time-to-digital converter (tdc)”(“时间数字转换器(tdc)的计数器设计”)的美国申请中所述的来实现,并且被转让给本技术的受让人,其内容通过引用整体并入本文。62.核心逻辑110经连接以接收信号count-1(104-1)和信号count-2(104-2),并且在路径115上生成输出数字值,如上文简要描述。63.当了解周期性输入可能表现出抖动的方式时,可以更好地理解本公开的若干特征。因此,接下来参考图2简要描述输入时钟表现出抖动的方式。64.3.具有抖动的周期性输入图2是示出在一个实施方案中在稳定状态下具有相同频率和相同相位的一对周期性输入中的一者具有抖动的方式的时序图。在图2中,抖动的波形未按比例绘制,并且仅提供用于示出抖动。在图2中,路径101-1和路径102-1上的两个波形分别表示要针对其测量相位差的输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)的波形。65.输入时钟clk-in-1(101-1)的上升沿被示为出现在时刻t11、t12、t14和t18,而输入时钟clk-in-2(101-2)的上升沿被示为出现在时刻t10、t13、t15和t16。在稳定状态下,在输入时钟中不存在抖动时,输入时钟clk-in-2(101-2)的每个上升沿将与输入时钟clk-in-1(101-1)的相应上升沿重合,即,输入时钟clk-in-2(101-2)的上升沿也将出现在时刻t11、t12、t14和t18。66.然而,如图2所示,输入时钟clk-in-2(101-2)的上升沿被示为要么稍微早于输入时钟clk-in-1(101-1)的对应上升沿出现,诸如在一些周期内的时刻t10和t16,要么稍微晚于输入时钟clk-in-1(101-2)的对应上升沿出现,诸如在一些周期内的时刻t13和t15。67.因此,输入时钟clk-in-2(101-2)被称为具有“抖动”。通常,抖动表现出随机特性,因此当叠加在另外的理想时钟信号上时,抖动表现为负时间差和正时间差。本公开的各方面利用这种观察来识别抖动。68.本公开的另外的方面寻求通过在识别出存在抖动时在相位差的计算中忽视正或负符号的时间差来减少对测量的相位差的不期望的影响。69.为了便于理解,图2的时序图描绘了抖动的简单化图示。然而,实际上,抖动将更随机,并且输入时钟内可能存在具有抖动的若干周期。此外,如对本领域技术人员显而易见的,抖动可以是若干类型,诸如随机抖动、确定性抖动等。本公开的各方面也适用于这种类型的抖动。70.尽管图2的时序图示出了具有相同频率的一对周期性输入(输入时钟)中的抖动,但是本公开的各方面也适用于频率为大于1的整数相关倍数的一对输入时钟。71.根据本公开的各方面实现的tdc 100除了在存在和不存在抖动时提供相位差之外,还检测这些输入时钟中的一个输入时钟中抖动的存在,如以下示例所述。72.4.流程图图3a是示出根据本公开的一方面的tdc利用具有抖动的输入时钟信号操作的方式的流程图。仅为了例示而相对于图1的核心逻辑110描述该流程图。然而,许多特征可以在其他系统和/或其他环境中实现,而不脱离本公开的若干方面的范围和精神,如相关领域的技术人员通过阅读本文提供的公开内容将显而易见的。73.另外,一些步骤可以按照与下文描绘的不同顺序执行,以适合于特定环境,这对于相关领域的技术人员将是显而易见的。许多这样的具体实施被预期为由本公开的若干方面覆盖。流程图开始于步骤301,其中控制立即转到步骤303。74.在步骤303中,核心逻辑110分别接收第一周期信号和第二周期信号的第一计数序列和第二计数序列。在步骤304中,核心逻辑110生成这两个周期信号的(相同方向的)边沿之间的时间差,其中用符号和量值表示每个时间差。75.在步骤306中,核心逻辑110检查在这两个周期信号中的一者中是否存在抖动。如果不存在抖动,则控制转到步骤307,如果存在抖动,则转到步骤311。步骤307和步骤311根据不同的方法计算相位差,具体在于抵消抖动对精确相位差测量的影响。76.可以选择任何合适的方法来最小化在检测到抖动时抖动对相位差测量的影响。在下文描述的实施方案中,第一方法需要通过在单独的累加器中合计正时间差和负时间差来计算相位差,而第二方法通过将正时间差和负时间差两者合计到单个累加器中来计算相位差。77.然后控制转到步骤315,其中将计算的相位差提供给需要这种信息的任何外部部件。流程图在步骤320结束。78.因此,本公开的tdc提供了相当准确的相位差,即使在这些时钟信号中的一者中存在抖动时也是如此。接下来简要提供本公开的一个实施方案中这种tdc中所包含的核心逻辑的具体实施细节。79.5.核心逻辑图3b是示出本公开的一个实施方案中核心逻辑110的具体实施细节的框图。核心逻辑110被示为包含输入分析器模块350和输出发生器模块390。80.输入分析器模块350被示为在路径104-1上接收输入的信号count-1、在路径104-2上接收信号count-2、在路径307上接收信号clk-dig-tdc,并且在路径395上接收信号jitter-indicator。输入分析器模块350在路径332上生成信号window-identifier,在路径342-1上生成信号count1-sub,并且在路径342-2上生成信号count2-sub。输入分析器模块350在对应的输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)的每个上升沿接收信号count-1(104-1)和信号count-2(104-2)。输入分析器模块350可以存储信号count-1(104-1)和信号count-2(104-2)值,并且另外执行操作诸如处理生成信号count-1(104-1)和信号count-2(104-2)的计数器的翻转。在不存在这种附加操作的情况下,信号count1-sub(342-1)和信号count2-sub(342-2)分别在功能上等效于信号count-1(104-1)和信号count-2(104-2)。81.输入分析器模块350,除了其他操作之外,还进行操作以确定窗口的边界(相应时刻),当两个时钟具有相同频率时,该边界对应于两个输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)中的任一者的一对连续边沿(或由其定义),并且当时钟具有大于1的整数倍频率时,该边界对应于较慢时钟的一对连续边沿。如将在下文详细描述的,输入分析器350使用信号window-identifier(332)来指示窗口的边界(左边沿和右边沿)。82.尽管描述继续相对于输入时钟的上升沿,但本公开的各方面同样适用于输入时钟的下降沿,如本领域技术人员通过阅读本文公开的内容将显而易见的。83.输出发生器模块390被示为在路径332上接收信号window-identifier、在路径342-1上接收信号count1-sub、在路径342-2上接收信号count2-sub、在路径307上接收信号clk-dig-tdc,并且在路径395上生成信号jitter-indicator。在一个实施方案中,输出发生器模块390在路径115上生成窗口序列中的每个窗口中的值序列中的一个值,其中该值指示该窗口的对应计算的相位差。如将在下文详细描述的可以基于tdc 100的操作模式在对应路径上提供附加输出。84.尽管上述tdc 100被示为仅对一对周期性输入进行操作,但是tdc 100可以被实现为通过对tdc 100进行适当修改而同时对多于一对周期性输入进行操作。利用多于一对周期性输入的tdc的操作在与2022年5月10日提交的名称为“time-to-digital converter (tdc) measuring phase difference between periodic inputs”(“用于测量多个时钟之间相位差的时间-数字转换器(tdc)体系结构”)的美国申请中详细地描述,并且被转让给本技术的受让人,其内容通过引用整体并入本文。85.接下来详细描述在确定一对输入时钟之间的相位差时由核心逻辑110的输入分析器模块350和输出发生器模块390执行的操作的细节。86.6.输入分析器模块图4a是示出本公开的一个实施方案中输入分析器模块的具体实施细节的框图。输入分析器模块350被示为包含第一计数(count 1-q)发生器405-1、第二计数(count2-q)发生器405-2、第一唯一发生器 410-1、第二唯一发生器 410-2、第一翻转发生器415-1、第二翻转发生器415-2、窗口标识模块420和翻转模块425。图4a的具体模块和互连仅作为示例示出。在本公开的其他实施方案中可以使用更多或更少的模块。在本公开的实施方案中,使用时序逻辑来实现模块405-1、405-2、410-1、410-2、415-1和415-2,而使用组合逻辑来实现窗口标识模块420和翻转模块425。然而,这些模块可以不同方式实现,如本领域技术人员通过阅读本文公开的内容将显而易见的。输入分析器模块350的顺序模块由信号clk-dig-tdc(307)计时。87.如上所述,信号clk-dig-tdc(307)的频率大于输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)的频率,并且在相应时钟的每个上升沿接收到信号count-1(104-1)和信号count-2(104-2)的值。因此,信号count-1(104-1)和信号count-2(104-2)的值可以在信号clk-dig-tdc(307)的两个或更多个周期内保持不变。因此,可以检查信号count-1(104-1)和信号count-2(104-2)的相应值的变化,以确定输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)之间的相位差。第一计数发生器405-1、第二计数发生器405-2、第一唯一发生器 410-1、第二唯一发生器 410-2和窗口标识模块420进行操作以提供这种功能。88.第一计数发生器405-1在路径104-1上接收信号count-1,并且在路径406-1上生成信号count1-q。在一个实施方案中,第一计数发生器405-1被实现为正边沿触发的触发器。第一计数发生器405-1由信号clk-dig-tdc(307)计时。信号count1-q(406-1)表示信号count-1(104-1)的时间延迟版本。因此,信号count-1(104-1)在被输出到路径406-1上之前被延迟了信号clk-dig-tdc(307)的一个时钟周期。89.第二计数发生器405-2在路径104-2上接收信号count-2,并且在路径406-2上生成信号count2-q。在一个实施方案中,第二计数发生器405-2被实现为正边沿触发的触发器。第二计数发生器405-2由信号clk-dig-tdc(307)计时。信号count2-q(406-2)表示信号count-2(104-2)的时间延迟版本。因此,信号count-2(104-2)在被输出到路径406-2上之前被延迟了信号clk-dig-tdc(307)的一个时钟周期。90.第一唯一发生器 410-1接收信号count-1(104-1)、信号count1-q(406-1)和信号window-identifier(332),并且在路径411-1上生成信号unique-count1-q。如从图4a中可观察到,第一唯一发生器410-1和窗口标识模块420(下文描述)的操作依赖于彼此的输出。通常,第一唯一发生器 410-1的输出是二进制信号,其指示在由窗口标识模块420标识的窗口的边界处是否有新的计数可用。在本公开的一个实施方案中,第一唯一发生器410-1被实现为顺序模块,由信号clk-dig-tdc(307)计时,并且实现以下逻辑:当信号count-1(104-1)等于信号count1-q(406-1),并且信号window-identifier(332)为逻辑高电平时,第一唯一发生器 410-1在路径411-1上生成逻辑低电平,并且当信号count-1(104-1)不等于信号count1-q(406-1)时生成逻辑高电平。换句话说,第一唯一发生器 410-1进行操作以确定信号count-1(104-1)的计数值已经历与其在信号clk-dig-tdc(307)的先前时钟周期中的值相比的变化(指示输入时钟clk-in-1(101-1)的上升沿的出现),并且还额外考虑了信号window-identifier(332)的值。91.第二唯一发生器 410-2接收信号count-2(104-2)、信号count2-q(406-2)和信号window-identifier(332),并且在路径411-2上生成信号unique-count2-q。如从图4a中可观察到,第二唯一发生器 410-2和窗口标识模块420(下文描述)的操作依赖于彼此的输出。通常,第二唯一发生器410-2输出的是二进制信号,其指示在由窗口标识模块420标识的窗口的边界处是否有新的计数可用。在本公开的一个实施方案中,第二唯一发生器 410-2被实现为顺序模块,由信号clk-dig-tdc(307)计时,并且实现以下逻辑:当信号count-2(104-2)等于信号count2-q(406-2),并且信号window-identifier(332)为逻辑高电平时,第二唯一发生器410-2在路径411-2上生成逻辑低电平,并且当信号count-2(104-2)不等于信号count2-q(406-2)时生成逻辑高电平。换句话说,第二唯一发生器410-2进行操作以确定信号count-2(104-2)的计数值已经历与其在信号clk-dig-tdc(307)的先前时钟周期中的值相比的变化(指示输入时钟clk-in-2(101-2)的上升沿的出现),并且额外考虑了信号window-identifier(332)的值。92.核心逻辑110接收表示输入时钟clk-in-1(101-1)和clk-in-2(101-2)的对应边沿的连续计数流。核心逻辑110从一个输入时钟(例如,输入时钟clk-in-1(101-1))的(相同方向的,上升/下降)一对连续边沿和另一输入时钟(例如,输入时钟clk-in-2(101-2))的单个边沿生成输出序列中的每个输出(如上所述)。因此,核心逻辑110需要识别相应对连续边沿以用于生成每个输出。在输入分析器模块350中实现的窗口标识模块420执行这样的操作。93.窗口标识模块420进行操作以识别上述窗口边界。也就是说,当两个输入时钟的频率为大于1的整数倍时,窗口标识模块420进行操作以识别较慢输入时钟的相同方向(上升或下降)的一对连续边沿的出现时刻,或者当两个输入时钟的频率相等时,进行操作以识别两个输入时钟中任一者的相同方向(上升或下降)的一对连续边沿的出现时刻。这些时刻之间的持续时间在本文被称为窗口。每个窗口可具有相应差异流,需要对这些差异流进行检查以便在每个窗口结束后生成输出(表示输入时钟clk-in-1(101-1)与输入时钟clk-in-2(101-2)之间的相位差)。94.窗口标识模块420接收信号unique-count1-q(411-1)和信号unique-count2-q(411-2),并且在路径332上生成信号window-identifier。当信号unique-count1-q(411-1)和信号unique-count2-q(411-2)都为逻辑高电平时,窗口标识模块420在路径332上生成逻辑高电平,否则生成逻辑低电平。如在下文的描述中将显而易见的,一对连续逻辑高电平表示如上所述的窗口边界。95.第一翻转发生器415-1接收信号count-1(104-1)、信号count1-q(406-1)、信号window-identifier(332),并且在路径416-1上生成信号rollover-1。在本公开的实施方案中,第一翻转发生器415-1被实现为顺序模块,由信号clk-dig-tdc(307)计时。当信号count-1(104-1)的计数值已超过计数器的满刻度值(翻转)时,第一翻转发生器415-1在路径416-1上生成逻辑高电平。如在相关领域中众所周知的,当计数器的值达到其满刻度值时,就说发生了翻转,并且计数器从零开始计数。例如,对于10位计数器,当计数的值达到1024时,就说发生了翻转。96.第二翻转发生器415-2接收信号count-2(104-2)、信号count2-q(406-2)、信号window-identifier(332),并且在路径416-2上生成信号rollover-2。在本公开的实施方案中,第二翻转发生器415-2被实现为顺序模块,由信号clk-dig-tdc(307)计时。当信号count-2(104-2)的计数值已超过计数器的满刻度值(翻转)时,第二翻转发生器415-2在路径416-2上生成逻辑高电平。97.翻转模块425接收信号count-1(104-1)、信号count-2(104-2)、信号rollover-1(416-1)和信号rollover-2(416-2),并且生成信号count1-sub(342-1)和信号count2-sub(342-2)。在本公开的实施方案中,翻转模块425被实现为组合模块。翻转模块425进行操作以确保在任一输入计数翻转的情况下,输入计数的相应正确值被转发到输出发生器模块390。98.在一个实施方案中,翻转处理如与2022年5月10日提交的名称为“time-to-digital converter (tdc) measuring phase difference between periodic inputs”(“用于测量周期输入之间的相位差的时间数字转换器(tdc)”)的美国申请中的详细描述来实现,并且被转让给本技术的受让人,其内容通过引用整体并入本文。99.接下来提供本公开的一个实施方案中输出发生器模块390的具体实施细节。100.7.输出发生器模块图4b是示出本公开的一个实施方案中输出发生器模块的具体实施细节的框图。输出发生器模块390被示为包含减法单元430、正最小值发生器435、负最大值发生器445、窗口计数器444、正累加器440、负累加器450、抖动检测器460、运行累加器数据发生器(running-accumulator-data generator)465和累加器有效数据发生器(accumulator valid-data generator)475。101.图4b的具体模块和互连仅作为示例示出。在本公开的其他实施方案中可以使用更多或更少的模块。在本公开的一个实施方案中,模块435、445、444、440、450和475被示为顺序的,而模块430和465被示为组合的。其他输出信号,即信号running-acc-data(491)、信号running-nsample(492)和信号data-valid(493)由运行累加器数据发生器(running-accumulator-data generator)465和累加器有效数据发生器(accumulator valid-data generator)475生成,它们另外在核心逻辑110中实现,以启用模式(1)和模式(2)中的操作,如下文所述。102.在一个实施方案中,tdc 100被设计成在以下模式中进行操作:模式(1):累加器模式,其中输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)具有相同频率。103.模式(2):累加器模式,其中输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)的频率整数相关。104.模式(3):连续单发模式。105.模式(4):一次性单发模式。106.在模式(1)和(2)中,tdc 100(经由未示出的对应装置从用户)接收指示要累加的相位差样本的数量的预先确定值。在这两种模式中,tdc 100在路径115(信号output)、路径493(信号data-valid)、路径491(信号running-acc-data)和路径492(信号running-nsample)上生成输出。在对每个预先确定数量的样本进行采样(以下称为累加周期)结束时,tdc 100断言信号data-valid(493)并且在路径115(信号output)上提供累加相位差值。在累加每个相位差样本结束时,tdc 100在路径491(信号running-acc-data)上提供迄今累加的相位差值。信号running-nsample(492)指示在信号running-acc-data(491)中累加的样本的数量。累加值的平均值(总累加值除以累加样本的数量)可以由tdc 100外部的部件确定。107.在模式(3)中,tdc 100生成该对周期性输入之间的相位差(如在模式(1)和模式(2)中没有相位差样本的累加),并且在附加路径(未示出)上提供相位差序列。108.在模式(4)中,tdc 100对脉冲输入进行操作,生成脉冲之间的一次性相位差,并且在附加路径(未示出)上提供相位差。109.输出发生器模块390接收信号window-identifier(332)、信号count1-sub(342-1)和信号count2-sub(342-2)。在一个实施方案中,信号window-identifier(332)、信号count1-sub(342-1)和信号count2-sub(342-2)在一个采样深度的流水线级(未示出)中被缓冲,以使得核心逻辑110能够满足电路时序要求。在一个实施方案中,流水线延迟级使用寄存器来实现,并且信号被延迟/缓冲信号clk-dig-tdc(307)的一个时钟周期。110.输出发生器模块390在路径395上生成信号jitter-indicator。信号jitter-indicator(395)用于指示输入时钟中的任一者中的抖动,如下文将详细描述的。尽管路径395被表示为单个路径,但是在路径395上提供信号jitter-present(392)和信号use-jitter-approach(393)。111.减法单元430在路径342-1上接收信号count1-sub,在路径342-2上接收信号count2-sub。减法单元430在路径433上生成信号running-count-diff。在本公开的实施方案中,减法单元430被实现为有符号减法模块。因此,减法单元430生成信号count1-sub(342-1)与信号count2-sub(342-2)之间的有符号差。信号running-count-diff(433)表示窗口内输入时钟clk-in-1(101-1)与输入时钟clk-in-2(101-2)的边沿或边沿对之间的时间差流。112.正最小值发生器435进行操作以确定在由窗口标识模块420标识的每个窗口中(即,在两个输入时钟中的较慢时钟的一对连续正(上升)沿之间)减法单元430生成的一组差值(信号running-count-diff(433))之中/之间的正最小值。正最小值发生器435在路径433上接收信号running-count-diff,在路径332上接收信号window-identifier,并且在路径436上生成信号pos-min。在本公开的一个实施方案中,正最小值发生器435被实现为顺序模块,由信号clk-dig-tdc(307)计时,并且根据以下逻辑操作:如果信号window-identifier(332)为逻辑高电平并且信号running-count-diff(433)为零或正值,则将信号pos-min(436)记录为信号running-count-diff(433)。否则,如果信号window-identifier(332)为逻辑高电平并且信号running-count-diff(433)为非零并且为负值,则将信号pos-min(436)记录为满刻度正值。换句话说,如果信号count-1(104-1)和信号count-2(104-2)每一者由p个位组成,则满刻度正值为+(2p-1),在下文中称为“max1”。否则,如果信号running-count-diff(433)是正值并且小于信号pos-min(436),则信号pos-min(436)被更新为信号running-count-diff(433)。因此,正最小值发生器435进行操作以确定两个连续信号window-identifier(332)脉冲之间的信号running-count-diff(433)的正最小值。113.负最大值发生器445进行操作以确定在由窗口标识模块420标识的每个窗口中(即,在两个输入时钟中的较慢时钟的一对连续正(上升)沿之间)减法单元430生成的一组差值(信号running-count-diff(433))之中/之间的最大负值。负最大值发生器445在路径433上接收信号running-count-diff,在路径332上接收信号window-identifier,并且在路径446上生成信号neg-max。在本公开的一个实施方案中,负最大值发生器445被实现为顺序模块,由信号clk-dig-tdc(307)计时,并且根据以下逻辑操作:如果信号window-identifier(332)为逻辑高电平并且信号running-count-diff(433)为零或负值,则将信号neg-max(446)记录为信号running-count-diff(433)。否则,如果信号window-identifier(332)为逻辑高电平并且信号running-count-diff(433)为非零并且为正值,则将信号neg-max(446)记录为满刻度负值。换句话说,如果信号count-1(104-1)和信号count-2(104-2)每一者由p个位组成,则满刻度负值为-(2p-1),在下文中称为“max2”。否则,如果信号running-count-diff(433)为负值并且大于信号neg-max(446),则信号neg-max(446)被更新为信号running-count-diff(433)。因此,负最大值发生器445进行操作以确定两个信号window-identifier(332)脉冲之间的信号running-count-diff(433)的最大负值。114.窗口计数器444接收信号pos-min(436)、信号neg-max(446)和信号jitter-indicator(395),并且在路径447上生成信号nsample-done。在一个实施方案中,窗口计数器444在每个窗口结束时递增计数器的值,并且当计数器值等于作为用户输入提供的相位差样本的预先确定数量时断言信号nsample-done(447)。当信号jitter-present(392)的接收值为逻辑高电平时,窗口计数器444断言路径447上的信号nsample-done(结束当前累加周期)并且将计数器的值重置为零(指示新累加周期的开始)。115.正累加器440在路径436上接收信号pos-min,在路径446上接收信号neg-max,在路径332上接收信号window-identifier,在路径447上接收信号nsample-done,在路径395上接收信号jitter-indicator,并且在路径442上生成信号acc-pos-q。在一个实施方案中,如将在下文详细描述的,上述“max1”的值是正累加器440的阈值,其形成指示抖动存在的基础。116.在一个实施方案中,当在路径392上接收的值(信号jitter-present)为逻辑高电平(指示输入时钟中的任一者中存在抖动)时,正累加器440将累加值,即信号acc-pos-q(442)重置为边界值(例如,零)。117.在一个实施方案中,当在路径393上接收的值(信号use-jitter-approach)为逻辑低电平(指示在输入时钟中不存在抖动)时,正累加器440累加(相加)接收的信号pos-min(436)。换句话说,当信号use-jitter-approach(393)为逻辑低电平时,正累加器440忽略接收的信号neg-max(446)。118.当在路径393上接收的值(信号use-jitter-approach)为逻辑高电平(指示输入时钟中存在抖动)时,正累加器440使用以下方法操作:正累加器440计算在每个窗口中接收的信号pos-min(436)和信号neg-max(446)的较低量值(绝对最小值),并且将计算的值(具有对应符号)累加(相加)到正累加器440的当前值。例如,在窗口中,如果信号pos-min(436)的值被接收为“+1”并且信号neg-max(446)的值被接收为“‑2”,则正累加器440将“+1”加到正累加器440中的当前值。再如,在窗口中,如果信号pos-min(436)的值被接收为“+3”并且信号neg-max(446)的值被接收为“‑2”,则正累加器440将较低量值计算为“‑2”,并且将“‑2”(具有符号)加到正累加器440中的当前值。119.负累加器450在路径446上接收信号neg-max,在路径332上接收信号window-identifier,在路径447上接收信号nsample-done,在路径395上接收信号jitter-indicator,并且在路径452上生成信号acc-neg-q。在一个实施方案中,如将在下文详细描述的,上述“max2”的值是负累加器450的阈值,其形成指示抖动存在的基础。120.在一个实施方案中,当在路径392上接收的值(信号jitter-present)为逻辑高电平(指示输入时钟中的任一者中存在抖动)时,正累加器440将累加值信号acc-pos-q(442)重置为边界值(例如,零)。121.在一个实施方案中,当在路径393上接收的值(信号use-jitter-approach)为逻辑低电平(指示在输入时钟中不存在抖动)时,负累加器450累加(相加)接收的信号neg-max(446)。当在路径393上接收的值(信号use-jitter-approach)为逻辑高电平(指示输入时钟中的任一者中存在抖动)时,负累加器450不累加任何值。122.运行累加器数据发生器465和累加器有效数据发生器475检查信号acc-pos-q(442)和信号acc-neg-q(452),以确定上述模式(1)和(2)中的输出(信号running-acc-data(491)和信号output(115))。模块440、450、465和475一起包括可进行操作以在tdc 100的累加操作模式中生成对应输出的累加逻辑。123.运行累加器数据发生器465接收信号acc-pos-q(442)、信号acc-neg-q(452)、信号jitter-indicator(395),并且在路径491上生成信号running-acc-data,在路径492上生成信号running-nsample。124.在一个实施方案中,当在路径393上接收的值(信号use-jitter-approach)为逻辑低电平(指示输入时钟中不存在抖动)时,运行累加器数据发生器465确定信号acc-pos-q(442)和信号acc-neg-q(452)的较低量值(绝对最小值),并在路径491上提供该较低量值。当在路径393上接收的值(信号use-jitter-approach)为逻辑高电平(指示输入时钟中存在抖动)时,运行累加器数据发生器465转发在路径442上接收的值(信号acc-pos-q)并且忽略信号acc-neg-q(452)。信号running-nsample(492)指示在信号running-acc-data(491)中累加的样本的数量。125.累加器有效数据发生器475接收信号acc-pos-q(442)、信号acc-neg-q(452)、信号nsample-done(447)和信号jitter-indicator(395),并且在路径493上生成信号data-valid,在路径115上生成信号output。在累加每预先确定数量的样本结束时(由信号nsample-done(447)指示),累加器有效数据发生器475断言信号data-valid(493),并且在路径115上提供累加相位差。126.在一个实施方案中,当在路径392上接收的值(信号jitter-present)为逻辑高电平时,累加器有效数据发生器475将当前累加值重置为边界值(例如,零)。当在路径393上接收的值(信号use-jitter-approach)为逻辑低电平(指示输入时钟中不存在抖动)时,累加器有效数据发生器475确定在累加周期结束时接收的信号acc-pos-q(442)和信号acc-neg-q(452)的较低量值(绝对最小值),并且在路径115上提供相同的值,直到下一累加周期结束为止。当在路径393上接收的值(信号use-jitter-approach)为逻辑高电平(指示输入时钟中存在抖动)时,累加器有效数据发生器475在累加周期结束时转发在路径442上接收的值(信号acc-pos-q),并且在路径115上提供该值作为累加相位差,直到下一累加周期结束为止。换句话说,当在路径393上接收的值(信号use-jitter-approach)为逻辑高电平(指示输入时钟中存在抖动)时,累加器有效数据发生器475忽略信号acc-neg-q(452)。127.抖动检测器460接收信号acc-pos-q(442)和信号acc-neg-q(452),并且在路径395上生成信号jitter-indicator。如上所述,信号jitter-indicator(395)用于指示在输入时钟中的任一者中存在抖动。128.如上所述,抖动检测器460在路径395上生成信号jitter-present(392)和信号use-jitter-approach(393)。在一个实施方案中,路径392(信号jitter-present)上的逻辑低电平指示输入时钟中不存在抖动,而路径392(信号jitter-present)上的逻辑高电平指示在输入时钟中的任一者中存在抖动。信号jitter-present(392)默认设置为逻辑低电平。抖动检测器460检查信号acc-pos-q(442)和信号acc-neg-q(452)两者的值是否已超过相应阈值(分别为“max1”和“max2”)。如果是,则抖动检测器460在路径392上生成逻辑高电平,指示在输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)中的任一者中存在抖动。在示例性实施方案中,在信号clk-dig-tdc(307)的一个时钟周期之后,将jitter-present(392)信号解除断言。因此,信号jitter-present(392)的脉冲宽度等于信号clk-dig-tdc(307)的一个时钟周期。129.在一个实施方案中,信号use-jitter-approach(393)默认为逻辑低电平。当确定存在抖动时,抖动检测器460在路径393上生成逻辑高电平。抖动检测器460将信号use-jitter-approach(393)保持在断言状态(逻辑高电平)中,持续时间等于由用户提供的用于相位差样本的累加的预先确定数量的窗口。抖动检测器460基于在路径447(未示出)上接收的信号nsample-done来确定预先确定数量的窗口的结束。130.尽管在例示性实施方案中,抖动的检测被示为由在模块运行累加器数据发生器465和累加器有效数据发生器475外部实现的抖动检测器460来执行,但是在另选实施方案中,抖动检测器460可以被实现为模块运行累加器数据发生器465或累加器有效数据发生器475中的任一者的一部分。131.接下来提供本公开的一个实施方案中第一唯一发生器和第二唯一发生器的具体实施细节。132.8.唯一计数(unique-count)发生器图5是示出本公开的一个实施方案中唯一计数发生器的具体实施细节的框图。图5被示为包含触发器502-1、第一计数发生器405-1、第一唯一发生器 410-1、触发器502-2、第二计数发生器405-2、第二唯一发生器410-2和窗口标识模块420。第一唯一发生器410-1又被示为包含逻辑模块505-1、多路复用器(mux)507-1、509-1、511-1、513-1、触发器515-1、反相器520-1和与门518-1。第二唯一发生器410-2又被示为包含逻辑模块505-2、多路复用器507-2、509-2、511-2、513-2、触发器515-2、反相器520-2和与门518-2。图5中的具体模块和互连仅作为示例示出。在本公开的其他实施方案中可以使用更多或更少的模块。133.逻辑模块505-1接收信号count-1(104-1)和信号count1-q(406-1),并且生成信号unique-count1(501-1)。在一个实施方案中,如果信号count-1(104-1)和信号count1-q(406-1)不相等,则逻辑模块505-1在路径501-1上生成逻辑高电平,否则生成逻辑低电平。因此,逻辑模块505-1实现了逻辑:unique-count1=(count-1!=count1-q)。134.mux 507-1在路径503-1上接收逻辑高电平和信号unique-count1-q(411-1),并且基于选择信号(信号unique-count1(501-1))的逻辑值,在路径508-1上转发逻辑高电平和信号unique-count1-q(411-1)中的一者作为输出(mux选择输出)。因此,当信号unique-count1(501-1)为逻辑高电平时,mux 507-1在路径508-1上转发逻辑高电平(503-1)。当信号unique-count1(501-1)为逻辑低电平时,mux 507-1在路径508-1上转发信号unique-count1-q(411-1)。135.mux 509-1在路径504-1上接收逻辑低电平,在路径508-1上接收mux 507-1的输出,并且基于选择信号(路径519-1上的信号)的逻辑值,在路径510-1上转发逻辑低电平(信号504-1上的信号)和mux输出(路径508-1上信号)中的一者作为输出(mux选择输出)。因此,当路径519-1上的值为逻辑高电平时,mux 509-1在路径510-1上转发逻辑低电平(路径504-1上的信号)。当路径519-1上的值为逻辑低电平时,mux 509-1在路径510-1上转发路径508-1上的值。136.mux 511-1在路径506-1上接收逻辑低电平,在路径510-1上接收mux 509-1的输出,并且基于选择信号(即信号jitter-present(392))的逻辑值,在路径512-1上转发逻辑低电平和mux输出的路径510-1上信号中的一者作为输出(mux选择输出)。137.信号jitter-present(392)是从输出发生器模块390(如上相对于图4b所述)接收的,并且指示输入时钟(clk-in-1(101-1)和clk-in-2(101-2))中的任一者中是否存在抖动。因此,当信号jitter-present(392)为逻辑高电平(指示存在抖动)时,mux 511-1在路径512-1上转发逻辑低电平(路径506-1上信号)。当信号jitter-present(392)为逻辑低电平时,mux 511-1在路径512-1上转发路径510-1上的值。因此,当信号jitter-present(392)为逻辑高电平时,信号unique-count-1-q(411-1)被设置为逻辑低电平(重置)。138.mux 513-1在路径516-1上接收逻辑低电平,在路径512-1上接收mux 511-1的输出,并且基于选择信号rstn-i(519)的逻辑值,在路径514-1上转发逻辑低电平和mux输出(路径512-1上信号)中的一者作为输出(mux选择输出)。信号rstn-i(519)表示芯片重置或上电重置。因此,当信号rstn-i(519)为逻辑高电平时,mux 513-1在路径514-1上转发逻辑低电平(516-1)。当信号rstn-i(519)为逻辑低电平时,mux 513-1在路径514-1上转发路径512-1上的值。139.触发器515-1由信号clk-dig-tdc(307)计时。触发器515-1在其d输入端接收路径514-1上的输入信号,并且在路径411-1上生成输出(q)、信号unique-count1-q。在一个实施方案中,触发器515-1被实现为正边沿触发的触发器。140.与门518-1在路径521-1上接收反相器520-1的输出,在路径332上接收信号window-identifier,并且在路径519-1上生成与运算的结果。141.窗口标识模块420接收信号unique-count1-q(411-1)和信号unique-count2-q(411-2),并且在路径332上生成信号window-identifier。在本公开的一个实施方案中,窗口标识模块420被实现为与门。因此,窗口标识模块420实现了逻辑:window-identifier=(unique-count1-q && unique-count2-q)。在例示性实施方案中,在信号clk-dig-tdc(307)的一个时钟周期之后,将信号window-identifier(332)解除断言。因此,信号window-identifier(332)的脉冲宽度等于信号clk-dig-tdc(307)的一个时钟周期,并且信号window-identifier(332)的频率等于两个所选输入时钟(clk-in-1(101-1)和clk-in-2(101-2))频率中较慢的一者(在这两个时钟的频率整数相关的情况下)。142.部件505-1、507-1、509-1、511-1和513-1一起实现以下逻辑:if (window-identifier && !unique-count1) unique-count1-q = 0else if (unique-count1) unique-count1-q = 1上面的表达式(window-identifier && !unique-count1)包含运算符&&和!,它们分别表示“与”运算符和“非”运算符。因此,当信号window-identifier的值为逻辑高电平并且信号unique-count1的值为逻辑低电平时,表达式(window-identifier && !unique-count1)将被评估为1,否则为0。143.部件505-2、520-2、518-2、507-2、509-2、511-2、513-2和515-2分别以与部件505-1、520-1、518-1、507-1、509-1、511-1、513-1和515-1类似的方式进行操作,为了简明起见,此处不再重复描述。144.接下来用示例性波形示出唯一计数发生器和窗口标识模块进行操作以确定窗口的方式。145.9.针对具有相同频率的一对输入时钟生成信号unique-count和信号window-identifier图6是示出本公开的一个实施方案中针对具有相同频率(和相位差)的一对输入时钟生成信号unique-count(501, 411)和信号window-identifier(332)的方式的时序图(未按比例绘制)。图6示出了信号clk-dig-tdc(307)、输入时钟clk-in-1(101-1)、信号count-1(104-1)、信号count1-q(406-1)、信号unique-count1(501-1)、信号unique-count1-q(411-1)、输入时钟clk-in-2(101-2)、信号count-2(104-2)、信号count2-q(406-2)、信号unique-count2(501-2)、信号unique-count2-q(411-2)和信号window-identifier(332)的示例性波形。在此例示性实施方案中,对应于输入时钟(clk-in-1(101-1)和clk-in-2(101-2))的计数被假定为36位宽。图6中所示的具体计数值和输入时钟clk-in-1与输入时钟clk-in-2之间的相位差未按比例绘制,仅用于示出生成唯一计数值和信号window-identifier的方式。出于本说明书的目的,数据波形(信号count-1(104-1)、信号count1-q(406-1)、信号count-2(104-2)、count2-q(406-2)、信号running-count-diff(433)、信号pos-min(436)、信号neg-max(446)、信号acc-pos-q(442)、信号acc-neg-q(452))中的“x”值指示“无关”值。146.在t610接收的值“289”(信号count-1(104-1))对应于输入时钟clk-in-1(101-1)的上升沿(re11)的出现时间的数字表示,而在t612接收的值“310”(信号count-2(104-2))对应于输入时钟clk-in-2(101-2)的上升沿(re21)的出现时间的数字表示。由相应输入时钟clk-in-1和输入时钟clk-in-2采样的计数器(在计数逻辑105中,未示出)在输入时钟clk-in-1和输入时钟clk-in-2的相应上升沿提供对应计数值信号count-1(104-1)和信号count-2(104-2)。如上所述,对应于每对输入时钟的计数器被同步,即,从相同的初始值(例如,零)开始计数并以相同速率递增。因此,计数器表示相同时间尺度上的时刻。147.对应于输入时钟clk-in-1(101-1)的上升沿的计数被示为在时刻t610、t618和t626被接收。因此,信号count-1(104-1)被示为具有t610-t618之间的值289、t618-t626之间的值373以及t626-t632之间的值457。信号count1-q(406-1)为信号count-1(104-1)的值,但是被触发器,即第一计数发生器405-1,延迟信号clk-dig-tdc(307)的一个时钟周期。因此,当信号count-1(104-1)具有在t610开始的值289时,信号count1-q(406-1)被示为具有在t612开始的值289(在信号clk-dig-tdc(307)的一个周期之后)。因此,信号count1-q(406-1)被示为具有t612-t620之间的值289、t620-t628之间的值373以及t628-t632之间的值457。148.当信号count-1(104-1)的值不等于信号count1-q(406-1)的值时,断言信号unique-count1(501-1)。换句话说,当输入时钟clk-in-1(101-1)的计数已经历与其在信号clk-dig-tdc(307)的先前时钟周期中的值相比的变化时,信号unique-count1(501-1)被设置为逻辑高电平。因此,当信号count-1(104-1)的值不等于信号count1-q(406-1)的值时,信号unique-count1(501-1)被示为仅在时间间隔t610-t612、t618-t620和t626-t628中被断言。149.如上所述,信号unique-count1-q(411-1)基于以下逻辑来确定:if (window-identifier && !unique-count1) unique-count1-q = 0else if (unique-count1) unique-count1-q = 1(逻辑1.1)基于当前时刻之前一个时钟周期的信号window-identifier(332)和信号unique-count1(501-1)的值来评估上述逻辑。因此,在t612,考虑进行评估的信号window-identifier(332)的值为逻辑低电平(时间间隔t610-t612中的值),并且考虑进行评估的信号unique-count1(501-1)的值为逻辑高电平。因此,第一唯一发生器410-1评估逻辑1.1,并且在t612开始将信号unique-count1-q(411-1)设置为逻辑高电平。150.对应于输入时钟clk-in-2(101-2)的上升沿的计数被示为在时刻t612、t620和t628被接收。因此,信号count-2(104-2)被示为具有t612-t620之间的值310、t620-t628之间的值394以及t628-t632之间的值478。信号count2-q(406-2)为信号count-2(104-2)的值,但是被触发器,即第二计数发生器405-2延迟信号clk-dig-tdc(307)的一个时钟周期。因此,当信号count-2(104-2)具有在t612开始的值310时,信号count2-q(406-2)被示为具有在t614开始的值310(在信号clk-dig-tdc(307)的一个周期之后)。因此,信号count2-q(406-2)被示为具有t614-t622之间的值310、t622-t630之间的值394以及t630-t632之间的值478。151.当信号count-2(104-2)的值不等于信号count2-q(406-2)的值时,断言信号unique-count2(501-2)。换句话说,当输入时钟clk-in-2(101-2)的计数已经历与其在信号clk-dig-tdc(307)的先前时钟周期中的值相比的变化时,信号unique-count2(501-2)被设置为逻辑高电平。因此,当信号count-2(104-2)的值不等于信号count2-q(406-2)的值时,信号unique-count2(501-2)被示为仅在时间间隔t612-t614、t620-t622和t628-t630中被断言。152.如上相对于图5所述,信号unique-count2-q(411-2)基于以下逻辑来确定:if (window-identifier && !unique-count2) unique-count2-q = 0else if (unique-count2)unique-count2-q = 1ꢀ…………(逻辑1.2)如上相对于信号unique-count1-q(411-1)所述,基于在当前时刻之前一个时钟周期的信号window-identifier(332)和信号unique-count2(501-2)的值来评估上述逻辑。因此,在t612,考虑进行评估的信号window-identifier(332)的值为逻辑低电平(时间间隔t610-t612中的值),并且考虑进行评估的信号unique-count2(501-2)的值为逻辑高电平。因此,第二唯一发生器410-2评估逻辑1.2,并且在t612开始信号unique-count2-q(411-2)保持在逻辑低电平。153.类似地,在t614,对于逻辑1.2的评估,信号window-identifier(332)的值为逻辑低电平,并且信号unique-count2(501-2)的值为逻辑高电平。因此,第二唯一发生器410-2评估上述逻辑1.2,并且在t614开始将信号unique-count2-q(411-2)设置为逻辑高电平。154.当信号unique-count2-q(411-2)在t614被设置为逻辑高电平时,信号window-identifier(332)也变为逻辑高电平,因为信号unique-count1-q(411-1)和信号unique-count2-q(411-2)两者都为逻辑高电平。如上所述,在t616,即在信号clk-dig-tdc(307)的一个时钟周期之后,信号window-identifier(332)被解除断言。155.在t616,为了确定信号unique-count1-q(411-1),信号window-identifier(332)的值为逻辑高电平,并且信号unique-count1(501-1)的值为逻辑低电平。因此,信号unique-count1-q(411-1)在t616开始被设置为逻辑低电平。156.在t616,为了确定信号unique-count2-q(411-2),信号window-identifier(332)的值为逻辑高电平,并且信号unique-count2(501-2)的值为逻辑低电平。因此,信号unique-count2-q(411-2)在t616开始被设置为逻辑低电平。157.信号unique-count1-q(411-1)、信号unique-count2-q(411-2)和信号window-identifier(332)的值以类似的方式在直至t632的相应时刻生成,如图6所示。158.因此,信号window-identifier(332)被示为标识窗口的边界,其中每个窗口对应于输入时钟(在此图示中为输入时钟clk-in-1(101-1))的一对连续边沿。159.接下来描述针对具有整数相关倍频率的一对输入时钟生成信号unique-count(501, 411)和信号window-identifier(332)的方式。160.10.针对具有整数相关频率的一对输入时钟生成信号unique-count和信号max(446)、信号acc-pos-q(442)和信号acc-neg-q(452)的示例性波形。出于本说明书的目的,数据波形(信号count-1(104-1)、信号count1-q(406-1)、信号count-2(104-2)、信号count2-q(406-2)、信号running-count-diff(433)、信号pos-min(436)、信号neg-max(446)、信号acc-pos-q(442)、信号acc-neg-q(452))中的“x”值指示“无关”值。数据波形信号pos-min(436)中的值“max1”表示最大正阈值,即,在此情况下为(236-1)。175.输入时钟clk-in-1(101-1)的上升沿r11至r13被示为出现在相应时刻t810、t818和t826。因此,数字核心110接收信号count-1(104-1)的值289、373和457,分别对应于输入时钟clk-in-1(101-1)的每个上升沿。176.类似地,输入时钟clk-in-2(101-2)的上升沿r21至r23被示为出现在相应时刻t812、t820和t828。因此,数字核心110接收信号count-2(104-2)的值310、394和478,分别对应于输入时钟clk-in-2(101-2)的每个上升沿。因此,在例示性实施方案中,输入时钟clk-in-2(101-2)被示为相对于输入时钟clk-in-1(101-1)在相位上滞后(大约90度)。177.尽管对应于输入时钟(clk-in-1(101-1)和clk-in-2(101-2))的上升沿的计数(信号count-1(104-1)和信号count-2(104-2))被示为与相应上升沿同步地被接收,但是实际上,计数可以比输入时钟clk-in-1(101-1)和输入时钟clk-in-2(102-2)的对应上升沿的出现稍晚地被接收。178.响应于信号count-2(104-2)在t812改变其值(至310),在信号clk-dig-tdc(307)的一个时钟周期内,在t814断言信号window-identifier(332)。因此,在t816开始,测量输入时钟clk-in-1(101-1)与输入时钟clk-in-2(101-2)之间的相位差。179.基于持续时间中的值(信号count1-q(406-1)减去信号count2-q(406-2))(基于上述流水线延迟),信号running-count-diff(433)被示为在相应时间间隔中具有以下值:t816-t818:running-count-diff (433) = 289ꢀ‑ꢀ310 =ꢀ‑21t818-t820:running-count-diff (433) = 289ꢀ‑ꢀ310 =ꢀ‑21t820-t822:running-count-diff (433) = 289ꢀ‑ꢀ310 =ꢀ‑21t822-t824:running-count-diff (433) = 373ꢀ‑ꢀ310 = 63持续时间t816-t822中的相位差表示输入时钟clk-in-2(101-2)的上升沿r21与输入时钟clk-in-1(101-1)的上升沿r11之间的相位差,而持续时间t822-t824中的相位差表示输入时钟clk-in-2(101-2)的上升沿r22与输入时钟clk-in-1(101-1)的上升沿r12之间的相位差。180.在t818,正最小值发生器435在路径332上接收逻辑高电平(信号window-identifier)并且在路径433上接收值“‑21”(信号running-count-diff)。因此,正最小值发生器435在t818将信号pos-min(436)的值设置为max1。181.在t820,正最小值发生器435在路径332上接收逻辑低电平(信号window-identifier)并且在路径433上接收值“‑21”(信号running-count-diff)。因此,正最小值发生器在t820保持信号pos-min(436)的当前值,即max1。以这种方式,信号pos-min(436)的值被示为基于信号window-identifier(332)、信号running-count-diff(433)的值和信号pos-min(436)的当前值来更新。182.在t818,负最大值发生器445在路径332上接收逻辑高电平(信号window-identifier)并且在路径433上接收值“‑21”(信号running-count-diff)。因此,负最大值发生器445将信号neg-max(446)的值设置为信号running-count-diff(433)的值,即“‑21”。183.在t820,负最大值发生器445在路径332上接收逻辑低电平(信号window-identifier)并且在路径433上接收值“‑21”(信号running-count-diff)。因此,负最大值发生器445保持信号neg-max(446)的当前值,即,在t820处的“‑21”。以这种方式,信号neg-max(446)的值被示为基于信号window-identifier(332)、信号running-count-diff(433)的值和信号neg-max(446)的当前值来更新/保持。184.使用如上所述的类似操作,tdc 100确定对于相位差的其他值(超前或滞后)具有相等频率的周期性时钟输入之间的相位差。185.接下来用示例示出tdc 100确定具有整数相关倍数(2倍或更大)的频率的一对输入时钟之间的相位差的方式。186.12.确定具有整数相关倍频率的一对输入时钟之间的相位差图8b是示出tdc 100测量具有整数相关倍频率的一对时钟之间的相位差的方式的时序图(未按比例绘制)。图8b示出了信号clk-dig-tdc(307)、输入时钟clk-in-1(101-1)、信号count-1(104-1)、信号count1-q(406-1)、信号unique-count1(501-1)、信号unique-count1-q(411-1)、输入时钟clk-in-2(101-2)、信号count-2(104-2)、信号count2-q(406-2)、信号unique-count2(501-2)、信号unique-count2-q(411-2)、信号window-identifier(332)、信号running-count-diff(433)、信号pos-min(436)、信号neg-max(446)、信号acc-pos-q(442)和信号acc-neg-q(452)的示例性波形。这些波形对应于图8a中所示的那些,并且为了简洁起见,此处不再重复其描述。在此例示性实施方案中,对应于输入时钟(clk-in-1(101-1)和clk-in-2(101-2))的计数被假定为36位。187.如上相对于图7所述,输入时钟clk-in-1(101-1)的频率被示为输入时钟clk-in-2(101-2)的8倍。因此,输入时钟clk-in-1(101-1)的8个上升沿(d11至d18)被示为存在于输入时钟clk-in-2(101-2)的2个连续上升沿(d21, d22)之间。188.此外,如上相对于图7所述,信号count-1(104-1)和信号count-2(104-2)分别比输入时钟clk-in-1(101-1)和输入时钟clk-in-2(102-2)的对应上升沿的出现稍晚地被接收。因此,在t854接收的信号count-1(104-1)对应于被示为在t852出现的输入时钟clk-in-1(101-1)的上升沿d11,而在t854接收的信号count-2(104-2)对应于被示为在t851出现的输入时钟clk-in-2(101-2)的上升沿d21。189.响应于信号count-2(104-2)在t854改变其值(至281),在信号clk-dig-tdc(307)的一个时钟周期内,在t855断言信号window-identifier(332)。因此,在t856(断言信号window-identifier(332)之后的一个时钟周期)开始,测量较慢时钟clk-in-2(101-2)的上升沿d21与较快时钟clk-in-1(101-1)的每个上升沿(d11至d18)之间的相位差,其中所述每个上升沿存在于较慢时钟clk-in-2(101-2)的两个连续边沿d21与d22之间。190.基于持续时间中的值(信号count1-q(406-1)减去信号count2-q(406-2))(基于上述流水线延迟),信号running-count-diff(433)被示为在相应时间间隔中具有以下值:t856-t859:running-count-diff (433) = 297ꢀ‑ꢀ281 = 16t859-t861:running-count-diff (433) = 381ꢀ‑ꢀ281 = 100t861-t863:running-count-diff (433) = 465ꢀ‑ꢀ281 = 184t863-t865:running-count-diff (433) = 549ꢀ‑ꢀ281 = 268t865-t867:running-count-diff (433) = 633ꢀ‑ꢀ281 = 452t867-t869:running-count-diff (433) = 717ꢀ‑ꢀ281 = 436t869-t874:running-count-diff (433) = 801ꢀ‑ꢀ281 = 520t874-t877:running-count-diff (433) = 885ꢀ‑ꢀ281 = 604因此,信号running-count-diff(433)被示为具有8个不同的值,其中每个值表示输入时钟clk-in-2(101-2)的上升沿d21与(时钟clk-in-1(101-1)的)上升沿d11至d18中的对应一者之间的相位差。191.在t857之前,作为输入时钟clk-in-2(101-2)的两个连续上升沿之间的先前(未示出)最小相位差的结果,信号pos-min(436)被示为具有值17。在t857,正最小值发生器435接收信号running-count-diff(433)的值为16,并且在路径332上接收逻辑高电平(信号window-identifier),因此,正最小值发生器435在t857将信号pos-min(436)更新为信号running-count-diff(433)的值,即16。在t857与t876之间,由于信号running-count-diff(433)值均未超过当前值16,所以正最小值发生器435将信号pos-min(436)的值保持在其当前值,即16。192.在t857之前,信号neg-max(446)被示为具有大的负值(-236-1)。在t857开始,由于所有相位差值均为正,所以负最大值发生器445将信号neg-max(446)保持在大的负值。193.在t875,再次断言信号window-identifier(332)信号,指示输入时钟clk-in-2(101-2)的下一上升沿(d22)的出现。可以观察到,值16是在两个信号window-identifier(332)脉冲之间所测量的所有8个差值中的最小相位差。因此,在t875处,输入时钟clk-in-1(101-2)与输入时钟clk-in-2(101-2)之间的相位差被确定为16。如上所述,频率为整数相关倍数的一对输入时钟的相位差是较慢时钟的边沿出现与较快时钟的最近边沿出现之间的时间。194.根据本公开的另一方面,tdc 100进行操作以在输入时钟中的任一者中存在抖动时生成相位差。接下来用示例描述tdc在存在抖动的情况下进行操作的方式。195.13.当输入时钟信号中存在抖动时tdc的操作图9a和图9b一起示出在本发明的一个实施方案中tdc利用具有抖动的输入时钟信号的操作。具体地,图9a是示出tdc 100识别输入时钟信号中存在抖动的方式的时序图(未按比例绘制)。图9a示出了信号clk-dig-tdc(307)、输入时钟clk-in-1(101-1)、信号count-1(104-1)、信号count1-q(406-1)、信号unique-count1(501-1)、信号unique-count1-q(411-1)、输入时钟clk-in-2(101-2)、信号count-2(104-2)、信号count2-q(406-2)、信号unique-count2(501-2)、信号unique-count2-q(411-2)、信号window-identifier(332)、信号running-count-diff(433)、信号pos-min(436)、neg-max(446)、信号acc-pos-q(442)和信号acc-neg-q(452)的示例性波形。这些波形对应于图8a中所示的那些,并且为了简洁起见,此处不再重复其描述。另外,图9a示出了信号jitter-present(392)和信号use-jitter-approach(393)的示例性波形。在此例示性实施方案中,对应于输入时钟(clk-in-1(101-1)和clk-in-2(101-2))的计数被假定为36位。196.在示例性实施方案中,输入时钟clk-in-1(101-1)和输入时钟clk-in-2(101-2)表示具有相同频率的一对时钟,其中在输入时钟clk-in-2(101-2)中伴随有抖动。输入时钟clk-in-1(101-1)的上升沿r31至r34被示为出现在相应时刻t910、t915、t919和t928。因此,核心逻辑110接收信号count-1(104-1)的值289、373、457和541,分别对应于输入时钟clk-in-1(101-1)的每个上升沿。197.在图9a中,输入时钟clk-in-2(101-2)被示为具有抖动。因此,输入时钟clk-in-2(101-2)的一些上升沿(诸如边沿r42和r44)被示为稍微早于输入时钟clk-in-1(101-1)的对应上升沿(即分别为r32和r34)出现,诸如在一些周期中的时刻t914和t926,而输入时钟clk-in-2(101-2)的一些上升沿(诸如边沿r41和r43)被示为稍微晚于输入时钟clk-in-1(101-2)的相应上升沿(即分别为r31和r33)出现,诸如在一些周期内的时刻t912和t920。198.基于持续时间中的值(信号count1-q(406-1)减去信号count2-q(406-2))(基于上述流水线延迟),信号running-count-diff(433)被示为在相应时间间隔中具有以下值:t913-t916:running-count-diff (433) = 289ꢀ‑ꢀ290 =ꢀ‑1t916-t917:running-count-diff (433) = 289ꢀ‑ꢀ372 =ꢀ‑83t917-t921:running-count-diff (433) = 373ꢀ‑ꢀ372 = 1t921-t923:running-count-diff (433) = 457ꢀ‑ꢀ372 = 85因此,输入时钟clk-in-2(101-2)中的抖动被示为导致正相位差和负相位差。可以观察到,在某些类型的抖动(诸如随机抖动)中,抖动引起正相位误差和负相位误差的概率可以基本上相等。199.正最小值发生器435和负最大值发生器445根据上述逻辑进行操作,并且因此生成如图9a所示的信号pos-min(436)和信号neg-max(446)。在t916,断言信号window-identifier(332),并且因此在t918,将信号pos-min(436)加到正累加器440中的当前累加值。因此,在t918开始,信号acc-pos-q(442)被示为具有值“max1”。200.在t916,断言信号window-identifier(332),并且因此在t918,将信号neg-max(446)加到负累加器450中的当前累加值。因此,信号acc-neg-q(452)被示出为在时间间隔t918-t924中具有值“‑1”。在t924,将值“max2”加到信号acc-neg-q(452),从而在负累加器450中生成值“max2-1”。201.可以观察到,正累加器440和负累加器450两者累加大的值,超过相应阈值(即,正累加器440的“max1”,以及负累加器450的“max2”)。这在信号running-count-diff(433)中存在足够数量的正值和负值时发生。在不存在抖动时,仅一个累加器(正累加器440或负累加器450,但不是两者)累加阈值。例如,在图8a的图示中(输入时钟clk-in-2(101-2)在相位上滞后输入时钟clk-in-1(101-1)),仅正累加器440累加阈值。在图8b的图示中(输入时钟clk-in-2(101-2)在相位上超前输入时钟clk-in-1(101-1)),仅负累加器450累加阈值。202.当正累加器440和负累加器450两者累加大的值时,指示输入时钟信号中的任一者中存在抖动,所述任一者原本具有零相位差。203.在时间间隔t918-t924中,抖动检测器460检查信号acc-pos-q(442)和信号acc-neg-q(452)两者的值是否已超过相应阈值。信号acc-pos-q(442)超过相应阈值,而信号acc-neg-q(452)没有超过相应阈值。因此,抖动检测器460不在路径392上生成逻辑高电平(信号jitter-present)。204.在t924,抖动检测器460检查信号acc-pos-q(442)和信号acc-neg-q(452)两者的值是否已超过相应阈值。抖动检测器460确定两个累加器都已超过相应阈值。因此,抖动检测器460在路径392上生成逻辑高电平(信号jitter-present)。如上所述,抖动检测器460在信号clk-dig-tdc(307)的一个时钟周期之后解除断言信号jitter-present(392)。此外,在t924,抖动检测器460在路径393上生成逻辑高电平(信号use-jitter-approach)。抖动检测器460保持断言信号use-jitter-approach(逻辑高电平)直到预先确定数量的相位差样本的累加结束(由在路径447上断言信号nsample-done来指示),此后抖动检测器460解除断言信号use-jitter-approach(393)。205.在t926,作为在路径392上接收到逻辑高电平(信号jitter-present)的结果,正累加器440和负累加器450清除(设置为边界值,例如零)相应累加值(信号acc-pos-q(442)和信号acc-neg-q(452))。因此,在t926开始,信号acc-pos-q(442)和信号acc-neg-q(452)被示为具有零值。类似地,在t926开始,正最小值发生器435和负最大值发生器445在路径392上接收到逻辑高电平(信号jitter-present)时也清除(设置为边界值,例如零)相应值,并且因此被示为具有零值。此外,在t926,窗口计数器444将采样计数器重置为零,从而结束当前的累加周期并开始(预先确定数量的窗口的)新累加周期。206.在一个实施方案中,仅重新启动正累加器440,并且在存在抖动的情况下不使用负累加器450。图9b是示出本公开的一个实施方案中tdc 100进行操作以在存在抖动的情况下提供相位差的方式的时序图(未按比例绘制)。图9b的时序图示出了在图9a的时刻t930之后的tdc的操作。207.因此,图9b的示例性波形,即信号clk-dig-tdc(307)、输入时钟clk-in-1(101-1)、信号count-1(104-1)、信号count1-q(406-1)、信号unique-count1(501-1)、信号unique-count1-q(411-1)、输入时钟clk-in-2(101-2)、信号count-2(104-2)、第二计数count2-q(406-2)、信号unique-count2(501-2)、信号unique-count2-q(411-2)、信号window-identifier(332)、信号running-count-diff(433)、信号pos-min(436)、信号neg-max(446)、信号acc-pos-q(442)和信号acc-neg-q(452)对应于图9a中所示的那些,并且为了简洁起见,此处不再重复其描述。208.如上相对于图9a所述,在t940之前,已识别出存在抖动,并且正累加器440和负累加器450已被重置为边界值(例如,在例示性实施方案中为零)。209.在t940开始,正累加器440如下所述累加相位差值,而负累加器450不累加任何值。输入时钟clk-in-2(101-2)被示为持续具有抖动。由于信号use-jitter-approach(393)(未示出)为逻辑高电平(在图9a中的t924处开始),因此正累加器440计算在每个窗口中接收的信号pos-min(436)和信号neg-max(446)的较低量值(绝对最小值),并且将具有对应符号的计算的值累加(添加)到正累加器440的当前值。210.因此,在t948,正累加器440计算值“max1”和“‑1”中的较低最小值,并且将“‑1”加到信号acc-pos-q(442)(在此情况下为零)。类似地,在t954,正累加器440计算值“1”和“max2”中的较低最小值,并且将“+1”加到信号acc-pos-q(442)(在此情况下为“‑1”),从而生成“0”。使用类似的操作,信号acc-pos-q(442)被示为在时间间隔t948-t954中具有值“‑1”,在时间间隔t954-t960中具有值“0”,在时间间隔t960-966中具有值“‑1”。211.因此,累加相位差基本上等于零或非常小的值。累加值除以累加的样本数量(等于窗口数量,例如1024)被提供为输入时钟之间的相位差。212.可以理解,对于给定的抖动量值(信号jitter-input),累加的样本数量越多(即,求平均时间越长),估计相位差的精度就越高。在求平均之后,输入时钟中的抖动可以被减少信号jitter-input/sqrt(nsample)。213.尽管图9a和图9b中所描绘的例示性实施方案是相对于具有相同频率的输入时钟来描述的,但本发明的各方面适用于具有大于一的整数相关倍频率的输入时钟。214.此外,尽管正累加器440、运行累加器数据发生器465和累加器有效数据发生器475被示为在存在抖动的情况下使用另选逻辑来进行操作,但是在另选实施方案中,这样的逻辑可以在对信号路径进行适当改变的情况下在单独的模块中实现。此外,在另选实施方案中,当存在抖动时,可将正累加器440的输出提供为单独路径上的累加相位差。215.根据本公开的另一方面,tdc 100累加输入时钟(clk-in-1(101-1)和clk-in-2(101-2))之间的预先确定数量(由用户提供)的相位差,并且对累加值求平均(即,累加值除以相位差样本的数量),以便潜在地提高分辨率,利用该分辨率可以确定相位差。接下来用示例描述实现这种累加的方式。216.14.相位差样本的累加图10是示出在本公开的一个实施方案中相位差样本的累加的时序图(未按比例绘制)。具体地,该图被示为包含信号running-acc-data(491)、信号nsample-done(447)、信号running-nsample(492)、信号output(115)和信号data-valid(493)的波形。路径115、493、491和493上的波形在tdc 100的模式(1)和(2)(如上所述)中可用。217.如前面相对于图4b所述,运行累加器数据发生器465生成信号running-acc-data(491)和信号running-nsample(492)。信号running-acc-data(491)表示在每个窗口结束时的累加相位差值。218.在输入时钟(clk-in-1(101-1)和clk-in-2(101-2)具有小频率(诸如约1赫兹)并且用户已编程了预先确定数量的要累加的相位差样本中相对高数量(比如1024)的样本的情况下,信号running-acc-data(491)是可取的。因此,每个累加周期将持续1024秒。在这种情况下,在累加数据在输出路径115上可用之前,用户需要等待1024秒(在累加周期开始之后)。同时,如果用户希望检查中间累加值(比如在累加周期开始后大约3秒或10秒),则用户可以通过在任何希望数量的窗口结束时读取在路径491上可用的累加数据(信号running-acc-data)来进行检查。219.参考图10,示出了两个累加周期,一个在时间间隔t1010-t1025之间,接下来一个在t1025-t1035之间。因此,在时刻t1020和t1032断言信号nsample-done(447)。220.在时刻t1025(在持续时间t1010-t1025内的第一累加周期结束时),路径115上的累加数据可用,并且被保持在该值(累加器有效数据1),直到下一累加周期完成(在这种情况下,直到t1035)。在t1025,还断言信号data-valid(493)以指示路径115上可用的数据是有效的。如果用户在时间间隔t1025-t1035期间读取路径115上的输出,则在t1025为用户提供更新的值(累加器有效数据1)。221.在模式(1)中,参考图8a,当累加周期在t830结束时(基于作为用户输入提供的预先确定数量的相位差样本),累加器有效数据发生器475确定信号acc-pos-q(442)和信号acc-neg-q(452)的绝对最小值,并且在路径115上提供值(信号output)。因此,在t830开始直到下一累加周期结束,值“21”被提供作为信号output(115)。222.在模式(2)中,参考图8b,在t857之前,作为先前累加(未示出)的结果,信号acc-pos-q(442)被示为具有值655。在t855,断言信号window-identifier(332),并且因此在t857,将信号pos-min(436)加到当前累加值。因此,在t857开始,信号acc-pos-q(442)被示为具有值(655 + 17),即672。在t878,在t875断言信号window-identifier(332)之后,将信号pos-min(436)加到当前累加值。因此,在t878开始,信号acc-pos-q(442)被示为具有值(672 + 16),即688。223.继续参考图8b,在t857之前,作为先前累加(未示出)的结果,信号acc-neg-q(452)被示出为具有大的负值(-236-1)。在t855,断言信号window-identifier(332),并且因此在t857,将信号neg-max(446)加到当前累加值。因此,在t857开始,信号acc-neg-q(452)被示为具有值-68,719,476,734。224.因此,当累加周期在t875结束时(基于作为用户输入提供的预先确定数量的相位差样本),累加器有效数据发生器475确定信号acc-pos-q(442)和信号acc-neg-q(452)的绝对最小值,并且在路径115上提供值(信号output)。因此,在t878开始直到下一累加周期结束,值672被提供作为信号output(115)。225.信号running-nsample(492)值在每次断言信号window-identifier(332)(未示出)时递增。每次断言信号window-identifier(332)(在每个窗口结束后)也更新数据信号running-acc-data(491)的每个值。因此,如果用户希望检查在累加周期的开始与结束之间的累加值,则用户可以读取路径491上的信号running-acc-data。路径492上可用的信号running-nsample数据指示路径491上可用的累加样本的数量。226.例如,现在参考图10,如果用户在时刻t1015读取信号running-acc-data(491),则信号running-nsample(492)指示已累加2个样本,并且信号acc-pos-q(442)和信号acc-neg-q(452)的绝对最小值在路径491上可用(信号running-acc-data)。227.在模式(1)中,参考图8a,正累加器440和负累加器450分别累加信号pos-min(436)和信号neg-max(446),如图8a所示。对于在路径491上作为输出提供的运行累加器数据,将确定信号acc-pos-q(442)和信号acc-neg-q(452)的瞬时值的绝对最小值。因此,信号running-acc-data(491)在持续时间t818-t826中提供值“21”,并且在持续时间t826-t832中提供值“42”。在模式(2)中,参考图8b,信号running-acc-data(491)提供持续时间t857-t878的值655,以及在t878开始的值672。因此,tdc 100以累加器模式(1)和(2)提供累加数据。228.以此方式,本发明的各方面使得tdc能够利用具有抖动的周期性输入进行操作。如上所述实现的tdc 100可以并入下文简要描述的更大的设备或系统中。229.15.系统图11是如上文详细描述的包含根据本公开的各种方面实现的锁相环的示例性信号处理系统的框图。系统1100被示为包含同步以太网(synce)定时卡-1 1110和同步以太网定时卡-2 1120以及线路卡1至n,为了简单起见,仅示出了其中的两个线路卡1130和1150。线路卡1130被示为包含抖动衰减器锁相环(jitter attenuator pll)1140和同步以太网 phy发射机1145。线路卡1150被示为包含抖动衰减器锁相环 1160和同步以太网 phy发射机1165。图11的部件可以按照同步以太网(synce)网络标准进行操作。如相关领域众所周知的,同步以太网是用于在基于分组的以太网中实现同步的基于物理层(phy)的技术。通过物理层发送的同步以太网时钟信号应可跟踪到外部主时钟(例如,来自定时卡诸如同步以太网定时卡1110或1120)。因此,以太网分组相对于主时钟被重新定时,然后在物理层中被发送。因此,数据分组(例如,在路径1131和路径1151上)被重新定时和发送,而没有任何时间戳信息被记录在该数据分组中。这些分组可以由对应应用诸如iptv(互联网协议电视)、voip(互联网协议语音)等生成。230.因此,线路卡1130在路径1131上接收分组,并且在分组已与主时钟重新定时(同步)之后在输出1146上转发该分组。类似地,线路卡1150在路径1151上接收分组,并且在分组已与主时钟重新定时(同步)之后在输出1166上转发该分组。231.主时钟(1111/时钟-1)由同步以太网定时卡-1 1110生成。同步以太网定时卡-2 1120生成冗余时钟(1121/时钟-2),该冗余时钟将在主时钟1111发生故障时由线路卡1130和1150使用。主时钟1111和冗余时钟1121经由背板(由数字1170表示)提供给线路卡1130和1150中的每一者。232.在线路卡1130中,抖动衰减器锁相环 1140可以包含tdc 100,以用于检测上面详细描述的其输入时钟之间的相位差,并且接收主时钟1111和冗余时钟1121。抖动衰减器锁相环 1140生成输出时钟1141,该时钟用于同步(重新定时)在路径1131上接收的分组,并且在路径1146上转发作为重新定时的分组。233.类似地,在线路卡1150中,抖动衰减器锁相环1160还可以包含tdc 100,以用于检测上面详细描述的其输入时钟之间的相位差,并且接收主时钟1111和冗余时钟1121。抖动衰减器锁相环 1160生成输出时钟1161,该时钟用于同步(重新定时)在路径1151上接收的分组,并且在路径1166上转发作为重新定时的分组。在失相时,抖动衰减器锁相环 1160被设计成以上面详细描述的方式提供相位锁定。234.16.结论本说明书通篇所提到的“一个实施方案”、“实施方案”或相似语言是指结合所述实施方案所描述的特定特征、结构或特性被包括在本公开的至少一个实施方案中。因此,本说明书通篇出现的短语“在一个实施方案中”、“在实施方案中”和相似语言可以但不一定全部是指同一个实施方案。235.应理解,上文所述的各模块/部件的特定结构或配置仅是作为例示。然而,通过阅读本文提供的公开内容,使用不同配置的另选实施方案对于相关领域的技术人员将是显而易见的。236.虽然上文已经描述了本公开的各种实施方案,但是应当理解,它们是仅作为示例而非限制来呈现的。因此,本公开的广度和范围不应受任何上述实施方案的限制,并且应当仅根据以下权利要求书及其等同物进行限定。凡是利用本技术说明书及附图内容所作的等效结构或等效流程变换,例如各实施例之间技术特征的相互结合,或直接或间接运用在其他相关的技术领域,均同理包括在本技术的专利保护范围内。

本文地址:https://www.jishuxx.com/zhuanli/20240730/150175.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

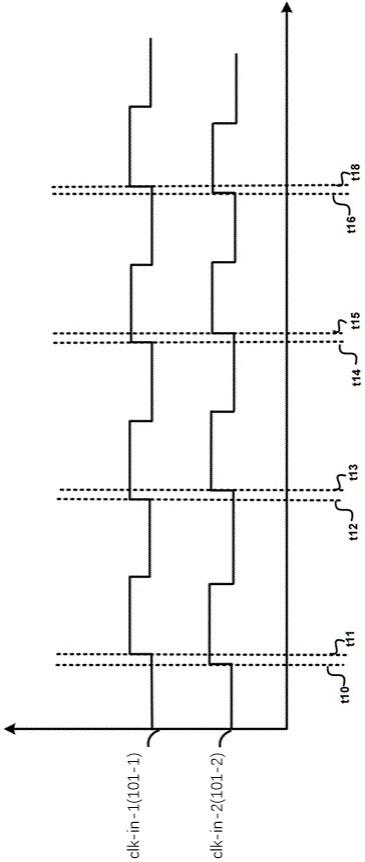

返回列表