基于嵌套时间放大与自动校准技术的高速时间数字转换器

- 国知局

- 2024-07-30 10:14:59

本发明属于时间数字转换器领域,具体涉及一种基于嵌套时间放大与自动校准技术的高速时间数字转换器。

背景技术:

1、模数转换器作为连接模拟世界和数字领域的桥梁,其性能限制着整个系统的性能;其中,时间域模数转换器尤其具备优秀的工艺适配性、较低的功耗和较小的面积的特性。随着工艺的持续进步,时间数字转换器(tdc)的分辨率和量化范围不断提高,使其成功应用于诸多领域,也对tdc的量化速度、精度和线性度方面提出了更高的要求,片内失配及带内噪声已成为无法忽略的限制tdc性能的关键因素。

2、由于流水线型时间数字转换器可以并行量化的特点,能做到多级子tdc流水线工作,达到较高的量化速度。但其级间一般采用时间余量放大器传递余量,随着集成电路工艺节点演进到纳米级别,mos管本征增益退化等诸多问题导致时间余量放大器增益随工艺、电压和温度参数的变化较为敏感,引入余量放大器导致了电路复杂度高且功耗增大;此外,片内失配具体表现为延迟单元形成的门控延迟链的孔径误差,也并未得到有效限制。

技术实现思路

1、为了解决现有技术中存在的上述问题,本发明提供了一种基于嵌套时间放大与自动校准技术的高速时间数字转换器。本发明要解决的技术问题通过以下技术方案实现:

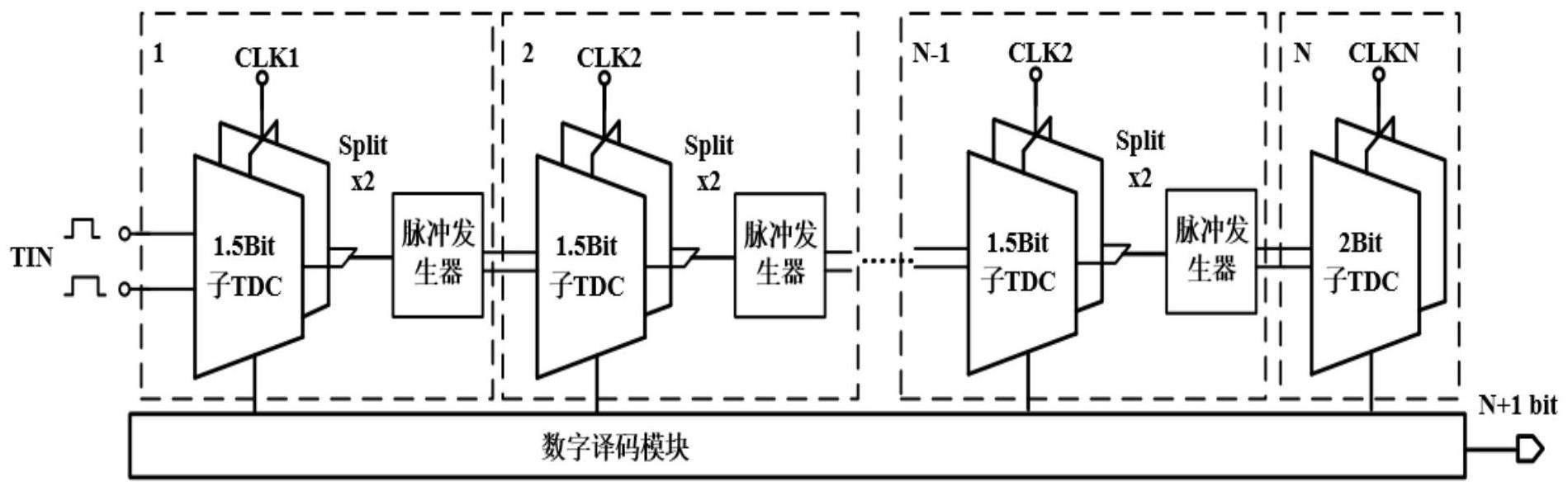

2、本发明提供了一种基于嵌套时间放大与自动校准技术的高速时间数字转换器,其特征在于,包括:n级tdc模块、脉冲发生器和数字译码模块;

3、相邻的两级所述tdc模块通过所述脉冲发生器连接,形成n级流水线架构,每级所述tdc模块的量化输出端均连接所述数字译码模块;

4、前n-1级tdc模块结构相同,均包括级联的两个低位子tdc模块;第n级tdc模块,包括级联的两个高位子tdc模块;所述低位子tdc模块与所述高位子tdc模块的量化位数不同;

5、每一级tdc模块对输入的时间信号量化产生对应的温度码和full信号,与其连接的所述脉冲发生器根据所述full信号和外部trigger信号的差值产生时间余量信号,其中,第一级tdc模块的输入端输入外部时间信号tin和外部trigger信号;前一级脉冲发生器产生的时间余量信号作为后一级tdc模块输入的时间信号;每一级tdc模块产生的温度码均输入至所述数字译码模块,所述数字译码模块对所述温度码译码处理后得到数字码dout并将其输出。

6、在本发明的一个实施例中,所述高位子tdc模块和所述低位子tdc模块的结构相同,所述高位子tdc模块的量化位数比所述低位子tdc模块的量化位数高1lsb。

7、在本发明的一个实施例中,所述低位子tdc模块包括:或门r1、开关s1、开关s2、开关s3、d触发器dff1、d触发器dff2、延迟单元tq1、延迟单元tq2、延迟单元tq3、延迟单元tq4、延迟单元tq5、延迟单元tq6、延迟单元tq7和延迟单元tq8;

8、其中,所述或门r1的第一输入端输入所述外部trigger信号,第二输入端输入所述时间信号,所述或门r1的输出端输出使能信号en;

9、所述延迟单元tq1、所述延迟单元tq2、所述延迟单元tq3、所述延迟单元tq4、所述延迟单元tq5、所述延迟单元tq6、所述延迟单元tq7和所述延迟单元tq8依次串联形成延迟链,其控制端均连接所述或门r1的输出端;

10、所述延迟单元tq1的输入端输入复位set信号;

11、所述开关s1的第一端连接在所述延迟单元tq4的输出端和所述延迟单元tq5的输入端之间,所述开关s2的第一端连接在所述延迟单元tq6的输出端和所述延迟单元tq7的输入端之间,所述开关s3的第一端连接所述延迟单元tq8的输出端;

12、所述开关s1的第二端、所述开关s2的第二端和所述开关s3的第二端相连接并作为所述full信号的输出端;

13、所述d触发器dff1的第一输入端连接在所述延迟单元tq3的输出端和所述延迟单元tq4的输入端之间,所述d触发器dff2的第一输入端连接在所述延迟单元tq5的输出端和所述延迟单元tq6的输入端之间;所述d触发器dff1的第二输入端和所述d触发器dff2的第二输入端均输入时钟信号clk;

14、所述d触发器dff1的输出端输出第一温度码d0,所述d触发器dff2的输出端输出第二温度码d1。

15、在本发明的一个实施例中,所述时间信号包括:一级时间信号t1和二级时间信号t2,且满足:

16、t2=t1+δt;

17、其中,tq为一个延迟单元的延迟时间。

18、在本发明的一个实施例中,在前n-1级的tdc模块中,

19、第一个低位子tdc模块对输入的所述一级时间信号t1和所述外部trigger信号,量化产生一级full信号;

20、第二个低位子tdc模块对输入的所述二级时间信号t2和所述一级full信号,量化产生二级full信号,将所述二级full信号作为tdc模块产生的full信号输入至所述脉冲发生器。

21、在本发明的一个实施例中,所述时间余量信号包括:所述第一个低位子tdc模块的余量信息和所述第二个低位子tdc模块的余量信息;

22、其中,所述第一个低位子tdc模块的余量信息包括第一孔径误差,所述第二个低位子tdc模块的余量信息包括第二孔径误差;

23、所述第一孔径误差与所述第二孔径误差的取值正负相反。

24、与现有技术相比,本发明的有益效果在于:

25、本发明的基于嵌套时间放大与自动校准技术的高速时间数字转换器,使用n级流水线架构,每级包括两级子tdc模块,输出的时间余量信号携带了两级子tdc的余量信息,避免了时间余量放大器的使用,有效降低了电路的复杂度及功耗。同时,采用拆分校准技术,两级子tdc模块对孔径误差进行自动校准,实现了更高的线性度,而噪声性能维持不变。

26、上述说明仅是本发明技术方案的概述,为了能够更清楚了解本发明的技术手段,而可依照说明书的内容予以实施,并且为了让本发明的上述和其他目的、特征和优点能够更明显易懂,以下特举较佳实施例,并配合附图,详细说明如下。

技术特征:1.一种基于嵌套时间放大与自动校准技术的高速时间数字转换器,其特征在于,包括:n级tdc模块、脉冲发生器和数字译码模块;

2.根据权利要求1所述的基于嵌套时间放大与自动校准技术的高速时间数字转换器,其特征在于,所述高位子tdc模块和所述低位子tdc模块的结构相同,所述高位子tdc模块的量化位数比所述低位子tdc模块的量化位数高1lsb。

3.根据权利要求1所述的基于嵌套时间放大与自动校准技术的高速时间数字转换器,其特征在于,所述低位子tdc模块包括:或门r1、开关s1、开关s2、开关s3、d触发器dff1、d触发器dff2、延迟单元tq1、延迟单元tq2、延迟单元tq3、延迟单元tq4、延迟单元tq5、延迟单元tq6、延迟单元tq7和延迟单元tq8;

4.根据权利要求3所述的基于嵌套时间放大与自动校准技术的高速时间数字转换器,其特征在于,

5.根据权利要求4所述的基于嵌套时间放大与自动校准技术的高速时间数字转换器,其特征在于,在前n-1级的tdc模块中,

6.根据权利要求5所述的基于嵌套时间放大与自动校准技术的高速时间数字转换器,其特征在于,

技术总结本发明涉及一种基于嵌套时间放大与自动校准技术的高速时间数字转换器,包括:N级TDC模块、脉冲发生器和数字译码模块;相邻的两级TDC模块通过脉冲发生器连接,形成N级流水线架构,每级TDC模块的量化产生温度码,输入至数字译码模块;数字译码模块对温度码译码处理后得到数字码Dout并将其输出。前N‑1级TDC模块结构相同,均包括级联的两个低位子TDC模块;第N级TDC模块,包括级联的两个高位子TDC模块。本发明使用N级流水线架构,每级包括两级子TDC模块,避免了时间余量放大器的使用,两级子TDC模块对孔径误差进行自动校准,实现了更高的线性度,而噪声性能维持不变。技术研发人员:丁瑞雪,仵梦童,沈易,李伟健,刘术彬,朱樟明受保护的技术使用者:西安电子科技大学技术研发日:技术公布日:2024/1/14本文地址:https://www.jishuxx.com/zhuanli/20240730/152033.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表