一种方便线路连接的集成电路测试方法及系统与流程

- 国知局

- 2024-07-30 11:04:26

本发明涉及集成电路测试,尤其涉及一种方便线路连接的集成电路测试方法及系统。

背景技术:

1、集成电路的测试是集成电路生产过程中不可或缺的一个重要环节,其目的是验证生产出的集成电路是否符合设计要求,性能指标是否达标,传统的集成电路测试方法主要包括探针测试和负载板测试两种,探针测试是指利用探针台将细小的探针直接与集成电路的引脚接触,通过向引脚施加测试信号和采集引脚输出信号,来判断集成电路的功能和性能是否合格,负载板测试是指将被测集成电路装配到专门设计的负载板上,通过负载板上的连接器或者焊盘与集成电路引脚相连,再利用自动测试设备向集成电路施加测试信号和采集输出信号;

2、但是,探针测试对探针的精度和可靠性要求很高,且当集成电路引脚数量增多、间距减小时,探针的制作和操作难度加大,测试成本升高,负载板测试虽然克服了探针测试的部分缺陷,但是负载板的设计和制作较为复杂,且每种集成电路都需要专门的负载板,通用性差,成本较高;

3、因此,亟需一种方法解决现有技术中存在的问题。

技术实现思路

1、本发明实施例提供一种方便线路连接的集成电路测试方法及系统,至少能解决现有技术中存在的部分问题。

2、本发明实施例的第一方面,提供一种方便线路连接的集成电路测试方法,包括:

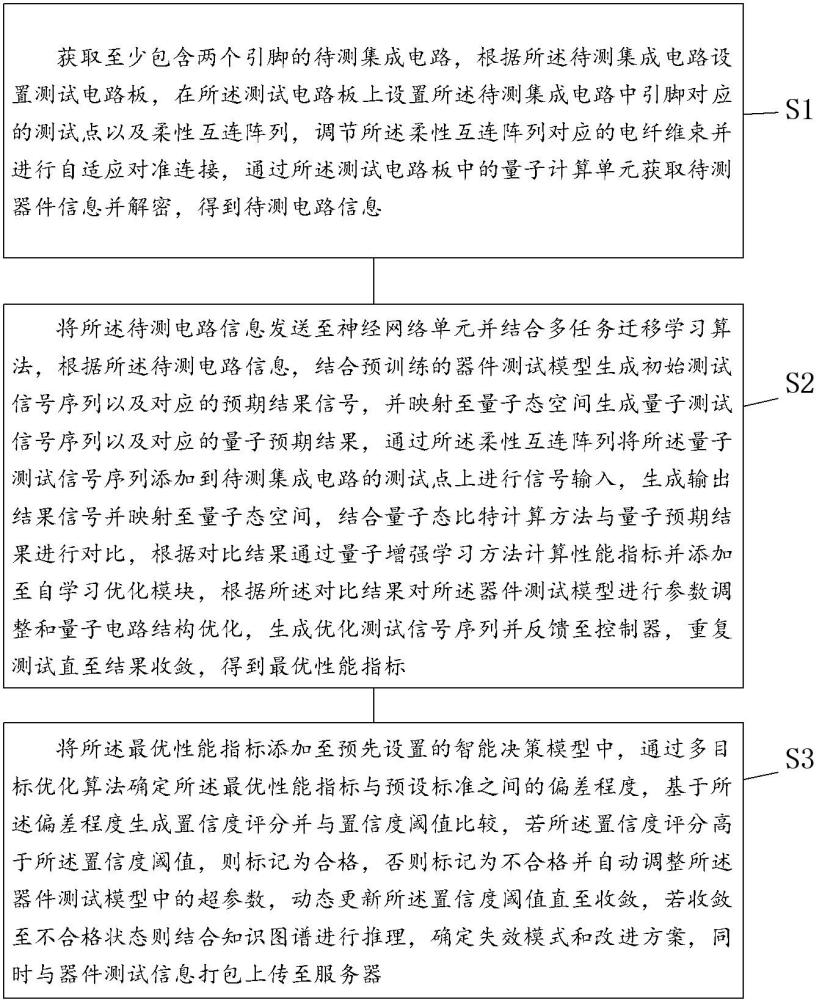

3、获取至少包含两个引脚的待测集成电路,根据所述待测集成电路设置测试电路板,在所述测试电路板上设置所述待测集成电路中引脚对应的测试点以及柔性互连阵列,调节所述柔性互连阵列对应的电纤维束并进行自适应对准连接,通过所述测试电路板中的量子计算单元获取待测器件信息并解密,得到待测电路信息;

4、将所述待测电路信息发送至神经网络单元并结合多任务迁移学习算法,根据所述待测电路信息,结合预训练的器件测试模型生成初始测试信号序列以及对应的预期结果信号,并映射至量子态空间生成量子测试信号序列以及对应的量子预期结果,通过所述柔性互连阵列将所述量子测试信号序列添加到待测集成电路的测试点上进行信号输入,生成输出结果信号并映射至量子态空间,结合量子态比特计算方法与量子预期结果进行对比,根据对比结果通过量子增强学习方法计算性能指标并添加至自学习优化模块,根据所述对比结果对所述器件测试模型进行参数调整和量子电路结构优化,生成优化测试信号序列并反馈至控制器,重复测试直至结果收敛,得到最优性能指标;

5、将所述最优性能指标添加至预先设置的智能决策模型中,通过多目标优化算法确定所述最优性能指标与预设标准之间的偏差程度,基于所述偏差程度生成置信度评分并与预先设置的置信度阈值比较,若所述置信度评分高于所述置信度阈值,则标记为合格,否则标记为不合格并自动调整所述器件测试模型中的超参数,动态更新所述置信度阈值直至收敛,若收敛至不合格状态则结合知识图谱进行推理,确定失效模式和改进方案,同时与器件测试信息打包上传至服务器。

6、在一种可选的实施方式中,

7、获取至少包含两个引脚的待测集成电路,根据所述待测集成电路设置测试电路板,在所述测试电路板上设置所述待测集成电路中引脚对应的测试点以及柔性互连阵列,调节所述柔性互连阵列对应的电纤维束并进行自适应对准连接,通过所述测试电路板中的量子计算单元获取待测器件信息并解密,得到待测电路信息包括:

8、通过光学字符识别技术对待测集成电路的原理图进行文字提取和符号提取,结合卷积神经网络模型识别所述原理图中的元器件和引脚,将获取到的信息转化为结构化数据表示,生成数据化原理图,对于所述数据化原理图,通过语义解析算法分析元器件类型和位置以及连线的拓扑关系,推断得到所述待测集成电路的功能结构和引脚属性,并以电路网表形式输出,动态解析所述电路网表并确定引脚驱动方式和负载特性,计算得到测试点阻抗范围;

9、基于所述测试点阻抗范围,结合引脚属性,通过启发式搜索算法,以最小化测试点之间的串扰为目标,在测试电路板的布线空间内自动生成最优测试点布局,基于所述最优测试点布局,通过计算机软件对柔性互连阵列进行虚拟装配,结合仿真分析验证所述柔性互连阵列与测试点的对准精度,基于对准精度优化电纤维束的排布方式,同时评估所述柔性互连阵列的机械应力分布,通过基于强化学习的参数优化算法最小化互连阵列的接触电阻,重复优化,得到最优布线信息;

10、将所述最优布线信息通过量子计算单元进行量子态编码,将经典比特映射至量子比特的基矢状态,并构建一个与密钥长度对应的量子态空间,在所述量子态空间中进行密钥搜索,通过振幅放大和振幅估计对密钥组合进行量子并行计算,结合非概率性量子行走,得到密钥量子态,解码得到待测器件信息,通过量子计算单元进行可测性分析,根据可测性分析结果生成所述待测电路信息。

11、在一种可选的实施方式中,

12、以最小化测试点之间的串扰为目标,在测试电路板的布线空间内自动生成最优测试点布局如下公式所示:

13、;

14、其中, cc表示测试点之间的串扰, ε为介质常数,表示材料的电容率, w表示线宽, l表示耦合长度, d表示线间距离, γ表示高宽比修正系数, ar表示高宽比, δ表示形状不规则系数对应的修正系数, sr为形状不规则系数,表示互连线段形状的不规则程度。

15、在一种可选的实施方式中,

16、将所述待测电路信息发送至神经网络单元并结合多任务迁移学习算法,根据所述待测电路信息,结合预训练的器件测试模型生成初始测试信号序列以及对应的预期结果信号,并映射至量子态空间生成量子测试信号序列以及对应的量子预期结果,通过所述柔性互连阵列将所述量子测试信号序列添加到待测集成电路的测试点上进行信号输入,生成输出结果信号并映射至量子态空间,结合量子态比特计算方法与量子预期结果进行对比,根据对比结果通过量子增强学习方法计算性能指标并添加至自学习优化模块,根据所述对比结果对所述器件测试模型进行参数调整和量子电路结构优化,生成优化测试信号序列并反馈至控制器,重复测试直至结果收敛,得到最优性能指标包括:

17、将所述待测电路信息发送至预先训练完成的神经网络单元,结合多任务迁移学习算法在对个电路测试任务上联合训练所述神经网络单元,通过图卷积网络与注意力机制自适应学习待测电路对应的电路特征表示;

18、基于所述电路特征表示,通过预训练的器件测试模型,以电路特征为条件生成符合当前电路特性的初始测试信号序列以及对应的预期信号结果,将所述初始测试信号序列通过量子态编码电路映射至量子态空间,将经典比特串转换为量子态比特串,得到量子测试信号序列以及对应的量子预期结果;

19、基于柔性互连阵列中的量子通道,通过选择性的激活所述量子通道将编码后的量子测试信号施加到所述待测集成电路的测试点上,产生输出结果信号并将所述输出结果信号映射至量子态空间;

20、在所述量子态空间中,根据量子比特的叠加性和纠缠性,通过量子态比较电路中的受控交换门和干涉测量,将量子态的输出结果信号与所述量子预期结果进行对比,计算两个量子态之间的保真度和距离度量,得到包含当前测试信号的有效性和覆盖率的对比结果;

21、根据所述对比结果,通过自学习优化模块对器件测试模型进行参数调优,以最大化测试覆盖率和最小化测试序列长度为目标,将评估指标作为奖励信号,更新所述器件测试模型,使用更新后的器件测试模型重新生成测试信号序列并反馈至控制器,重复测试直至结果收敛,得到所述最优性能指标。

22、在一种可选的实施方式中,

23、将所述初始测试信号序列通过量子态编码电路映射至量子态空间如下公式所示:

24、;

25、其中,表示编码后的量子态, x为经典测试信号,表示一个 n位的二进制串, n表示经典测试信号的位数,表示计算基态, xk表示测试信号 x的第 k位, i表示取值范围为 0到的所有 n位二进制数, ik表示 i的第 k位,mod 2为模2运算,表示对2取余数。

26、在一种可选的实施方式中,

27、将所述最优性能指标添加至预先设置的智能决策模型中,通过多目标优化算法确定所述最优性能指标与预设标准之间的偏差程度,基于所述偏差程度生成置信度评分并与预先设置的置信度阈值比较,若所述置信度评分高于所述置信度阈值,则标记为合格,否则标记为不合格并自动调整所述器件测试模型中的超参数,动态更新所述置信度阈值直至收敛,若收敛至不合格状态则结合知识图谱进行推理,确定失效模式和改进方案,同时与器件测试信息打包上传至服务器包括:

28、将所述最优性能指标添加至预先设置的智能决策模型中,通过多目标优化算法构建目标函数并确定对应的约束条件,随机生成初始种群,其中,所述初始种群中的每个个体代表一个性能指标,计算每个个体的目标函数值并进行非支配排序和拥挤度计算,得到每个个体对应的等级和密度信息,通过遗传操作生成子代种群,合并初始种群和子代种群并重复非支配排序,生成帕累托前沿并根据非支配排序得到每个指标与预设标准之间的偏差程度;

29、基于所述偏差程度,对于每个测试指标,通过计算实际值与目标值的相对偏差生成指标置信度,综合所述指标置信度,得到所述置信度评分,将所述置信度评分与预设的置信度阈值比较,若所述置信度评分高于所述置信度阈值,则将当前待测集成电路标记为合格,否则标记为不合格,根据测试场景自适应调整所述器件测试模型中的超参数并根据所述置信度评分调整所述置信度阈值,重复测试直至测试结果收敛,若所述测试结果收敛至合格,则上传合格报告;

30、若所述测试结果收敛至不合格,则对于标记为不合格的待测集成电路,提取测试指标异常信息并映射至集成电路测试知识图谱中作为器件测试信息,通过语义推理进行检索,得到所述失效模式,根据失效模式,对因果路径进行检索,结合测试场景筛选改进措施并生成改进方案,将所述器件测试信息、失效模式以及所述改进方案打包上传至服务器。

31、在一种可选的实施方式中,

32、基于所述偏差程度,对于每个测试指标,通过计算实际值与目标值的相对偏差生成指标置信度如下公式所示:

33、;

34、其中, confg( t)表示指标 g在当前时刻 t的指标置信度, λg表示基准值调节参数, αg表示历史偏差累积效应参数, kg表示非线性影响参数, βg表示权重衰减速率参数, wg( j)表示第 g个指标在历史时刻 j的动态权重, devg( j)表示第 g个指标在历史时刻 j的相对偏差, devg( t)表示第 g个指标在当前时刻 t的相对偏差, exp()表示指数函数。

35、本发明实施例的第二方面,提供一种方便线路连接的集成电路测试系统,包括:

36、第一单元,用于获取至少包含两个引脚的待测集成电路,根据所述待测集成电路设置测试电路板,在所述测试电路板上设置所述待测集成电路中引脚对应的测试点以及柔性互连阵列,调节所述柔性互连阵列对应的电纤维束并进行自适应对准连接,通过所述测试电路板中的量子计算单元获取待测器件信息并解密,得到待测电路信息;

37、第二单元,用于将所述待测电路信息发送至神经网络单元并结合多任务迁移学习算法,根据所述待测电路信息,结合预训练的器件测试模型生成初始测试信号序列以及对应的预期结果信号,并映射至量子态空间生成量子测试信号序列以及对应的量子预期结果,通过所述柔性互连阵列将所述量子测试信号序列添加到待测集成电路的测试点上进行信号输入,生成输出结果信号并映射至量子态空间,结合量子态比特计算方法与量子预期结果进行对比,根据对比结果通过量子增强学习方法计算性能指标并添加至自学习优化模块,根据所述对比结果对所述器件测试模型进行参数调整和量子电路结构优化,生成优化测试信号序列并反馈至控制器,重复测试直至结果收敛,得到最优性能指标;

38、第三单元,用于将所述最优性能指标添加至预先设置的智能决策模型中,通过多目标优化算法确定所述最优性能指标与预设标准之间的偏差程度,基于所述偏差程度生成置信度评分并与预先设置的置信度阈值比较,若所述置信度评分高于所述置信度阈值,则标记为合格,否则标记为不合格并自动调整所述器件测试模型中的超参数,动态更新所述置信度阈值直至收敛,若收敛至不合格状态则结合知识图谱进行推理,确定失效模式和改进方案,同时与器件测试信息打包上传至服务器。

39、本发明实施例的第三方面,

40、提供一种电子设备,包括:

41、处理器;

42、用于存储处理器可执行指令的存储器;

43、其中,所述处理器被配置为调用所述存储器存储的指令,以执行前述所述的方法。

44、本发明实施例的第四方面,

45、提供一种计算机可读存储介质,其上存储有计算机程序指令,所述计算机程序指令被处理器执行时实现前述所述的方法。

46、本发明中,通过量子增强的信号生成方式,充分利用了量子计算的并行性和高维度特性,提高了测试信号的多样性和覆盖性,增强了测试的有效性,通过柔性互连阵列将量子测试信号序列添加到待测集成电路的测试点,并将输出结果信号映射至量子态空间,能够根据测试结果动态优化测试策略,提高测试的准确性和效率,智能决策与置信度评估机制,提供了量化的测试结果评价,增强了测试的可解释性和可信度,对于标记为不合格的待测集成电路,结合知识图谱进行推理,确定失效模式和改进方案,提高了问题定位的准确性和效率,为测试工程师提供智能化的决策支持,综上,本发明为集成电路测试领域提供了一种全新的解决方案,有望推动集成电路测试技术的革新和发展,为保障集成电路的可靠性和质量做出重要贡献。

本文地址:https://www.jishuxx.com/zhuanli/20240730/155361.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。