一种隔离型高速输出接口电路的物理实现方法与流程

- 国知局

- 2024-07-31 18:06:07

本发明属于集成电路版图领域,具体涉及一种隔离型高速输出接口电路的物理实现方法。

背景技术:

1、目前,对于集成电路的高速输出接口电路的版图设计,通常采用工艺厂提供的mos管器件,外围添加一圈环用作衬底连接的方式实现。这样的设计具有版图面积小,寄生电容小的优点。但这部分器件直接连接输出pad,在esd发生时,如果esd保护器件没能及时起作用,那么pad处的大电压就会传导到输出接口电路,有可能造成器件dg/ds击穿,甚至可能引发闩锁效应,导致输出接口电路器件损伤。

技术实现思路

1、为了解决现有技术的设计不足,很有必要增加隔离型的设计,用于避免闩锁效应的发生,降低噪声影响,保护芯片内部电路。因此,本发明提供了一种隔离型高速输出接口电路的物理实现方法,在有效实现高速输出接口电路功能的基础上,同时可保持良好的隔离性,降低噪声影响,具有散热好,保护芯片内部电路,增加设计可靠性,可提高器件对称匹配性及增加高速输出接口电路esd防护能力的优点。

2、本发明的技术方案是:本发明为一种隔离型高速输出接口电路的物理实现方法,其特殊之处在于:该方法包括以下步骤:

3、1)高速输出mos管的最小根单元设计;

4、1.1)在高速输出接口电路中,直连pad的输出端分为mos管的d端和s端两种;输出mos管设计为一端宽,一端窄;为保障宽度在内,窄端在两侧的布局,最小根单元的建立以finger=2为准,高速输出接口电路中所有的mos管finger必须为双数;

5、1.2)以满足高速输出接口电路中同类器件(n型或p型)的过电流要求为基础,s端和d端找到最小公共根,拆分为最小根单元,器件输出端的宽度为另一端宽度的4-5倍;同类器件使用最小公共根可以简化设计,达到最少设计一种,最多设计两种最小根单元,即能覆盖高速输出接口电路的全部设计需求;

6、1.3)保持ct孔设计为在d端及s端的正中间一竖列,调整poly到宽端ct孔的间距为poly到窄端ct孔的间距宽度的4-5倍,ct孔过电流能力预留20%-30%;

7、1.4)active上的这一列ct孔,间距要完全一致,用来保持均匀性;在上下靠近active边界的区域,均去除4-5个孔,从而拉大孔到active边界的距离,放大到衬底接触的间距;

8、1.5)根据具体工艺选用的所有金属层叠放在一起布局,使金属的寄生电阻相同,避免开启不均匀;这里窄端metal允许超出窄端active设计;

9、1.6)金属层之间的连接孔均匀分布在金属区域内,个数的设置应大于符合具体工艺孔的过电流能力的10%-20%,多层孔完全重复叠加分布;

10、1.7)将覆盖在d端和s端的金属块每个直角切成两个135度的角,用来避免尖角放电;

11、1.8)mos管的g端上下均打两个孔,使用metal1完成连接;

12、2)高速输出接口电路的隔离与组合设计;

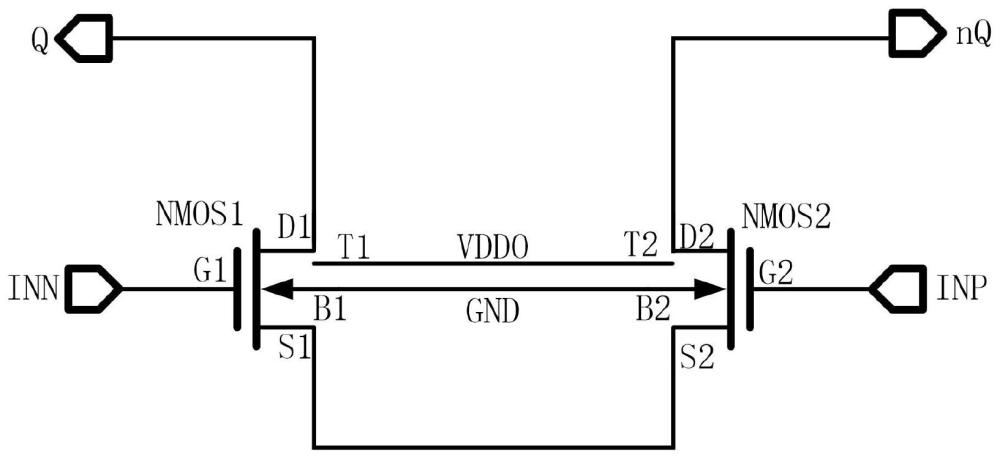

13、2.1)以高速输出mos管的最小根单元为底层模块,根据具体高速输出接口电路,将衬底电位相同,一端接输出,另一端共用的同类型mos管布局在一个隔离区内,在保障隔离的同时增强匹配性,减小面积;

14、2.2)在隔离区内层次化调用最小根单元,匹配具体电路器件finger数,g端采用metal1围环的方式连接;

15、2.3)根据高速输出接口电路的类型,进行物理设计。

16、进一步的,步骤1)的输出信号连接的mos管器件存在p管和n管,p管和n管均要通过该方法步骤独立设计。

17、进一步的,步骤2.3)中高速输出接口电路为n型时,nmos管先围p+的环做b端连接,保持衬底接触最近且充分;再把该器件全部设计放入dnwell内,外圈做dnwell的n+接触,接高电位;最外圈围接地的p+环加强隔离效果。

18、进一步的,步骤2.3)中高速输出接口电路为p型时,将pmos管放在nwell里,先围n+的环做b端连接,再从里向外围两圈隔离环:一圈p+的环接地,一圈n+的环接电源;

19、进一步的,步骤2.3)中高速输出接口电路为np组合型时,输出的nmos管摆在最外缘,pmos管摆在内;nmos管先围p+的环做b端连接,再把该器件设计全部放入dnwell内,外圈做dnwell的n+接触,接高电位;pmos管放在nwell里,先围n+的环做b端连接,再围p+的环接地;nmos管和pmos管在拉开距离的基础上,之间再加入接地的p+环隔离。

20、进一步的,步骤2.3)的环均要打两排孔,里边两圈环上的金属线适当加宽,拐角处切小角,两层环间距满足esd设计规则,避免latch-up效应。

21、进一步的,步骤2.3)之后还包括步骤2.4)n型、p型或np组合型三种接口电路中每个隔离区的器件,从里向外都至少围了三圈环,版图设计通过drc、lvs、erc、esd、latch-up、pex的检查,即完成了一种隔离型高速输出接口电路的物理实现。本发明提供的一种隔离型高速输出接口电路的物理实现方法,先将高速输出接口电路中的mos管以n型、p型划分为finger=2的最小根单元;再根据连接方式将衬底电位相同,一端接输出,另一端共用的同类型mos管合并在同一个隔离区,完成器件布局;最后对n型、p型、np组合型三种接口电路完成物理隔离及电路连接。这种输出管采用最小根单元,合并阱区,三圈环隔离的设计方法,在有效实现高速输出接口电路功能的基础上,同时可保持良好的隔离性,降低噪声影响,具有散热好,保护芯片内部电路,增加设计可靠性,可提高器件对称匹配性及增加高速输出接口电路esd防护能力的优点。

技术特征:1.一种隔离型高速输出接口电路的物理实现方法,其特征在于:该方法包括以下步骤:

2.根据权利要求1所述的隔离型高速输出接口电路的物理实现方法,其特征在于:所述步骤1)的输出信号连接的mos管器件存在p管和n管,p管和n管均要通过该方法步骤独立设计。

3.根据权利要求2所述的隔离型高速输出接口电路的物理实现方法,其特征在于:所述步骤2.3)中高速输出接口电路为n型时,nmos管先围p+的环做b端连接,保持衬底接触最近且充分;再把该器件全部设计放入dnwell内,外圈做dnwell的n+接触,接高电位;最外圈围接地的p+环加强隔离效果。

4.根据权利要求2所述的隔离型高速输出接口电路的物理实现方法,其特征在于:所述步骤2.3)中高速输出接口电路为p型时,将pmos管放在nwell里,先围n+的环做b端连接,再从里向外围两圈隔离环:一圈p+的环接地,一圈n+的环接电源。

5.根据权利要求2所述的隔离型高速输出接口电路的物理实现方法,其特征在于:所述步骤2.3)中高速输出接口电路为np组合型时,输出的nmos管摆在最外缘,pmos管摆在内;nmos管先围p+的环做b端连接,再把该器件设计全部放入dnwell内,外圈做dnwell的n+接触,接高电位;pmos管放在nwell里,先围n+的环做b端连接,再围p+的环接地;nmos管和pmos管在拉开距离的基础上,之间再加入接地的p+环隔离。

6.根据权利要求3至5任一权利要求所述的隔离型高速输出接口电路的物理实现方法,其特征在于:所述步骤2.3)的环均要打两排孔,里边两圈环上的金属线适当加宽,拐角处切小角,两层环间距满足esd设计规则。

7.根据权利要求6所述的隔离型高速输出接口电路的物理实现方法,其特征在于:所述步骤2.3)之后还包括步骤2.4)n型、p型或np组合型三种接口电路中每个隔离区的器件,从里向外都至少围了三圈环,版图设计通过drc、lvs、erc、esd、latch-up、pex的检查,即完成了一种隔离型高速输出接口电路的物理实现。

技术总结本发明涉及一种隔离型高速输出接口电路的物理实现方法,本发明包括以下步骤:1)高速输出MOS管的最小根单元设计;2)高速输出接口电路的隔离与组合设计。本发明在有效实现高速输出接口电路功能的基础上,同时可保持良好的隔离性,降低噪声影响,具有散热好,保护芯片内部电路,增加设计可靠性,可提高器件对称匹配性及增加高速输出接口电路ESD防护能力的优点。技术研发人员:邓广真,邵刚,刘颖,晏雨昕,吕俊盛,门萌萌受保护的技术使用者:西安翔腾微电子科技有限公司技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/177908.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表