增强型薄膜器件的制作方法

- 国知局

- 2024-07-31 18:10:57

本发明总体上涉及硅晶圆的表面处理以及用于将iii-v材料异质集成到硅上的器件。

背景技术:

1、根据摩尔定律,可以安装在芯片上的晶体管的数量预期将呈指数地增加,其中,晶体管的数量增加一倍的速率是每24个月。然而,当电子器件按比例缩小至纳米级时,这产生了问题。自20世纪70年代初以来,电子器件的尺寸不断缩小。通过晶体管的微型化,性能/成本比提高了,这使得半导体市场呈指数增长。这也引起了对半导体技术的持续投资,从而推动了电子器件的进一步微型化。为了继续提高性能,半导体行业现在面临着取代硅基cmos的挑战。硅晶体管的减少将达到其极限。

2、硅基场效应晶体管(mosfet)的独特特征在于其性能随着尺寸的减小而提高。由于通过开发工艺方法减小了场效应晶体管的大小,因此性能随晶体管密度呈指数提高。现代逻辑电路基于具有互补特性的晶体管。这些晶体管被称为n型和p型mosfet(或简称为nmos和pmos晶体管)。微型化的原理是电极以及n沟道和p沟道的长度越来越短。pmos和nmos晶体管一起用于cmos电路,这使得迄今为止制造非常密集的集成电路成为可能。

3、近来,由于散热约为100w/cm2,因此mosfet缩放处于功率限制缩放阶段。在没有大的封装和冷却成本的情况下,功率密度就无法有明显更高的提高,这使得这些芯片对于大多数应用是不切实际的。主要是硅形成自然氧化物的能力使其在集成电路中特别有用,但是对于化合物半导体,对高介电常数氧化物加以评估。特别地,因此,cmos晶体管的几何收缩使当今的计算机成为可能。为了继续电子器件的发展,需要新的解决方案在廉价的硅晶圆上实施新型半导体材料。

4、人们将注意力转移到适合提高cmos晶体管的性能的材料族(所谓的iii-v族半导体)上。这些半导体由元素周期表中的第iii组和第v组元素组合而成,并且是具有吸引力的半导体材料,因为它们的电子特性比硅好很多倍。半导体材料锗和石墨烯作为生产电子部件的替代材料也具有吸引力。这些材料出色的电子传输特性绝对是纳米电子学发展的核心。比如gaas、inas、inp等iii-v族半导体及其三元和四元合金组合了周期表第iii和v列中的元素。对于具有竞争力的iii-v cmos技术,这种材料必须制造在与si-cmos非常相似的硅平台上,该技术需要在硅上将iii-v族半导体与锗或单独的iii-v族半导体共集成。然而,在硅衬底上生产高质量沟道材料非常具有挑战性,尤其是对于iii-v族半导体而言。未来cmos的主要候选者是今天的iii-v cmos技术,以继续制造集成电路。国际半导体技术路线图(itrs)中描述了其对未来cmos技术的未来作用。通常预期在10-14nm节点附近,将需要替代沟道材料来实现国际半导体技术路线图(itrs)中阐述的性能目标。

5、然而,由于其特性是在气相化学工艺的电子器件的不同异质结构中以不同的带隙外延生长的,因此,将iii-v材料组合为合金的可能性备受关注。iii-v材料可以通过气相沉积由iii元素和v元素热降解的前体分子外延地生产。然而,材料不能仅在任何表面上生长,而必须具有带有相同或相似晶格常数的材料的结晶表面,以实现高结晶质量。algainas合金的异质结构是例如是ingaas/gaas/ingaas,而gan/ingan/gan结构分别形成量子阱,从而使光子部件的电荷载流子(电子和空穴)重组。因此,光子应用(比如激光器和led)对iii-v族半导体非常关注,而且还因为iii-v材料的直接带隙。这些半导体材料还由于其高频率电子器件的非常高的迁移率、一维纳米结构中的弹道电子传输、量子电子器件中0和1维纳米结构中的电荷载流子捕获而在制造半导体部件中引起关注。一些iii-v族半导体对于负电荷载流子(例如铟锑)具有非常高的迁移率,而其他半导体(例如锗)对于正电荷载流子具有非常高的迁移率。iii-v族半导体材料实现了可以集成在硅晶圆上的光子应用。石墨烯的电子迁移率是200,000cm2v-1s-1,对于硅而言,约为1400cm2v-1s-1,而对于锑化铟而言,约为77,000cm2v-1s-1。石墨烯的电子迁移率高,但空穴迁移率差,因此不适合cmos电子器件。对于cmos电子器件,高电子迁移率是不够的,但是对于电子迁移率而言,具有1900cm2v-1s-1的锗紧随其后是具有850cm2v-1s-1的insb,锗对于p和n掺杂沟道材料的正电荷载流子具有最大的迁移率。因此,为了实现iii-vcmos需要克服的最重要问题之一是在硅平台上的异构集成。

6、为了使iii-v化合物半导体作为集成电路的半导体成为替代技术,需要对应的驱动器,如si cmos。iii-v mosfet的工艺流程需要使用与硅基cmos技术类似的工艺流程。此外,对于直径为8-12”的工业用晶圆,需要将不同的iii-v族半导体共集成。以前,已经在硅上演示了单个iii-v化合物半导体。即使使用厚缓冲层来演示部件,商业上共集成也需要小于400nm的薄缓冲层。

7、文件“j.a.del alamo等人,iii-v cmos:the key to sub-10nm electronics?[低于10nm电子器件的关键是什么?],麻省理工学院微系统技术实验室,2011年mrs春季会议和展览研讨会p:interface engineering for post-cmos emergingchannel materials[后cmos新兴沟道材料的接口工程]”描述了cmos的功率密度在~100w/cm2时饱和。时钟频率在4ghz时饱和。该文件进一步描述了在大的晶圆区域(比如具有薄缓冲层和低缺陷密度的硅晶圆)上共集成iii-v异质结构的挑战。特别地,该文件描述了两个不同的薄膜结构岛并排地共集成的问题。对此的关键因素之一是材料具有完全不同的晶格常数。

8、文件“j.a.del alamo等人,“the prospects for 10nm iii-v cmos[10nm iii-vcmos的前景]”,麻省理工学院微系统技术实验室,rm.39-567,剑桥,ma02139,usa”描述了取决于p沟道的候选材料,其本身的挑战是需要将两种不同的材料非常紧密地并排集成在硅晶圆上。

9、文件“international technology r oadmap for s emiconductors 2009editionemerging research materials[国际半导体技术路线图2009版新兴研究材料]”中描述的问题是将硅以外的其他半导体用作电子迁移率低但空穴迁移率低的iii-v族半导体。锗具有高空穴迁移率,但电子迁移率不如iii-v化合物半导体的高。另一个问题是为具有不同沟道材料的晶体管实现高迁移率n沟道和p沟道,这些沟道材料被共集成以利用各自的电荷载流子迁移率。另一个问题是在可控位置和方向在硅晶圆上的期望位置处选择性生长替代晶体管沟道材料。

10、文件“international technology r oadmap for s emiconductors 2011editionemerging research materials[国际半导体技术路线图2011版新兴研究材料]”描述了为2018年至2026年预计的2011年挑战。特别关注的是发明一种可以替代常规cmos技术的新cmos技术。根据摩尔定律和itrs,预期晶体管将收缩至2017年的10nm、2019年的7nm、2020年的5nm和2023年的3nm。特别地,该文件描述了将iii-v族半导体与锗共集成用于cmos的问题具有挑战性,但即使集成,挑战也将甚至更加复杂,因为还需要缺陷控制和掺杂控制。另外,iii-v材料的掺杂活化可以在低温发生,而锗的掺杂原子的活化则需要高工艺温度才能进行n掺杂。这两个相互矛盾的要求可能要求在iii-v材料生长之前生产锗部件,这进一步增加了iii-v材料和锗的集成复杂性。

11、特别地,该文件描述了将iii-v族半导体与锗共集成用于cmos的问题具有挑战性,但即使集成,挑战也将甚至更加复杂,因为还需要缺陷控制和掺杂控制。另外,iii-v材料的掺杂活化可以在低温发生,而锗的掺杂原子的活化则需要高工艺温度进行n掺杂。这两个相互矛盾的要求可能要求在iii-v材料生长之前生产锗部件,这进一步增加了iii-v材料和锗的集成复杂性。

12、博士论文“high-performance iii-v pmosfet[高性能iii-v pmosfet],a.nainani,2011”描述了由于硅cmos技术的微型化产生了边际收益,因此,长期以来一直在探索iii-v材料用作低压下高性能晶体管部件的晶体管沟道。该文件描述了后硅cmos的iii-v场效应晶体管的最大挑战是iii-v材料与硅平台的异质集成。另一个挑战是将锗作为p型mosfet沟道的p型部件与基于n型iii-v的mosfet集成。

13、文件“j.a.del alamo等人,“nanometre-scale electronics with iii-vcompoundsemiconductors[具有iii-v化合物半导体的纳米级电子器件]”,自然479.7373(2011):317-323”描述了后sicmos的最大挑战是制备衬底,使得可以并排制造nmos和pmos晶体管。该文件特别描述了为了实现iii-v cmos必须解决的问题是将nmos和pmos晶体管集成在硅上。最重要的是,可能需要的最大进步是将iii-v nmos和pmos晶体管并排集成在硅衬底上。技术预算决定了使用硅晶圆主要是为了实现摩尔定律的成本结构。出于经济原因,需要缓冲层是薄的,并且外延生长时间短,而且还由于散热的热原因。iii-v半导体及其合金的外延层的生长速率为约1-2μm/h。硅上的iii-v族半导体的缓冲层的厚度为约1.5μm。iii-v cmos的最大挑战是制造用于nmos和pmos晶体管的混合衬底,其中具有不同晶格常数的两种不同材料的岛并排放置,以提供平坦的表面。该文件指出,这是没有给予足够重视的关键问题。

14、为了生产更便宜的氮化镓衬底,到目前为止,已经在硅上制造了缓冲层,在缓冲层上,薄膜生长有合金,从氮化铝到氮化镓具有用半导体材料梯度。即,为了通过用由通常为1-5nm薄的ingan薄层限定的2维电子气形成平面gan/ingan/gan量子阱来在氮化镓材料中形成电气部件、特别是平面led。iii-v族半导体的晶格常数使得难以在硅上制造iii-v材料的薄膜而在较大晶圆上制造期间不破裂。

15、硅cmos技术的进一步发展是所谓的硅finfet技术,该技术使用各向异性蚀刻的硅半导体,在源极和漏极之间具有多栅极接触。平面cmos缩放的困难在于维持通过晶体管的电流的可接受的栅极控制。fincmosfet的优势在于,非常容易对水平长形结构涂上触点,对通过晶体管的电流进行有利的静电控制。然而,finfet的一个问题是由于半导体狭窄引起的高电阻。另外,对于10nm以下的晶体管节点,finfet技术受到自上而下的工艺方法的限制。

16、除了其非常好的电子特性外,比如iii-v族半导体和石墨烯等材料还难以制造在大型硅晶圆上。对于iii-v族半导体,这尤其是由于以下事实:这些半导体是晶格失配半导体,即,它们在原子的结晶晶格中的晶格常数与硅明显不同。这导致在硅晶圆中形成应力,该应力导致硅晶圆弯曲和微小变弯。在硅上涂上纯氮化镓(晶格失配半导体)容易导致硅晶圆破裂。上述对硅涂上氮化镓的方法是在对硅晶圆涂上大量氮化铝镓合金的复杂工艺中生长缓冲层,该工艺用各种掺杂和氮化铝镓合金均匀地消除了缓冲层中的应力。该工艺难以扩展到大批量各种不同的硅晶圆,特别是需要针对每个设备和硅晶圆进行优化。另外,氮化铝镓中的大量合金外延层导致过程时间长,这对于大规模生产而言成本非常高。

17、led制造商在蓝宝石衬底上生长iii族氮化物半导体,这非常昂贵,6英寸晶圆约400美元,而硅电子器件制造商面临着转换为iii-v材料以增强集成电路性能的挑战,当今将需要厚度为200-300微米的固体iii-v族半导体的半导体晶圆。根据国际半导体技术路线图(itrs),对于半导体工业中需要比2”iii-v族半导体更大的盘,目前尚不存在轻易可用的产品。

18、减轻上述问题的一种方式是使用iii-v材料的横向过生长。尤其在专利us20100072513a1中描述了这种解决方案,其中,半导体材料涂在结晶衬底上,第一半导体材料和掩模设置在结晶衬底表面上。半导体材料包括具有填充开口并覆盖掩模以减少位错的第二半导体材料的结晶过生长。这种解决方案的缺点在于,iii-v材料如此脆,以至于同一结晶衬底上的两种不同晶格失配半导体材料或iii-v材料与锗或其他具有相同晶格常数的材料的组合会导致晶圆破裂,尤其是对于较大的晶圆直径(比如4-12英寸)。

19、文件us 7250359 b2描述了在将锗集成在硅上时如何在晶圆中引入张力。该文件进一步披露了一种通过在硅上蚀刻v形凹痕然后在硅上外延晶格失配生长iii-v材料来在硅上生长iii-v材料的方法。目的是由于材料中的应力而限制gan衬底的大小。gan膜的厚度还可以为从基于gan的光学部件发射的光提供波长偏移。破裂通常发生在gan外延层中,并在晶体结构中产生应力和应变。该方法的缺点是晶格失配导致在材料中仍有许多应力,结果导致限制了旨在用于晶格失配的半导体的外延衬底的大小。

20、文件us 9379204 b2描述了iii-v材料的晶圆如何被蚀刻并且被重新填充iii-v材料以提供无位错的iii-v族半导体。此方法的缺点是晶格失配造成材料中仍有很多张力。另外,晶圆的机械性能不足以用于共集成非常多样化的iii-v材料的目的,这些材料在大于2英寸的大区域上对晶圆提供不同的应力。

21、在文件us20140264607 a1中描述了一种在硅衬底上形成具有相关联的iii-v族材料的finfet部件的方式。根据此解决方案,非硅基半导体在具有长度厚度比的沟槽中生长,以在失配的沟槽晶格中形成半导体材料。还描述了如何掺杂半导体鳍的不同部分以形成与半导体鳍的源极和漏极接触。此方法的缺点在于,当半导体鳍在硅衬底上生长得晶格失配时,晶圆的脆性仍然存在。一个主要问题是,iii-v族半导体的晶格常数使得难以在硅上制造iii-v材料的薄膜而在较大的晶圆衬底上制造期间不会破裂。特别地,位错可能传播到半导体鳍。

22、文件wang等人、small,13,2017,1700929描述了锗外延层如何可以催化地用于使石墨烯与cvd合成。将200nm厚的锗膜溅射到具有300nm siox氧化物层的高掺杂p-si晶圆上。特别地,期望形成石墨烯以避免金属污染。在真空下,引入23sccm氢气和230sccm氩气的混合物直至大气压。在不改变气体流量的情况下,将锗外延层加热到接近其900-930摄氏度的熔点。将0.7sccm甲烷气体添加到反应器中60-360分钟。用于生产用于催化石墨烯生长的锗层的这种方法的缺点在于,锗层被溅射并且具有石墨烯的量子电子部件的结晶质量低。

23、总之,已知的在硅上制造iii-v材料和其他材料的方法存在问题。一个问题是,采用已知的缓冲层技术,大于6”的硅晶圆上的iii-v薄膜缺陷阻止在用于电子部件的硅上的iii-v族半导体上生产50-100nm薄的薄膜缓冲层。

24、另一个问题是硅上的厚iii-v薄膜可以在有限程度上改善晶体质量,但导致光子学中的其他问题:硅上的厚缓冲层导致的波长偏移以及iii-v cmos的功率密度导致的散热不佳,这些问题则可以用硅上具有iii-v族半导体的更薄外延层进行补救。

技术实现思路

1、因此,本发明的实施例优选地试图通过提供根据所附专利权利要求所述的增强型薄膜来缓解、减轻或消除本领域中的比如以上单独或以任何组合确认的一个或多个缺陷、缺点或问题。

2、应强调的是,当在本说明书中使用时,术语“包括(comprises/comprising)”被用于指定所陈述的特征、整体、步骤或部件的存在,但不排除存在或添加一个或多个其他特征、整体、步骤、部件或其群组。

3、本发明的目的是提供增强型晶圆,这些晶圆具有比目前通过之前的方法可以制造的高迁移率半导体材料的尺寸大于4英寸或具有用于电子部件的缓冲层的晶圆更高的供外延生长的结晶质量。

4、本发明的另一个目的是提供一种硅晶圆,该硅晶圆不会由于引起当前硅晶圆弯曲的iii-v族半导体材料生长而破裂。对于工业应用,还要求晶圆与机器人搬运相容,使得机械臂(通过真空吸力进入晶圆下方)可以将晶圆移入和移出如用于6-12英寸晶圆的设备中正在使用的工艺室。这将使仅基于比在硅中的迁移率更高的电荷载流子迁移率的高性能电子部件的制造更廉价,而硅晶圆可以在许多为比如2英寸、4英寸、6英寸、8英寸和12英寸晶圆的工业规模晶圆的特定尺寸而设计的工艺中用作平台。还将允许在用于后硅cmos部件的集成电路以及硅晶圆上集成的纳米电子器件和光子器件的外延制造中具有很高的精度。

5、本发明的另一个目的是提供一种晶圆,作为在本文所述的硅晶圆上构造量子计算器件的方式。

6、上述目的是通过根据所附独立权利要求所述的薄膜器件来实现的,其中在从属权利要求中描述了特定实施例。因此,本发明目的在于提供一种高强度的薄膜,该薄膜可以代替大的iii-v族半导体晶圆,由此能够在控制下在硅上生长iii-v族半导体外延层(或石墨烯)以制造功能性电子部件。

7、本发明的另一个目的是将各种高迁移率半导体集成用于后硅cmos部件的硅平台上。这种共集成在文献中被认为极具挑战性,并且被认为是iii-v cmos的主要挑战。本发明的另一个目的是提供一种用于将外延层作为不同半导体材料的岛并排定位在晶圆上并控制其用于vlsi iii-v cmos的大小的方式。为了使iii-v cmos达到国际半导体技术路线图(itrs)中提出的目标,必须将两种具有不同晶格常数的不同半导体材料的岛共集成在硅晶圆上。另外,本发明的目的是提供一种用于10nm以下的晶体管节点的硅后cmos纳米电子平台的装置,此后利用量子计算机的自上而下的工艺方法来制造变得具有挑战性。

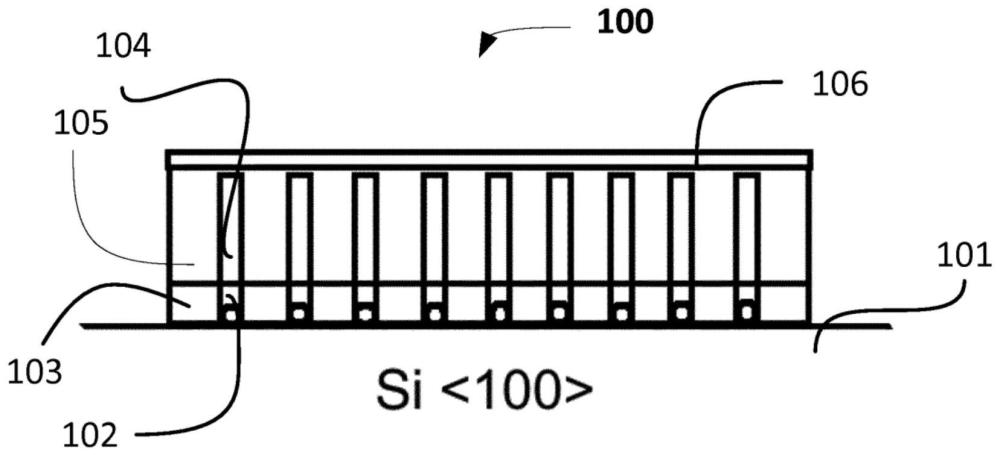

8、本发明的第一方面是一种增强型薄膜器件,其包括:衬底,该衬底具有用于支撑外延层的顶表面;掩模层,该掩模层被图形化有多个纳米级空腔,这些纳米级空腔设置在所述衬底上,以形成针垫;设置在所述掩模层上的晶格失配半导体的薄膜,其中,所述薄膜包括所述晶格失配半导体的嵌入所述薄膜中的多个平行间隔的半导体针,其中,所述多个半导体针沿轴向方向朝所述衬底基本上竖直地设置在所述掩模层的所述多个纳米级空腔中,并且其中,所述薄膜上设置有其支撑的晶格失配半导体外延层;优选地,其中,所述衬底是直径大于2英寸的硅晶圆。从属权利要求中限定了本发明的另外的实施例,其中本发明的第二方面和后续方面的特征是关于第一方面加以必要的修改。

9、简而言之,由薄膜提供的增强件是具有嵌入在薄膜中的半导体针的竖直增强件。与体半导体材料相比,直径为5-10nm的iii-v材料的半导体针具有非常好的强度特性。因此,增强件允许这种半导体针的弹性变形以防止位错扩散。此外,将针如何以密集堆积结构嵌入薄膜中的图形用于增强。

10、增强型薄膜器件的第一优点是,相比硅上常规厚缓冲层的1μm/h生长速度,硅上半导体针的大部分iii-v族半导体生长以高达30μm/h的速度生长。纳米线的短培养时间大大缩短了iii-v族半导体薄膜的总生长时间,并允许100nm以下的薄膜具有比微米厚的缓冲层更高的晶体质量。

11、另一优点是,增强型薄膜器件使直径为6-12英寸的iii-v族半导体晶圆不会因晶格应变而扩散位错。位错扩散受到纳米级紧密堆积的增强件的限制,这可以防止破裂,即硅晶圆可能破碎成几片。而且,对于两个不同的高迁移率p型和n型沟道的同质外延晶体生长,通过由于在薄膜中嵌入了密集堆积的纳米线而可以传播的位错较少,晶体管沟道的晶体质量提高。

12、另一优点是,薄膜可以在硅衬底上生长,其高度大约为十亿分之一米,可以代替相同材料的250-1000μm厚的固态大晶圆。如今,丰富度有限的iii和v前体使用的iii-v族半导体晶圆替代可以从沙子中提取的非常丰富的硅,相比之下,iii和v前体相对稀有。

13、另一个优点是薄膜不需要通过异质外延生长进行生长,或不需要在适当的晶体方向的衬底(比如(111)平面硅晶圆)上生长。

14、另一个优点是可能不需要铝对gan生长的mocvd腔室的污染。

15、另一个优点是,增强型薄膜器件能够在硅上锗衬底上生长石墨烯岛,即以石墨烯作为迄今为止半导体材料中电子迁移率最高的材料。

16、另一个优点是,可以通过薄膜器件的薄外延层有效地消散cmos晶体管中产生的热量。

17、另一个优点是,由于控制了纳米线在硅晶圆上特定位置处的定位,因此可以在增强晶圆上并排生长不同iii-v和锗层的岛,以用于平面nmos和pmos晶体管。

18、另一个优点是可以在iii-v岛生长之前完成锗岛的掺杂物原子的活化。

19、另一个优点是,对于vlsi iii-v/iii-v鳍式cmos tfet,可以控制外延岛的位置及其生长。

20、另一个优点是可以为增强晶圆上的pmos和nmos的p-i-n隧道效应晶体管限定薄的本征外延层。这意味着iii-v finfet的缩放可以用于7nm以下的节点。

21、另一个优点是可以在硅晶圆上制造铟锑外延层,以产生外延生长的纳米结构,用于硅晶圆上的拓扑量子计算机。

本文地址:https://www.jishuxx.com/zhuanli/20240731/178166.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表