一种应用于三维异质异构封装技术的空间电磁耦合抑制结构

- 国知局

- 2024-07-31 18:16:58

本发明涉及三维异质异构射频封装工艺领域,尤其涉及一种封装后腔内电磁耦合抑制结构。

背景技术:

1、在相控阵雷达的发展中,小型化是重要发展方向之一,目前大多数相控阵组件采用表面贴装工艺,集成度相对较低、体积较大。为解决该困难,目前多采用基于半导体工艺的封装集成技术(如三维异构封装),使用通孔或倒装技术实现组件的三维垂直互连,有效解决互连走线寄生影响较大的问题,提高系统集成度,从而实现小型化与高性能化。

2、三维异质异构射频封装腔体内部通常含有毫米波相控阵射频通道芯片,其包括幅相控制电路、低噪声放大器、功率放大器、无源传输线、电感与变压器等有源与无源器件等。腔体本振谐振频率与芯片工作频率接近,在谐振频率处的腔内电磁耦合较强,引起芯片的带内或带外振荡。传统抑制腔内电磁耦合方法为在腔内增加隔离腔,减小腔体尺寸,导致腔体尺寸增大,且不适用隔离单个大尺寸集成芯片。

技术实现思路

1、本发明的目的在于提出一种腔体电磁耦合抑制结构,以解决现有三维异质异构封装腔体内部电磁耦合的问题。

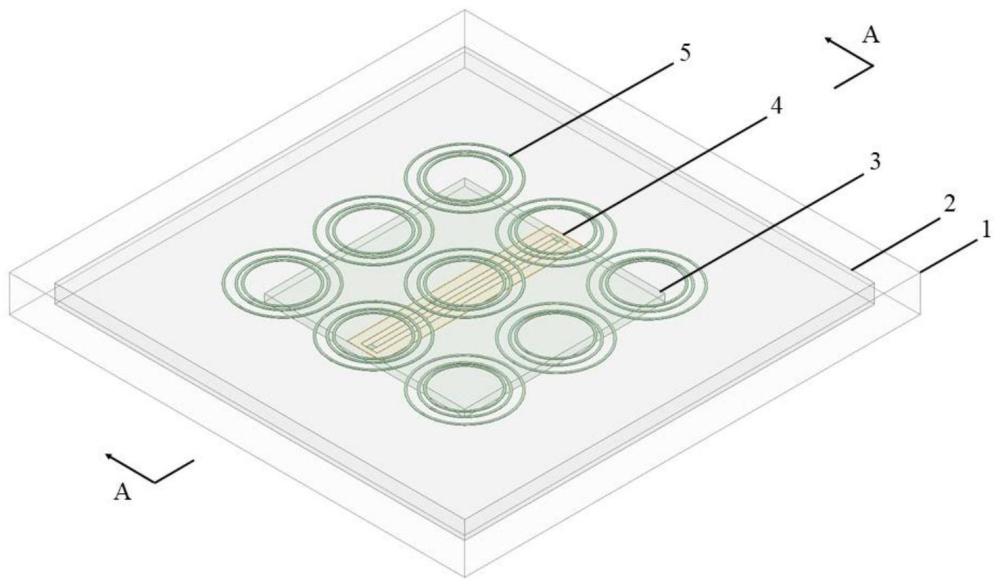

2、实现本发明目的的技术解决方案为:一种应用于三维异质异构封装技术的空间电磁耦合抑制结构,包括封装外壳,所述封装外壳内部存在空腔,所述空腔底部中央内置射频芯片,所述空腔顶部中央设置用于抑制电磁耦合现象的谐振环族矩阵,所述谐振环族矩阵由多个谐振环族以m×n矩阵排列组成,所述谐振环族由多个不同周长的串联有电阻、电感的谐振环同心排布组成。

3、进一步的,所述封装外壳采用硅基/化合物封装外壳。

4、进一步的,所述封装外壳内部空腔为空气腔或真空腔。

5、进一步的,封装外壳尺寸由所需封装的射频芯片决定,外壳下半部分与射频芯片嵌合,或者尺寸大于射频芯片尺寸,当外壳下半部分尺寸大于射频芯片尺寸,将射频芯片置于封装外壳底部中央。

6、进一步的,所述谐振环族中谐振环的谐振频率由环上串联电容c与环自身电感l决定,谐振环的谐振频率由给出,谐振环的电感值与环周长紧密相关,因此环周长确定后,电感l数值就确定了;针对所需抑制的腔体本征频率,通过调整谐振环的周长改变谐振环自身电感大小,从而改变谐振环的谐振频率与所需抑制的腔体的本征频率接近,使环吸收腔体本征谐振散发出的电磁能量;当腔体内存在多个本征频率,根据需要抑制的腔体本征模式数增减环的数量,根据不同模式的本征频率调整环的周长,以达到抑制效果。

7、进一步的,所述谐振环族个数以及谐振环族间距直接影响环族耦合系数,间接改变谐振频率带宽,应使得空腔顶层尽可能被谐振环覆盖,使得谐振环族矩阵的电磁耦合抑制效果在腔内达到最大。

8、进一步的,所述谐振环族个数与谐振环族间距根据抑制频率的带宽要求进行调整,带宽越宽,谐振环族间距更小,每族谐振环更多,考虑到腔体本征谐振频率的离散特征,每族谐振环数目不用过多,依据半导体制造工艺的可实现性确定,谐振环族圆心间距不易超过3倍环半径,依据矩阵环族间的耦合强度确定。

9、进一步的,所述谐振环的厚度小于5μm,所述谐振环的宽度为20μm。

10、进一步的,所述谐振环的形状采用圆环、椭圆环或多边形环。

11、进一步的,所述谐振环采用铝或铜制成。

12、发明与现有技术相比,其显著优点为:由谐振环族组成的腔体电磁耦合抑制结构,在封装内通过在腔体顶部设置带电阻谐振环族矩阵,掩盖多个模式的腔体谐振频率,采用带电阻金属环降低金属谐振环族的q值,实现了封装腔体内谐振抑制,以及腔内嵌射频芯片的超宽带匹配和低插损传输。

技术特征:1.一种应用于三维异质异构封装技术的空间电磁耦合抑制结构,其特征在于,包括封装外壳,所述封装外壳内部存在空腔,所述空腔底部中央内置射频芯片,所述空腔顶部中央设置用于抑制电磁耦合现象的谐振环族矩阵,所述谐振环族矩阵由多个谐振环族以m×n矩阵排列组成,所述谐振环族由多个不同周长的串联有电阻、电感的谐振环同心排布组成。

2.根据权利要求1所述的应用于三维异质异构封装技术的空间电磁耦合抑制结构,其特征在于,所述封装外壳采用硅基/化合物封装外壳。

3.根据权利要求1所述的应用于三维异质异构封装技术的空间电磁耦合抑制结构,其特征在于,所述封装外壳内部空腔为空气腔或真空腔。

4.根据权利要求1所述的应用于三维异质异构封装技术的空间电磁耦合抑制结构,其特征在于,封装外壳尺寸由所需封装的射频芯片决定,外壳下半部分与射频芯片嵌合,或者尺寸大于射频芯片尺寸,当外壳下半部分尺寸大于射频芯片尺寸,将射频芯片置于封装外壳底部中央。

5.根据权利要求1所述的应用于三维异质异构封装技术的空间电磁耦合抑制结构,其特征在于,所述谐振环族中谐振环的谐振频率由环上串联电容c与环自身电感l决定,谐振环的谐振频率由给出,谐振环的电感值与环周长紧密相关,因此环周长确定后,电感l数值就确定了;针对所需抑制的腔体本征频率,通过调整谐振环的周长改变谐振环自身电感大小,从而改变谐振环的谐振频率与所需抑制的腔体的本征频率接近,使环吸收腔体本征谐振散发出的电磁能量;当腔体内存在多个本征频率,根据需要抑制的腔体本征模式数增减环的数量,根据不同模式的本征频率调整环的周长,以达到抑制效果。

6.根据权利要求1所述的应用于三维异质异构封装技术的空间电磁耦合抑制结构,其特征在于,所述谐振环族个数以及谐振环族间距直接影响环族耦合系数,间接改变谐振频率带宽,应使得空腔顶层尽可能被谐振环覆盖,使得谐振环族矩阵的电磁耦合抑制效果在腔内达到最大。

7.根据权利要求6所述的应用于三维异质异构封装技术的空间电磁耦合抑制结构,其特征在于,所述谐振环族个数与谐振环族间距根据抑制频率的带宽要求进行调整,带宽越宽,谐振环族间距更小,每族谐振环更多,考虑到腔体本征谐振频率的离散特征,每族谐振环数目不用过多,依据半导体制造工艺的可实现性确定,谐振环族圆心间距不易超过3倍环半径,依据矩阵环族间的耦合强度确定。

8.根据权利要求1所述的应用于三维异质异构封装技术的空间电磁耦合抑制结构,其特征在于,所述谐振环的厚度小于5μm,所述谐振环的宽度为20μm。

9.根据权利要求1所述的应用于三维异质异构封装技术的空间电磁耦合抑制结构,其特征在于,所述谐振环的形状采用圆环、椭圆环或多边形环。

10.根据权利要求1所述的应用于三维异质异构封装技术的空间电磁耦合抑制结构,其特征在于,所述谐振环采用铝或铜制成。

技术总结本发明公开了一种应用于三维异质异构封装技术的空间电磁耦合抑制结构,包括封装外壳,所述封装外壳内部存在空腔,所述空腔底部中央内置射频芯片,所述空腔顶部中央设置用于抑制电磁耦合现象的谐振环族矩阵,所述谐振环族矩阵由多个谐振环族以M×N矩阵排列组成,所述谐振环族由多个不同周长的串联有电阻、电感的谐振环同心排布组成。本发明由每个环带电阻电感的谐振环族组成矩阵的方式抑制腔体内电磁耦合,抑制腔内电磁耦合的均匀性较好,无需隔离腔、减小封装腔体尺寸。技术研发人员:黄同德,彭恒旭,张皓,陶洪琪,吴文受保护的技术使用者:南京理工大学技术研发日:技术公布日:2024/7/25本文地址:https://www.jishuxx.com/zhuanli/20240731/178603.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表