一种半导体器件及其制造方法

- 国知局

- 2024-07-31 18:20:57

本发明涉及半导体领域,特别涉及一种半导体器件及其制造方法。

背景技术:

1、随着半导体技术的发展,集成电路的特征尺寸持续微缩,传统三栅或双栅的鳍式场效应晶体管(fin field-effect transistor,finfet)在3纳米(nm)以下节点受到限制,由于纳米片环栅晶体管(nanosheet-gate all round fin field-effect transistor,nanosheet-gaafet)突破了3nm节点的限制,因此受到广泛关注和研究。

2、nanosheet-gaafet是一种具有环栅结构和水平纳米片(nanosheet,ns)作为导电沟道的新型器件。在栅极控制方面,环栅结构具有比finfet器件结构更好的栅控能力,可以有效抑制器件的短沟道效应,在电流驱动方面,nanosheet-gaafet具有“体反型”的反型载流子,而且有效栅宽的增加和垂直方向的纳米片堆叠设计也可显著增强器件的电流驱动性能。当前nanosheet-gaafet可以形成不同类型的器件,例如可以形成n型金属-氧化物-半导体(n-metal-oxide-semiconductor,nmos)晶体管,也可以形成p型金属-氧化物-半导体(p-metal-oxide-semiconductor,pmos)晶体管,还可以形成互补金属-氧化物-半导体(complementary-metal-oxide-semiconductor,cmos)晶体管。为了实现这些不同类型的nanosheet-gaafet的阈值控制,需要在形成nanosheet-gaafet的栅极时,首先形成功函数层(wfl),通过控制功函数层的厚度控制nanosheet-gaafet的阈值。

3、但是当前利用功函数层的厚度控制nanosheet-gaafet的阈值存在阈值控制不精确的情况。

技术实现思路

1、有鉴于此,本技术的目的在于提供一种半导体器件及其制造方法,能够利用第一介质层和第二介质层对nanosheet-gaafet进行精确阈值控制,提高器件性能。

2、本技术提供了一种半导体器件,所述半导体器件包括:

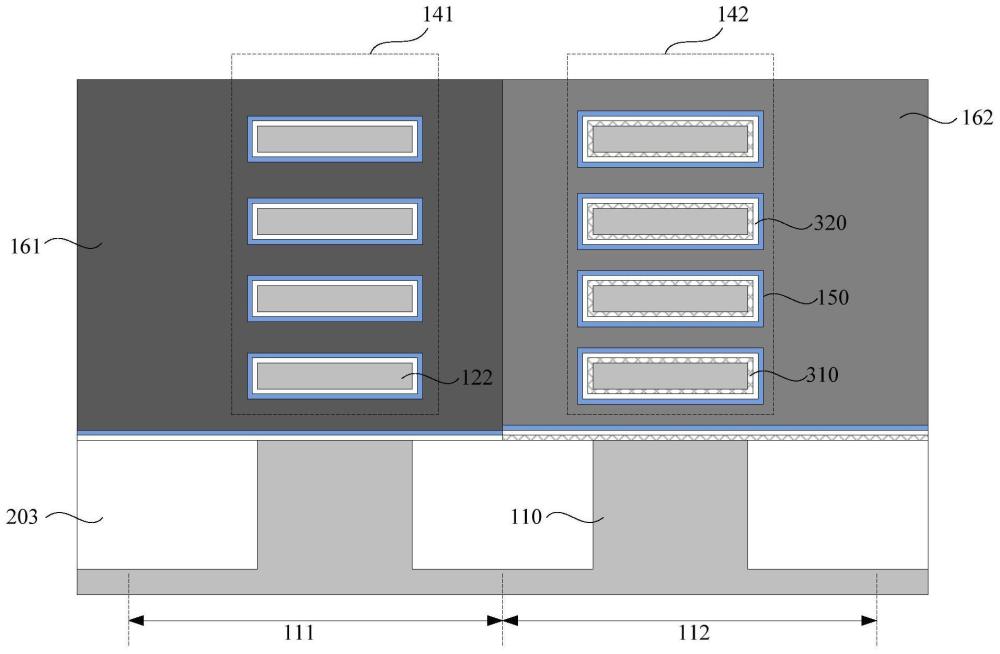

3、衬底,所述衬底包括n型区域和p型区域;

4、在所述衬底一侧的设置于所述n型区域的第一源极、第一漏极和第一沟道结构,在所述衬底一侧的设置于所述p型区域的第二源极、第二漏极和第二沟道结构,所述第一沟道结构包括多个第一纳米片形成的叠层,所述第二沟道结构包括多个第二纳米片形成的叠层;

5、环绕所述第一纳米片和所述第二纳米片中的其中一个的第一介质层以及第二介质层,环绕所述第一纳米片和所述第二纳米片中的另一个的所述第二介质层,所述第一介质层和所述第二介质层材料不同,所述第一介质层和所述第二介质层中的一种为第一类型高k介质层,所述第一介质层和所述第二介质层中的另一种为第二类型高k介质层,所述第一类型高k介质层和所述第二类型高k介质层的静电偶极子方向相反;

6、第一栅极和第二栅极,所述第一栅极环绕所述第一纳米片,所述第二栅极环绕所述第二纳米片。

7、可选地,所述第一类型高k介质层的材料包括稀土氧化物,所述第二类型高k介质层的材料的离子式为mox,所述m满足预设条件。

8、可选地,所述第一类型高k介质层的材料包括laox、mgox、scox、yox、ndox、tbox和dyox中的一种或多种;

9、所述第二类型高k介质层的材料包括alox、mnox、zrox、tiox和moox中的一种或多种。

10、可选地,所述半导体器件包括第三类型高k介质层,所述第三类型高k介质层的材料至少包括铪元素;

11、所述第三类型高k介质层环绕所述第二介质层。

12、可选地,所述第三类型高k介质层的材料包括hfo2、hfsiox、hfon、hfsion、hfalox和hflaox中的一种或多种。

13、可选地,所述第一介质层和所述第二介质层的厚度范围为[0.1nm,5nm]。

14、本技术提供了一种半导体器件的制造方法,所述方法包括:

15、提供衬底,所述衬底包括n型区域和p型区域,在所述衬底的一侧形成由第一半导体层和第二半导体层交替层叠的叠层结构;对所述叠层结构进行刻蚀在所述n型区域形成第一源极区域和第一漏极区域以及在所述p型区域形成第二源极区域和第二漏极区域,所述第一源极区域和所述第一漏极区域之间为第一沟道区域,所述第二源极区域和所述第二漏极区域之间为第二沟道区域;在所述第一源极区域和所述第一漏极区域分别形成第一源极和第一漏极,在所述第二源极区域和所述第二漏极区域分别形成第二源极和第二漏极;

16、去除所述第一沟道区域以及所述第二沟道区域的所述第一半导体层,所述第二半导体层之间形成多个待填充微纳腔体空间;

17、在位于所述n型区域的所述第二半导体层的表面和位于所述p型区域的所述第二半导体层的表面中的其中一个形成第一介质层和第二介质层,位于所述n型区域的所述第二半导体层的表面和位于所述p型区域的所述第二半导体层的表面中的另一个形成所述第二介质层,所述第一介质层和所述第二介质层材料不同,所述第一介质层和所述第二介质层中的一种为第一类型高k介质层,所述第一介质层和所述第二介质层中的另一种为第二类型高k介质层,所述第一类型高k介质层和所述第二类型高k介质层的静电偶极子方向相反;

18、在所述n型区域的待填充微纳腔体空间填充第一栅极,在所述p型区域的待填充微纳腔体空间填充第二栅极,所述第一栅极和第二栅极环绕所述第二半导体层,位于所述n型区域的多个所述第二半导体层构成的叠层形成第一沟道结构,位于所述p型区域的多个所述第二半导体层构成的叠层形成第二沟道结构。

19、可选地,所述在位于所述n型区域的所述第二半导体层的表面和位于所述p型区域的所述第二半导体层的表面中的其中一个形成第一介质层和第二介质层,位于所述n型区域的所述第二半导体层的表面和位于所述p型区域的所述第二半导体层的表面中的另一个形成所述第二介质层包括:

20、在位于所述n型区域的所述第二半导体层的表面以及位于所述p型区域的所述第二半导体层的表面形成第一介质层和第二介质层;

21、在所述n型区域或所述p型区域形成掩膜层;

22、利用选择性工艺去除未被所述掩膜层覆盖的所述第一介质层和所述第二介质层;

23、去除所述掩膜层;

24、在所述n型区域和所述p型区域形成所述第二介质层。

25、可选地,所述方法还包括:

26、在所述第二介质层的表面形成第三类型高k介质层,所述第三类型高k介质层的材料至少包括铪元素。

27、可选地,所述第一栅极包括第一阻挡层、第一功函数层和第一导电层,所述第二栅极包括第二阻挡层、第二功函数层和第二导电层;

28、所述在所述n型区域的待填充微纳腔体空间填充第一栅极,在所述p型区域的待填充微纳腔体空间填充第二栅极包括:

29、在所述n型区域的第三类型高k介质层的表面依次形成所述第一阻挡层、所述第一功函数层和所述第一导电层;

30、在所述p型区域的第三类型高k介质层的表面形成所述第二阻挡层、所述第二功函数层和所述第二导电层。

31、本技术提供了一种半导体器件,半导体器件包括:衬底,衬底包括n型区域和p型区域,相应地,设置在衬底一侧的源极、漏极、栅极和沟道结构也同样的根据n型区域和p型区域分为第一源极和第二源极,第一漏极和第二漏极,第一栅极和第二栅极,第一沟道结构和第二沟道结构,其中,第一沟道结构包括多个第一纳米片形成的叠层,第二沟道结构包括多个第二纳米片形成的叠层,第一栅极环绕第一纳米片,第二栅极环绕第二纳米片,即本技术的半导体器件包括n型半导体器件和p型半导体器件。为了实现对半导体器件的阈值控制,可以在第一纳米片和第二纳米片中的其中一个设置环绕其的第一介质层以及第二介质层,在第一纳米片和第二纳米片中的另一个设置环绕其的第二介质层,也就是说,第一栅极和第一纳米片之间设置有第一介质层和第二介质层以及第二栅极和第二纳米片之间设置有第二介质层或第一栅极和第一纳米片之间设置有第二介质层以及第二栅极和第二纳米片之间设置有第一介质层和第二介质层。第一介质层和第二介质层材料不同,第一介质层和第二介质层中的一种为第一类型高k介质层,第一介质层和第二介质层中的另一种为第二类型高k介质层,其中,第一类型高k介质层和第二类型高k介质层的静电偶极子方向相反,即,第一类型高k介质层和第二类型高k介质层形成的电场方向相反。也就是说,无论第一介质层和第二介质层是哪一种类型的高k介质层,都能够极化产生方向相反的电场/静电偶极子,这样相当于在不同的区域形成方向相反的电场/静电偶极子,从而利用不同区域的方向相反的电场/静电偶极子控制半导体器件的阈值。相较于仅仅利用功函数层对半导体器件的阈值进行控制,利用设置于不同区域的第一介质层和第二介质层叠层结构以及单独的第二介质层辅助半导体器件进行阈值控制更为精确,能够实现阈值的精细以及多级控制,也能够实现阈值的大范围调控,从而提高器件性能。

本文地址:https://www.jishuxx.com/zhuanli/20240731/178844.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表