测试结构、掩膜版版图、及测试方法与流程

- 国知局

- 2024-07-31 18:26:45

本发明实施例涉及半导体制造领域,尤其涉及一种测试结构、掩膜版版图、及测试方法。

背景技术:

1、在半导体器件制作过程中,常常需要对器件的可靠性进行测试。特别是随着半导体工艺技术的发展,半导体器件越来越集成化,半导体器件的尺寸正在逐渐成比例缩小,其关键尺寸(cd,critical dimension)也变得越来越小,对于cd越来越小的半导体器件,在beol(back end of line,后段工艺)中的介质层(inter layer dielectric,ild)也会越来越薄,对beol制造的电路结构的性能进行测试也变得至关重要。

2、本领域中通常采用时间相关介质击穿(time dependent dielectric breakdown,简称tddb)测试来进行可靠性测试。它可以用来预测半导体器件的使用寿命。通常,在金属线上加恒定的电压,使器件处于积累状态,这就是一般所说的tddb。经过一段时间后,介质材料就会被击穿,在金属线上施加恒定电压开始到介质材料被击穿结束的这段期间所经历的时间就是在该条件下的介质材料寿命。

技术实现思路

1、本发明实施解决的问题是提供了一种测试结构、掩膜版版图、及测试方法,提高了测试结构的测试精度。

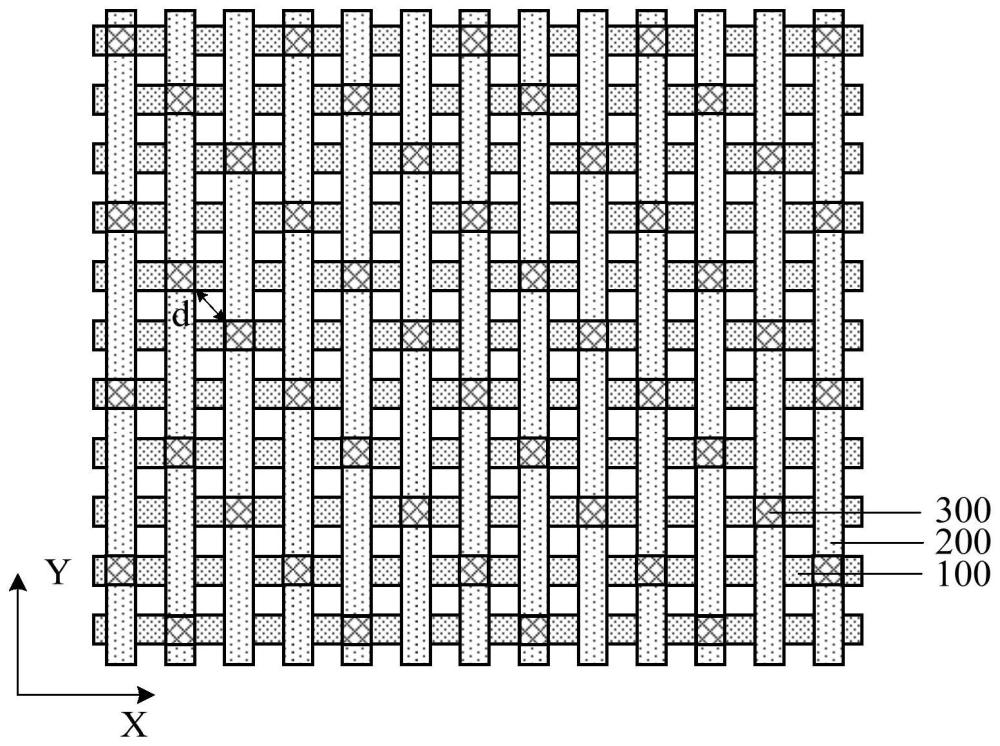

2、为解决上述问题,本发明实施例提供一种测试结构,包括:第一金属层,包括沿第一方向延伸且沿第二方向平行排列的多个第一金属线,沿第二方向,间隔相邻的第一金属线均用于作为第一信号加载端,剩余第一金属线均用于作为第二信号加载端,第二方向和第一方向垂直;位于第一金属层上方的第二金属层,包括沿第二方向延伸且沿第一方向平行排列的多个第二金属线;多个通孔互连结构,位于第一金属层与第二金属层之间,以第一金属线与第二金属线在水平面的投影交叠处作为交叉位置,通孔互连结构位于对角相邻的交叉位置、且与对应的第一金属线和第二金属线电连接。

3、可选的,多个通孔互连结构构成多个相互平行的通孔列,通孔列包括沿对角相邻的交叉位置的对角线排布的多个通孔互连结构。

4、可选的,沿第一方向,相邻通孔互连结构之间具有多个第二金属线;沿第二方向,相邻通孔互连结构之间具有多个第一金属线。

5、可选的,沿第一方向,相邻通孔互连结构之间具有2个第二金属线;沿第二方向,相邻通孔互连结构之间具有2个第一金属线。

6、可选的,测试结构还包括第一介电层、以及位于第一介电层上的第二介电层;第一金属层位于第一介电层中,且沿第二方向,相邻第一金属线之间通过第一介电层相间隔;第二金属层和通孔互连结构位于第二介电层中,且沿第一方向,相邻第二金属线之间通过第二介电层相间隔,相邻通孔互连结构之间通过第二介电层相间隔。

7、可选的,第一介电层的材料包括sioc、sioch、sic、sicn、sio2、sin和sion中的一种或多种;第二介电层的材料包括sioc、sioch、sic、sicn、sio2、sin和sion中的一种或多种。

8、可选的,第二金属线、以及与第二金属线电连接的通孔互连结构为一体结构。

9、可选的,相邻第一金属线之间的间隔相等;相邻第二金属线之间的间隔相等。

10、可选的,第一金属线的材料包括铜、铝和铜合金中的一种或多种;第二金属线的材料包括铜、铝和铜合金中的一种或多种;通孔互连结构的材料包括铜、铝和铜合金中的一种或多种。

11、可选的,第一信号加载端和第二信号加载端中的任一个用于加载高电位,另一个用于加载低电位。

12、相应的,本发明实施例还提供一种掩膜版版图,包括:第一版图层,包括沿第一方向延伸且沿第二方向平行排列的多个第一金属线图形,第二方向和第一方向垂直;第二版图层,位于第一版图层上方,第二版图层包括沿第二方向延伸且沿第一方向平行排列的多个第二金属线图形;第三版图层,位于第一版图层和第二版图层之间,第三版图层包括多个通孔互连结构图形,以第一金属线图形与第二金属线图形在水平面的投影交叠处作为交叉位置,通孔互连结构图形位于对角相邻的交叉位置。

13、可选的,多个通孔互连结构图形构成多个相互平行的通孔图形列,通孔图形列包括沿对角相邻的交叉位置的对角线排布的多个通孔互连结构图形。

14、可选的,沿第一方向,相邻通孔互连结构图形之间具有多个第二金属线图形;沿第二方向,相邻通孔互连结构图形之间具有多个第一金属线图形。

15、可选的,沿第一方向,相邻通孔互连结构图形之间具有2个第二金属线图形;沿第二方向,相邻通孔互连结构图形之间具有2个第一金属线图形。

16、可选的,相邻第一金属线图形之间的间隔相等;相邻第二金属线图形之间的间隔相等。

17、相应的,本发明实施例还提供一种测试方法,包括:提供本发明实施例的测试结构;将第一信号加载端和第二信号加载端中的任一个加载高电位,将第一信号加载端和第二信号加载端中的另一个加载低电位;加载高电位和低电位后,检测通孔互连结构与相邻第一金属线之间的漏电流。

18、可选的,检测通孔互连结构与相邻第一金属线之间的漏电流的步骤中,当漏电流大于或等于电流阈值时,表征对通孔互连结构的测试不通过;当漏电流小于电流阈值时,表征通孔互连结构通过测试。

19、与现有技术相比,本发明实施例的技术方案具有以下优点:

20、本发明实施例提供的测试结构中,以第一金属线与第二金属线在水平面的投影交叠处作为交叉位置,通孔互连结构位于对角相邻的交叉位置、且与对应的第一金属线和第二金属线电连接;在半导体工艺中,在形成通孔互连结构时,相邻通孔互连结构的间距越小,通孔互连结构产生的倒角越明显,通孔互连结构与相邻第一金属线之间的桥接风险越大,从而测试结果更为精准,相比于通常由于相邻第一金属线之间间距过小,而无法在相邻第一金属线沿第二方向相邻的交叉位置形成通孔互连结构,从而无法对间距较小的通孔互连结构进行通孔互连结构与相邻第一金属线之间的桥接风险测试的方案,本发明实施例中,通孔互连结构位于对角相邻的交叉位置,也就是说,沿对角相邻的交叉位置的对角线,相邻通孔互连结构之间的间距能够达到设计准则(design rule)所允许的最小间距,从而能够对间距较小的通孔互连结构进行通孔互连结构与相邻第一金属线之间的桥接风险测试,获得较为精准的测试结果,进而有利于提高测试结构的测试精度。

21、本发明实施例提供的掩膜版版图中,以第一金属线图形与第二金属线图形在水平面的投影交叠处作为交叉位置,通孔互连结构图形位于对角相邻的交叉位置;通孔互连结构图形用于形成通孔互连结构,第一金属线图形用于形成第一金属线,第二金属线图形用于形成第二金属线,在半导体工艺中,在形成通孔互连结构时,相邻通孔互连结构的间距越小,通孔互连结构产生的倒角越明显,通孔互连结构与相邻第一金属线之间的桥接风险越大,从而测试结果更为精准,相比于通常由于相邻第一金属线之间间距过小,而无法在相邻第一金属线沿第二方向相邻的交叉位置形成通孔互连结构,从而无法对间距较小的通孔互连结构进行通孔互连结构与相邻第一金属线之间的桥接风险测试的方案,本发明实施例中,通孔互连结构图形位于对角相邻的交叉位置,也就是说,通孔互连结构位于对角相邻的交叉位置,沿对角相邻的交叉位置的对角线,相邻通孔互连结构之间的间距能够达到设计准则(design rule)所允许的最小间距,从而能够对间距较小的通孔互连结构进行通孔互连结构与相邻第一金属线之间的桥接风险测试,获得较为精准的测试结果,进而有利于提高掩膜版对应的测试结构的测试精度。

22、本发明实施例提供的测试方法中,提供本发明实施例所述的测试结构,将第一信号加载端和第二信号加载端中的任一个加载高电位,将第一信号加载端和第二信号加载端中的另一个加载低电位,加载高电位和低电位后,检测通孔互连结构与相邻第一金属线之间的漏电流;在半导体工艺中,在形成通孔互连结构时,相邻通孔互连结构的间距越小,通孔互连结构产生的倒角越明显,通孔互连结构与相邻第一金属线之间的桥接风险越大,从而测试结果更为精准,相比于通常由于相邻第一金属线之间间距过小,而无法在相邻第一金属线沿第二方向相邻的交叉位置形成通孔互连结构,从而无法对间距较小的通孔互连结构进行通孔互连结构与相邻第一金属线之间的桥接风险测试的方案,本发明实施例中,通孔互连结构位于对角相邻的交叉位置,也就是说,沿对角相邻的交叉位置的对角线,相邻通孔互连结构之间的间距能够达到设计准则(design rule)所允许的最小间距,从而能够对间距较小的通孔互连结构进行通孔互连结构与相邻第一金属线之间的桥接风险测试,获得较为精准的测试结果,进而有利于提高测试结构的测试精度。

本文地址:https://www.jishuxx.com/zhuanli/20240731/179212.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表