3D垂直互连封装结构及其制备方法与流程

- 国知局

- 2024-07-31 19:01:02

本发明属于半导体制造,涉及一种3d垂直互连封装结构及其制备方法。

背景技术:

1、电子产品的迅猛发展是当今封装技术进化的主要驱动力,小型化、高密度、高频、高速、高可靠性和低成本是先进封装的主流发展方向。其中系统级封装(system in apackage,sip)是最重要也是最有潜力满足这种高密度系统集成的技术之一。

2、sip封装是指将多种功能芯片,如处理器、存储器等,根据应用场景或封装基板层数等集成在一个封装结构内的封装方式,以通过一个封装结构实现完整功能。

3、目前,为了实现封装小型化,大多直接利用3d堆栈方式进行封装,其中,用来作为垂直互连的方法有很多,目前最常用的就是如图1所示的铜柱垂直互连,但在采用铜柱垂直互连的结构中,由于受到光刻工艺条件的限制,该垂直互连结构中的最小间距p(pitch)约为300μm,高度h最高只能约为200μm,无法实现更高密度的封装。

4、因此,提供一种3d垂直互连封装结构及其制备方法,实属必要。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种3d垂直互连封装结构及其制备方法,用于解决现有技术中难以制备高密度封装结构的问题。

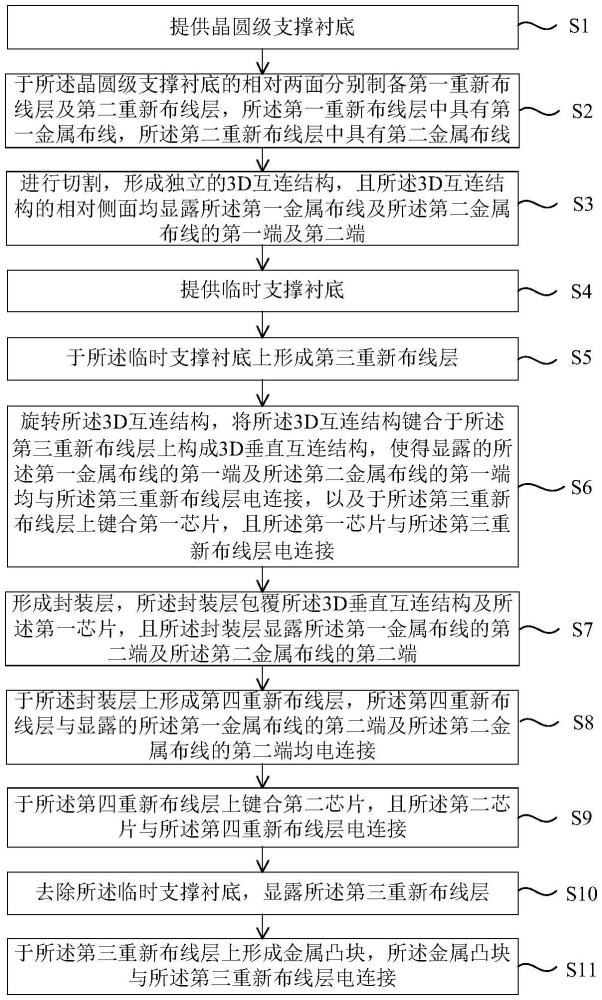

2、为实现上述目的及其他相关目的,本发明提供一种3d垂直互连封装结构的制备方法,包括以下步骤:

3、提供晶圆级支撑衬底;

4、于所述晶圆级支撑衬底的相对两面分别制备第一重新布线层及第二重新布线层,所述第一重新布线层中具有第一金属布线,所述第二重新布线层中具有第二金属布线;

5、进行切割,形成独立的3d互连结构,且所述3d互连结构的相对侧面均显露所述第一金属布线及所述第二金属布线的第一端及第二端;

6、提供临时支撑衬底;

7、于所述临时支撑衬底上形成第三重新布线层;

8、旋转所述3d互连结构,将所述3d互连结构键合于所述第三重新布线层上构成3d垂直互连结构,使得显露的所述第一金属布线的第一端及所述第二金属布线的第一端均与所述第三重新布线层电连接,以及于所述第三重新布线层上键合第一芯片,且所述第一芯片与所述第三重新布线层电连接;

9、形成封装层,所述封装层包覆所述3d垂直互连结构及所述第一芯片,且所述封装层显露所述第一金属布线的第二端及所述第二金属布线的第二端;

10、于所述封装层上形成第四重新布线层,所述第四重新布线层与显露的所述第一金属布线的第二端及所述第二金属布线的第二端均电连接;

11、于所述第四重新布线层上键合第二芯片,且所述第二芯片与所述第四重新布线层电连接;

12、去除所述临时支撑衬底,显露所述第三重新布线层;

13、于所述第三重新布线层上形成金属凸块,所述金属凸块与所述第三重新布线层电连接。

14、可选地,所述3d垂直互连结构中所述第一金属布线间的间距为3~50μm;所述3d垂直互连结构中所述第二金属布线间的间距为3~50μm。

15、可选地,所述第一金属布线与所述第三重新布线层及所述第四重新布线层均相垂直;所述第二金属布线与所述第三重新布线层及所述第四重新布线层均相垂直。

16、可选地,所述临时支撑衬底包括晶圆级临时衬底。

17、可选地,所述第二芯片与所述第四重新布线层之间形成有填充缝隙的底部填充层。

18、可选地,切割形成独立的所述3d互连结构的方法包括机械切割或激光切割中的一种或组合。

19、本发明还提供一种3d垂直互连封装结构,所述3d垂直互连封装结构包括:

20、第三重新布线层;

21、3d垂直互连结构,所述3d垂直互连结构键合于所述第三重新布线层上,所述3d垂直互连结构包括支撑衬底及位于所述支撑衬底的相对两面的第一重新布线层及第二重新布线层,所述第一重新布线层中具有第一金属布线,所述第二重新布线层中具有第二金属布线,且显露的所述第一金属布线的第一端及所述第二金属布线的第一端均与所述第三重新布线层电连接;

22、第一芯片,所述第一芯片键合于所述第三重新布线层上,且所述第一芯片与所述第三重新布线层电连接;

23、封装层,所述封装层包覆所述3d垂直互连结构及所述第一芯片,且所述封装层显露所述第一金属布线的第二端及所述第二金属布线的第二端;

24、第四重新布线层,所述第四重新布线层位于所述封装层上,且所述第四重新布线层与显露的所述第一金属布线的第二端及所述第二金属布线的第二端均电连接;

25、第二芯片,所述第二芯片键合于所述第四重新布线层上,且所述第二芯片与所述第四重新布线层电连接;

26、金属凸块,所述金属凸块位于所述第三重新布线层上且与所述第三重新布线层电连接。

27、可选地,所述3d垂直互连结构中所述第一金属布线间的间距为3~50μm;所述3d垂直互连结构中所述第二金属布线间的间距为3~50μm。

28、可选地,所述第一金属布线与所述第三重新布线层及所述第四重新布线层均相垂直;所述第二金属布线与所述第三重新布线层及所述第四重新布线层均相垂直。

29、可选地,所述第二芯片与所述第四重新布线层之间具有填充缝隙的底部填充层。

30、如上所述,本发明的3d垂直互连封装结构及其制备方法,通过制备双面具有重新布线层的3d互连结构,并在键合时将3d互连结构垂直设置以构成3d垂直互连结构,从而可通过控制3d互连结构中的介电层的厚度以控制3d垂直互连结构中金属布线间的间距,使得间距可缩小至3μm,通过控制3d互连结构中的金属布线的长度以控制3d垂直互连结构中金属布线的高度,且通过控制3d互连结构中的金属布线的厚度以控制3d垂直互连结构中金属布线的接触点的大小。

31、因此,本发明通过双面的3d垂直互连结构可实现高密度封装,且制程工艺灵活,适用范围广。

技术特征:1.一种3d垂直互连封装结构的制备方法,其特征在于,包括以下步骤:

2.根据权利要求1所述的3d垂直互连封装结构的制备方法,其特征在于:所述3d垂直互连结构中所述第一金属布线间的间距为3~50μm;所述3d垂直互连结构中所述第二金属布线间的间距为3~50μm。

3.根据权利要求1所述的3d垂直互连封装结构的制备方法,其特征在于:所述第一金属布线与所述第三重新布线层及所述第四重新布线层均相垂直;所述第二金属布线与所述第三重新布线层及所述第四重新布线层均相垂直。

4.根据权利要求1所述的3d垂直互连封装结构的制备方法,其特征在于:所述临时支撑衬底包括晶圆级临时衬底。

5.根据权利要求1所述的3d垂直互连封装结构的制备方法,其特征在于:所述第二芯片与所述第四重新布线层之间形成有填充缝隙的底部填充层。

6.根据权利要求1所述的3d垂直互连封装结构的制备方法,其特征在于:切割形成独立的所述3d互连结构的方法包括机械切割或激光切割中的一种或组合。

7.一种3d垂直互连封装结构,其特征在于,所述3d垂直互连封装结构包括:

8.根据权利要求7所述的3d垂直互连封装结构,其特征在于:所述3d垂直互连结构中所述第一金属布线间的间距为3~50μm;所述3d垂直互连结构中所述第二金属布线间的间距为3~50μm。

9.根据权利要求7所述的3d垂直互连封装结构,其特征在于:所述第一金属布线与所述第三重新布线层及所述第四重新布线层均相垂直;所述第二金属布线与所述第三重新布线层及所述第四重新布线层均相垂直。

10.根据权利要求7所述的3d垂直互连封装结构,其特征在于:所述第二芯片与所述第四重新布线层之间具有填充缝隙的底部填充层。

技术总结本发明提供一种3D垂直互连封装结构及其制备方法,通过制备双面具有重新布线层的3D互连结构,并在键合时将3D互连结构垂直设置以构成3D垂直互连结构,从而可通过控制3D互连结构中的介电层的厚度以控制3D垂直互连结构中金属布线间的间距,使得间距可缩小至3μm,通过控制3D互连结构中的金属布线的长度以控制3D垂直互连结构中金属布线的高度,且通过控制3D互连结构中的金属布线的厚度以控制3D垂直互连结构中金属布线的接触点的大小;本发明通过双面的3D垂直互连结构可实现高密度封装,且制程工艺灵活,适用范围广。技术研发人员:陈彦亨,林正忠受保护的技术使用者:盛合晶微半导体(江阴)有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/181365.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表