浮栅的制备方法与流程

- 国知局

- 2024-07-31 19:06:55

本发明涉及半导体,尤其涉及一种浮栅的制备方法。

背景技术:

1、闪存是一种非易失存储器,其包括多个闪存单元,闪存单元包括浮栅、ono结构层和控制栅,多个闪存单元一般呈阵列排布。目前,由于制备工艺缺陷,普遍在各闪存单元之间会形成漏电失效的问题,例如由于闪存单元制备时浮栅的尺寸较难精准的控制,浮栅的侧壁倾斜且容易产生多晶硅残留,导致相邻闪存单元之间形成漏电路径,影响闪存的可靠性。

技术实现思路

1、本发明的目的在于提供一种浮栅的制备方法,能够降低漏电的可能性,提高器件的可靠性,并且能够对浮栅的尺寸进行精准控制。

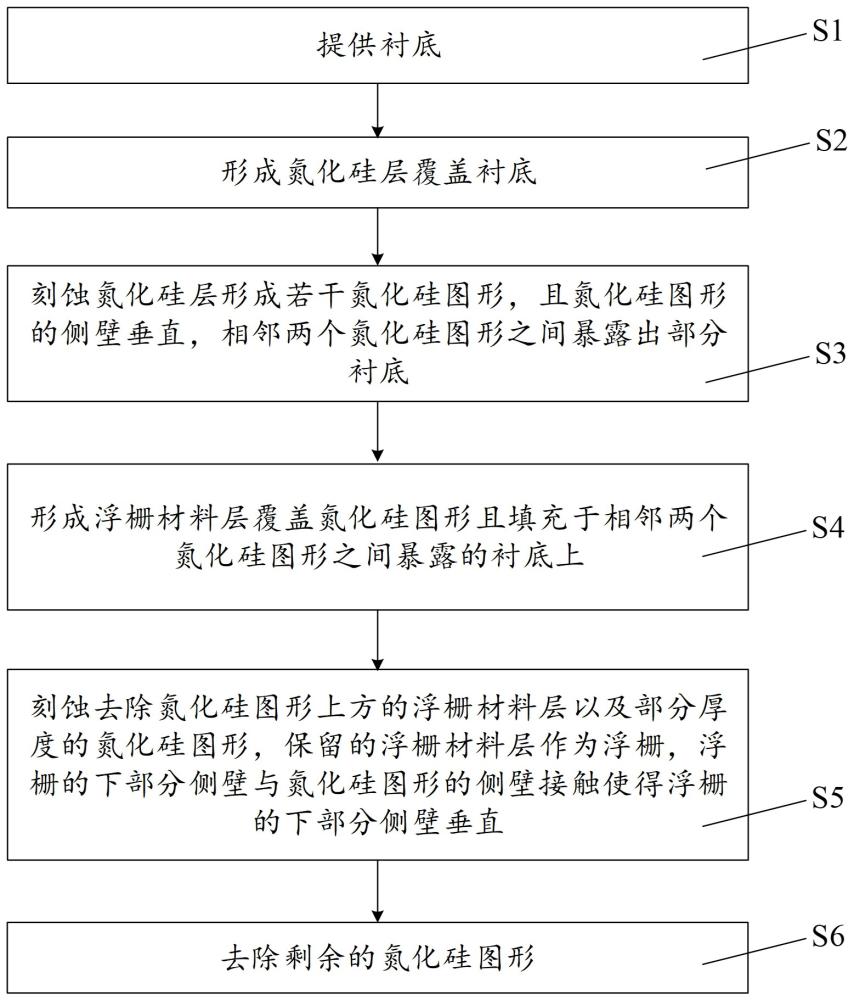

2、为了达到上述目的,本发明提供了一种浮栅的制备方法,包括:

3、提供衬底;

4、形成氮化硅层覆盖所述衬底;

5、刻蚀所述氮化硅层形成若干氮化硅图形,且所述氮化硅图形的侧壁垂直,相邻两个所述氮化硅图形之间暴露出部分所述衬底;

6、形成浮栅材料层覆盖所述氮化硅图形且填充于相邻两个所述氮化硅图形之间暴露的所述衬底上;

7、刻蚀去除所述氮化硅图形上方的浮栅材料层以及部分厚度的所述氮化硅图形,保留的所述浮栅材料层作为浮栅,所述浮栅的下部分侧壁与所述氮化硅图形的侧壁接触使得所述浮栅的下部分侧壁垂直;以及,

8、去除剩余的所述氮化硅图形。

9、可选的,形成所述浮栅材料层后,所述氮化硅图形的厚度为所述浮栅材料层的厚度的三分之一至三分之二。

10、可选的,形成若干所述氮化硅图形的步骤包括:

11、形成第一图形化的光刻胶层覆盖所述氮化硅层;

12、以所述第一图形化的光刻胶层为掩模,执行第一干法刻蚀工艺刻蚀所述氮化硅层,以形成若干所述氮化硅图形;

13、去除所述第一图形化的光刻胶层。

14、可选的,形成所述浮栅材料层后,位于所述衬底上的浮栅材料层的顶部高于所述氮化硅图形的顶部,且位于所述氮化硅图形上的浮栅材料层的顶部高于位于所述衬底上的浮栅材料层的顶部;以及,通过执行研磨工艺研磨所述浮栅材料层使得所述浮栅材料层的顶部齐平。

15、可选的,刻蚀去除所述氮化硅图形上方的浮栅材料层以及部分厚度的所述氮化硅图形的步骤包括:

16、形成第二图形化的光刻胶层覆盖所述浮栅材料层;

17、以所述第二图形化的光刻胶层为掩模,执行第二干法刻蚀工艺刻蚀去除所述氮化硅图形上方的浮栅材料层以及部分厚度的所述氮化硅图形;

18、去除所述第二图形化的光刻胶层。

19、可选的,执行所述第二干法刻蚀工艺时,所述浮栅材料层和所述氮化硅图形的刻蚀选择比大于1:1。

20、可选的,刻蚀去除所述氮化硅图形上方的浮栅材料层以及部分厚度的所述氮化硅图形后,所述氮化硅图形的剩余厚度为所述浮栅的高度的六分之一至四分之一。

21、可选的,采用湿法刻蚀工艺刻蚀去除剩余的所述氮化硅图形。

22、可选的,所述湿法刻蚀工艺的刻蚀剂包括热磷酸。

23、可选的,形成所述氮化硅层覆盖所述衬底前,所述衬底中形成有若干沟槽隔离结构,以及在相邻两个所述沟槽隔离结构之间的衬底上形成有隧穿氧化层;形成所述氮化硅图形后所述氮化硅图形位于所述沟槽隔离结构上,以及形成所述浮栅后所述浮栅位于所述隧穿氧化层上。

24、在本发明提供的浮栅的制备方法中,提供衬底,形成氮化硅层覆盖衬底,刻蚀氮化硅层形成若干氮化硅图形,由于氮化硅材质特性,使得氮化硅图形的侧壁垂直,相邻两个氮化硅图形之间暴露出部分衬底;然后形成浮栅材料层覆盖氮化硅图形且填充于相邻两个氮化硅图形之间暴露的衬底上;再刻蚀去除氮化硅图形上方的浮栅材料层以及部分厚度的氮化硅图形,保留的浮栅材料层作为浮栅;本发明意想不到的技术效果是由于氮化硅图形的侧壁垂直,保留的浮栅材料层作为浮栅,浮栅的下部分侧壁与氮化硅图形的侧壁接触使得浮栅的下部分侧壁垂直,浮栅的下部分侧壁垂直能够保证不会在浮栅的两侧底部产生多晶硅残留,降低漏电的可能性,提高器件的可靠性;并且能够对浮栅的尺寸进行精准控制,利于控制浮栅的存储容量。

技术特征:1.一种浮栅的制备方法,其特征在于,包括:

2.如权利要求1所述的浮栅的制备方法,其特征在于,形成所述浮栅材料层后,所述氮化硅图形的厚度为所述浮栅材料层的厚度的三分之一至三分之二。

3.如权利要求1所述的浮栅的制备方法,其特征在于,形成若干所述氮化硅图形的步骤包括:

4.如权利要求1所述的浮栅的制备方法,其特征在于,形成所述浮栅材料层后,位于所述衬底上的浮栅材料层的顶部高于所述氮化硅图形的顶部,且位于所述氮化硅图形上的浮栅材料层的顶部高于位于所述衬底上的浮栅材料层的顶部;以及,通过执行研磨工艺研磨所述浮栅材料层使得所述浮栅材料层的顶部齐平。

5.如权利要求1所述的浮栅的制备方法,其特征在于,刻蚀去除所述氮化硅图形上方的浮栅材料层以及部分厚度的所述氮化硅图形的步骤包括:

6.如权利要求5所述的浮栅的制备方法,其特征在于,执行所述第二干法刻蚀工艺时,所述浮栅材料层和所述氮化硅图形的刻蚀选择比大于1:1。

7.如权利要求1或5所述的浮栅的制备方法,其特征在于,刻蚀去除所述氮化硅图形上方的浮栅材料层以及部分厚度的所述氮化硅图形后,所述氮化硅图形的剩余厚度为所述浮栅的高度的六分之一至四分之一。

8.如权利要求1所述的浮栅的制备方法,其特征在于,采用湿法刻蚀工艺刻蚀去除剩余的所述氮化硅图形。

9.如权利要求8所述的浮栅的制备方法,其特征在于,所述湿法刻蚀工艺的刻蚀剂包括热磷酸。

10.如权利要求1所述的浮栅的制备方法,其特征在于,形成所述氮化硅层覆盖所述衬底前,所述衬底中形成有若干沟槽隔离结构,以及在相邻两个所述沟槽隔离结构之间的衬底上形成有隧穿氧化层;形成所述氮化硅图形后所述氮化硅图形位于所述沟槽隔离结构上,以及形成所述浮栅后所述浮栅位于所述隧穿氧化层上。

技术总结本发明提供了一种浮栅的制备方法,包括:提供衬底,形成氮化硅层覆盖衬底,刻蚀氮化硅层形成若干氮化硅图形,由于氮化硅材质特性,使得氮化硅图形的侧壁垂直,相邻两个氮化硅图形之间暴露出部分衬底;然后形成浮栅材料层覆盖氮化硅图形且填充于相邻两个氮化硅图形之间暴露的衬底上;再刻蚀去除氮化硅图形上方的浮栅材料层以及部分厚度的氮化硅图形,保留的浮栅材料层作为浮栅,浮栅的下部分侧壁与氮化硅图形的侧壁接触使得浮栅的下部分侧壁垂直;以及,去除剩余的氮化硅图形;本发明能够降低漏电的可能性,提高器件的可靠性,并且对浮栅的尺寸进行精准控制。技术研发人员:王敦年,张星池,谢荣源,林滔天,祝进专受保护的技术使用者:合肥晶合集成电路股份有限公司技术研发日:技术公布日:2024/7/29本文地址:https://www.jishuxx.com/zhuanli/20240731/181680.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表