用于存储应用的具有翻盖式放置的混合PCB拓扑和布局的制作方法

- 国知局

- 2024-07-31 19:07:59

本发明涉及在非易失性存储系统的印刷电路板(pcb)上非易失性存储设备的放置问题,并且特别涉及多点多负载非易失性存储接口拓扑,其中多个非易失性存储设备共享耦合到非易失性存储控制器的公共数据总线。

背景技术:

1、固态硬盘(ssd)的出现在一定程度上推动了现代计算系统的发展,固态硬盘(ssd)的速度和延迟性能比传统硬盘更高。与依靠磁性来存储数据的硬盘不同,固态硬盘使用nand闪存设备来实现数据存储。nand闪存设备是通过先进工艺和组装技术制造的可实现存储单元的多层次垂直堆叠到较小的封装中以实现高存储容量的集成电路的系列。

2、典型的ssd由一个控制器和多个nand闪存设备组成,这些设备放置在具有标准外形尺寸的印刷电路板(pcb)上并通过它进行连接,适用于各种消费者或企业使用模式。控制器和nand闪存设备之间的接口分组为通道,现代控制器通常具有4、8或16个nand通道。为了实现更高的存储容量,ssd需要将更多的nand闪存设备集成到pcb中,从而导致多个nand设备共享单个通道。结果,对于高密度固态硬盘的设计,通常采用多负载或多点pcb拓扑。

技术实现思路

1、翻盖式拓扑已用于大容量ssd多负载pcb,例如但不限于m.2或u.2外形尺寸。在该拓扑中,可以放置一对非易失性存储设备,使得pcb的一侧上的一个非易失性存储设备可以与另一侧上的另一个非易失性存储设备完全重叠。翻盖式结构中的一对或多对非易失性存储设备可以共享一个通道。传统上,共享一个通道的所有非易失性存储设备的信号路线(例如,数据总线和信号路径)可以紧密匹配(例如,对于电阻和电容),而不管非易失性存储设备是否具有相同的容量。根据本公开的实施例,提供了一种支持混合负载条件的混合pcb拓扑和布局技术,所述混合负载条件允许在不牺牲速度性能的情况下在具有不同容量的非易失性存储设备(例如,高容量和低容量设备)之间共享数据总线。

2、在一个示例性实施例中,提供了一种非易失性存储系统。非易失性存储系统可以包括印刷电路板(pcb)、具有第一容量并且附接到pcb的第一侧的第一非易失性存储设备、具有第二容量并且附接到pcb的第二侧的第二非易失性存储设备、以及通过共享通道耦合到所述第一非易失性存储设备和所述第二非易失性存储设备的存储控制器。所述第二容量可以不同于所述第一容量。所述第一非易失性存储设备和所述第二非易失性存储设备可以被放置在第一翻盖式结构中。所述共享通道可以具有通往所述第一非易失性存储设备的第一引脚的第一信号路线和通往所述第二非易失性存储设备的第二引脚的第二信号路线。所述第一引脚可以具有第一引脚电容,并且所述第二引脚可以具有第二引脚电容。所述第一引脚电容可以小于所述第二引脚电容。所述第一信号路线和所述第二信号路线可以共享主干线和第一分支,但是具有单独的设备分支,并且所述第一信号路线可以具有第一设备分支,与所述第二信号路线的第二设备分支相比,所述第一设备分支具有串联的第一额外电阻。所述第一额外电阻可以被放置在所述pcb的第一侧。

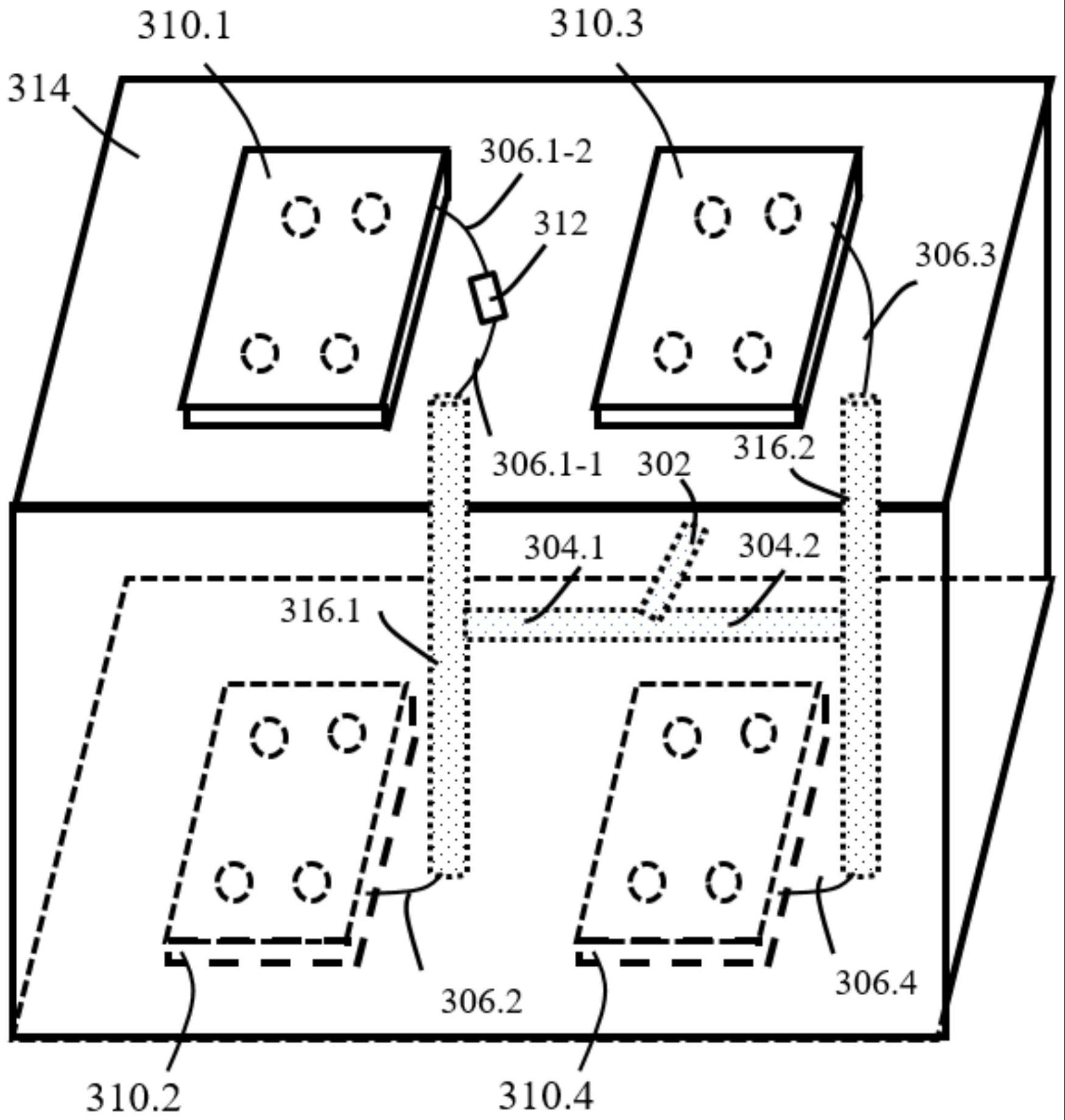

3、在另一个示例性实施例中,提供了另一种非易失性存储系统,其可以包括印刷电路板(pcb)、具有第一容量并且附接到pcb的第一侧的第一非易失性存储设备、具有第二容量并附接到pcb的第二侧的第二非易失性存储设备、具有第三容量并且附接到pcb的第一侧的第三非易失性存储设备,具有第四容量并且附接到pcb的第二侧的第四非易失性存储设备,以及通过共享通道耦合到所述第一非易失性存储设备、所述第二非易失性存储设备、所述第三非易失性存储设备和所述第四非易失性存储设备的存储控制器。所述第二容量可以不同于所述第一容量。所述第一非易失性存储设备和所述第二非易失性存储设备可以被放置在第一翻盖式结构中。所述第三容量和所述第四容量可以与所述第二容量相同。所述第三非易失性存储设备和所述第四非易失性存储设备可以被放置在第二翻盖式结构中。所述共享通道可以具有通往所述第一非易失性存储设备的第一引脚的第一信号路线、通往所述第二非易失性存储设备的第二引脚的第二信号路线、通往所述第三非易失性存储设备的第三引脚的第三信号路线以及通往所述第四非易失性存储设备的第四引脚的第四信号路线。所述第一引脚可以具有第一引脚电容,所述第二引脚可以具有第二引脚电容,所述第三引脚可以具有第三引脚电容,并且所述第四引脚可以具有第四引脚电容。所述第一引脚电容可以小于所述第二引脚电容,所述第三引脚电容和所述第四引脚电容可以与所述第二引脚电容相同。所述第一信号路线和所述第二信号路线可以共享主干线和第一分支,但是具有单独的设备分支。所述第一信号路线可以具有第一设备分支,与所述第二信号路线的第二设备分支相比,所述第一设备分支具有串联的第一额外电阻,第一额外电阻可以被放置在所述pcb的第一侧。所述第三信号路线和所述第四信号路线可以共享所述主干线和第二分支,但是具有单独的紧密匹配的设备分支。所述第二分支可以与所述第一分支紧密匹配。

4、在又一个示例性实施例中,提供了又一种非易失性存储系统,其可以包括印刷电路板(pcb)、具有第一容量并且附接到所述pcb的第一侧的第一非易失性存储设备、具有第二容量并且附接到所述pcb的第二侧的第二非易失性存储设备、具有第三容量并且附接到所述pcb的第一侧的第三非易失性存储设备、具有第四容量并且附接到所述pcb的第二侧的第四非易失性存储设备,以及通过共享通道耦合到所述第一非易失性存储设备、所述第二非易失性存储设备、所述第三非易失性存储设备和所述第四非易失性存储设备的存储控制器。所述第二容量可以不同于所述第一容量。所述第三容量可以与所述第二容量相同,所述第四容量可以与所述第一容量相同。所述第一非易失性存储设备和所述第二非易失性存储设备可以被放置在第一翻盖式结构中。所述第三非易失性存储设备和所述第四非易失性存储设备可以被放置在第二翻盖式结构中。所述共享通道可以具有通往所述第一非易失性存储设备的第一引脚的第一信号路线、通往所述第二非易失性存储设备的第二引脚的第二信号路线、通往所述第三非易失性存储设备的第三引脚的第三信号路线以及通往所述第四非易失性存储设备的第四引脚的第四信号路线。所述第一引脚可以具有第一引脚电容,所述第二引脚可以具有第二引脚电容,所述第三引脚可以具有第三引脚电容,并且所述第四引脚可以具有第四引脚电容。所述第一引脚电容可以小于所述第二引脚电容,所述第三引脚电容可以与所述第二引脚电容相同,所述第四引脚电容可以与所述第一引脚电容相同。所述第一信号路线和所述第二信号路线可以共享主干线和第一分支,但是具有单独的设备分支,并且所述第一信号路线可以具有第一设备分支,与所述第二信号路线的第二设备分支相比,所述第一设备分支具有串联的第一额外电阻。所述第一额外电阻可以放置在所述pcb的第一侧。所述第三信号路线和所述第四信号路线可以共享所述主干线和第二分支,但是具有单独的设备分支。所述第二分支可以与所述第一分支紧密匹配,并且所述第四信号路线可以具有第四设备分支,与所述第三信号路线的第三设备分支相比,所述第四设备分支具有串联的第二额外电阻。所述第二额外电阻可以放置在所述pcb的第二侧。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181720.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表