随机存取存储器的自检修补装置及其方法、芯片设备与流程

- 国知局

- 2024-07-31 19:07:51

本发明涉及存储器,特别涉及一种随机存取存储器的自检修补装置、一种随机存取存储器的自检修补方法和一种芯片设备。

背景技术:

1、在通用的微控制器(microcontroller unit,mcu)中,随机存取存储器(randomaccess memory,ram)是最常见的数据存储器。它支持实时的和高速的存取操作,是与mcu直接进行数据交互的内部存储器,通常作为运行程序的临时数据存储介质。然而,ram阵列在生产过程和用户使用的老化过程中都会出现损坏点(即错误位),尤其是在尺寸较大的ram阵列中,更容易出现损坏点,降低了芯片的成品率和可靠性,限制了ram阵列的使用寿命。为了保证ram存储数据的可靠性和老化预知,通常需要对ram阵列进行定期自检(self test),比如上电自检和周期性自检。但是,仅对ram阵列做自检只能筛查出有损坏点的芯片,并不能有效提高芯片的成品率和使用寿命。

2、目前,在测试阶段和应用阶段,常用的ram修补方案一般是通过非易失性存储器(nonvolatile memory,nvm)来存储和加载ram阵列的错误地址,从而实现ram阵列的一次性修补。还有些方案需要额外的行列备用阵列或者冗余地址实现对ram阵列的修补。因此,这些方案通常需要以下步骤来完成ram阵列的自检和一次性修补:1)通过bist(built inself test,内置自检)电路或者软件指令向目标ram进行自检操作;2)把自检中检测到的错误地址存入特定的nvm或者可电熔断efuse(electric-fuse,电子保险丝)的存储空间中;3)通过特定的硬件装置实现ram阵列中错误地址的替换或者重新映射。上述的修补方案通常占用了过多的硬件资源,比如专用的bist电路、非易失性存储器(nvm)、备用阵列或者冗余地址,并且灵活性较低,无法支持在应用过程中的实时修补。

技术实现思路

1、本发明旨在至少在一定程度上解决相关技术中的技术问题之一。为此,本发明的目的在于提出一种随机存取存储器的自检修补装置及其方法、芯片设备,以实现对随机存取存储器的实时自检和修补,提高随机存取存储器的使用寿命。

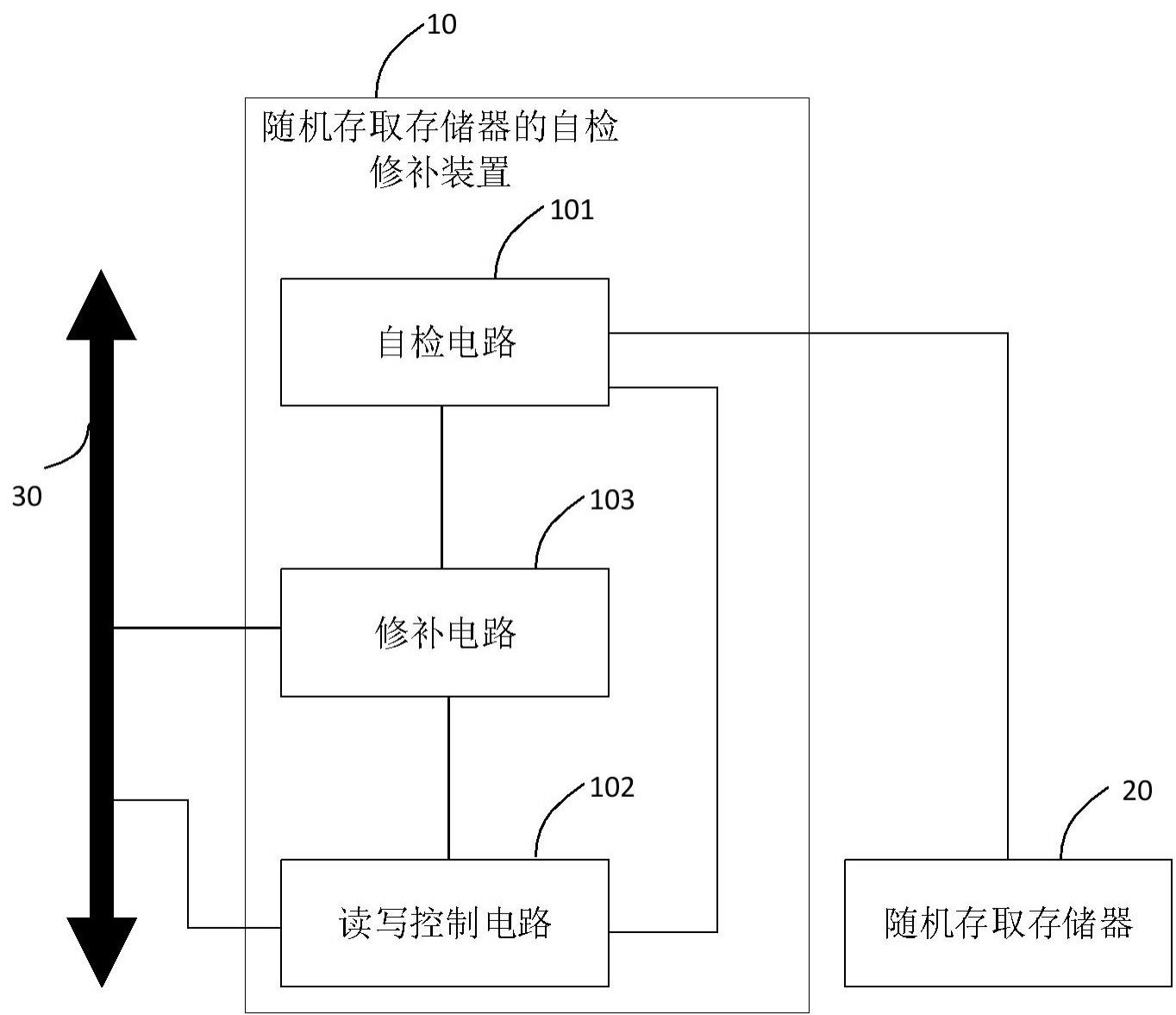

2、为达到上述目的,本发明第一方面实施例提出了一种随机存取存储器的自检修补装置,所述装置包括:自检电路、读写控制电路和修补电路。所述自检电路用以连接随机存取存储器,用于在接收到自检触发信号时,取得所述随机存取存储器的存取控制权,并对所述随机存取存储器进行扫描自检并输出修补地址;所述读写控制电路用以连接系统总线和所述自检电路,用于根据所述系统总线发送的操作地址进行数据存取操作;所述修补电路分别与所述自检电路和所述读写控制电路连接,并用以连接系统总线,用于在存在与所述操作地址匹配的修补地址时,根据所述匹配的修补地址通过所述读写控制电路对所述随机存取存储器中的错误地址进行重映射修补。

3、另外,本发明实施例的随机存取存储器的自检修补装置还可以具有如下附加技术特征:

4、根据本发明的一个实施例,所述自检电路包括:自检控制器和自检通道选择器;所述自检通道选择器用以连接随机存取存储器;所述自检控制器与所述自检通道选择器连接,用于根据接收到的自检触发信号生成自检总线选择信号,并将所述自检总线选择信号发送给所述自检通道选择器,以通过所述自检通道选择器选通自检总线,取得所述随机存取存储器的存取控制权,以及对所述随机存取存储器进行扫描自检并输出修补地址。

5、根据本发明的一个实施例,所述修补电路包括:修补地址寄存器组、修补数据寄存器组、地址判断器和修补通路选择器;所述修补地址寄存器组与所述自检控制器连接,用于将所述修补地址存储至相应的修补地址寄存器,并将对应的标识位置为有效,其中,所述修补地址寄存器组包括多个所述修补地址寄存器,对应每个所述修补地址寄存器设有标识位;所述地址判断器与所述修补地址寄存器组连接,用于根据所述系统总线发送的操作地址查询有效的标识位对应的修补地址寄存器,并在查询到与所述操作地址匹配的修补地址后,输出修补译码地址和修补总线选择信号;所述修补数据寄存器组与所述地址判断器连接,用于根据所述修补译码地址选取对应的修补数据寄存器,其中,所述修补数据寄存器组包括多个所述修补数据寄存器;所述修补通路选择器分别与所述修补数据寄存器组、所述地址判断器、所述读写控制电路和所述自检通道选择器连接,用于在接收到所述修补总线选择信号时,选通修补总线,以通过所述读写控制电路对选取的修补数据寄存器进行存取操作,以及在未接收到所述修补总线选择信号时,选通ram总线,以在所述自检通道选择器也选通所述ram总线时,通过所述读写控制电路对所述随机存取存储器进行存取操作。

6、根据本发明的一个实施例,多个所述修补地址寄存器与多个所述修补数据寄存器一一对应。

7、根据本发明的一个实施例,所述修补地址寄存器的有效数据位宽等于所述随机存取存储器的有效地址宽度,所述修补数据寄存器的有效数据位宽等于所述随机存取存储器的有效数据位宽。

8、根据本发明的一个实施例,所述修补地址寄存器的个数根据所述随机存取存储器的尺寸和所述随机存取存储器在有效生命周期内产生损坏的概率确定。

9、根据本发明的一个实施例,所述地址判断器采用内容可寻址存储器。

10、为达到上述目的,本发明第二方面实施例提出了一种随机存取存储器的自检修补装置的自检修补方法,所述随机存取存储器的自检修补装置为上述的随机存取存储器的自检修补装置,所述自检修补方法包括:自检控制器在接收到自检触发信号后,生成自检总线选择信号并发送给自检通道选择器;所述自检通道选择器选通自检总线,并取得所述随机存取存储器的存取控制权;所述自检控制器对所述随机存取存储器进行扫描自检,输出修补地址;将所述修补地址存储至相应的修补地址寄存器,并将对应的标识位置为有效;自检完成后,所述自检控制器释放所述随机存取存储器的存取控制权;根据所述系统总线发送的操作地址查询有效的标识位对应的所述修补地址寄存器;在查询到与所述操作地址匹配的修补地址后,输出修补译码地址和修补总线选择信号;修补通路选择器在接收到所述修补总线选择信号时,选通修补总线,修补数据寄存器组根据所述修补译码地址选取对应的修补数据寄存器,以通过所述读写控制电路对选取的修补数据寄存器进行存取操作;在所述操作地址与所述修补地址都不匹配时,修补通路选择器选通ram总线,通过所述读写控制电路对所述随机存取存储器进行存取操作。

11、另外,本发明实施例的一种随机存取存储器的自检修补装置的自检修补方法还可以具有如下附加技术特征:

12、根据本发明的一个实施例,在自检控制器在接收到自检触发信号后,生成自检总线选择信号并发送给自检通道选择器之前,所述自检修补方法,还包括:对所述修补数据寄存器、所述修补地址寄存器和所述修补地址寄存器对应的标识位进行上电复位;其中,在所述修补数据寄存器组复位后,所述修补数据寄存器中的数据为初始值,在所述修补地址寄存器组复位后,所述修补地址寄存器中的修补地址处于无效状态。

13、为达到上述目的,本发明第三方面实施例提出了一种芯片设备,包括:上述的随机存取存储器的自检修补装置。

14、本发明实施例的随机存取存储器的自检修补装置及其方法、芯片设备,能够实时完成随机存取存储器的自检和修补,减少因修补造成的其它硬件和软件资源的开销,有利于降低成本。同时,能够有效提高随机存取存储器的使用寿命。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181714.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表