一种兼容性的子母板芯片测试系统的制作方法

- 国知局

- 2024-07-31 19:09:39

本技术涉及芯片测试,尤其涉及一种兼容性的子母板芯片测试系统。

背景技术:

1、目前,随着lpddr4内存芯片的制程逐渐在增加,对于一些比较隐性的问题难以在短时间暴露出来,需要长时间的老化测试。老化测试系统按子板+母板的结构设计,在以往的测试方式中,子板和母板搭配使用,一套子板就需要配一套母板,不能做到兼容设计。

技术实现思路

1、有鉴于此,本实用新型实施例的目的是提供一种兼容性的子母板芯片测试系统,只需设计一套母板便能兼容不同类型的子板进行老化测试。

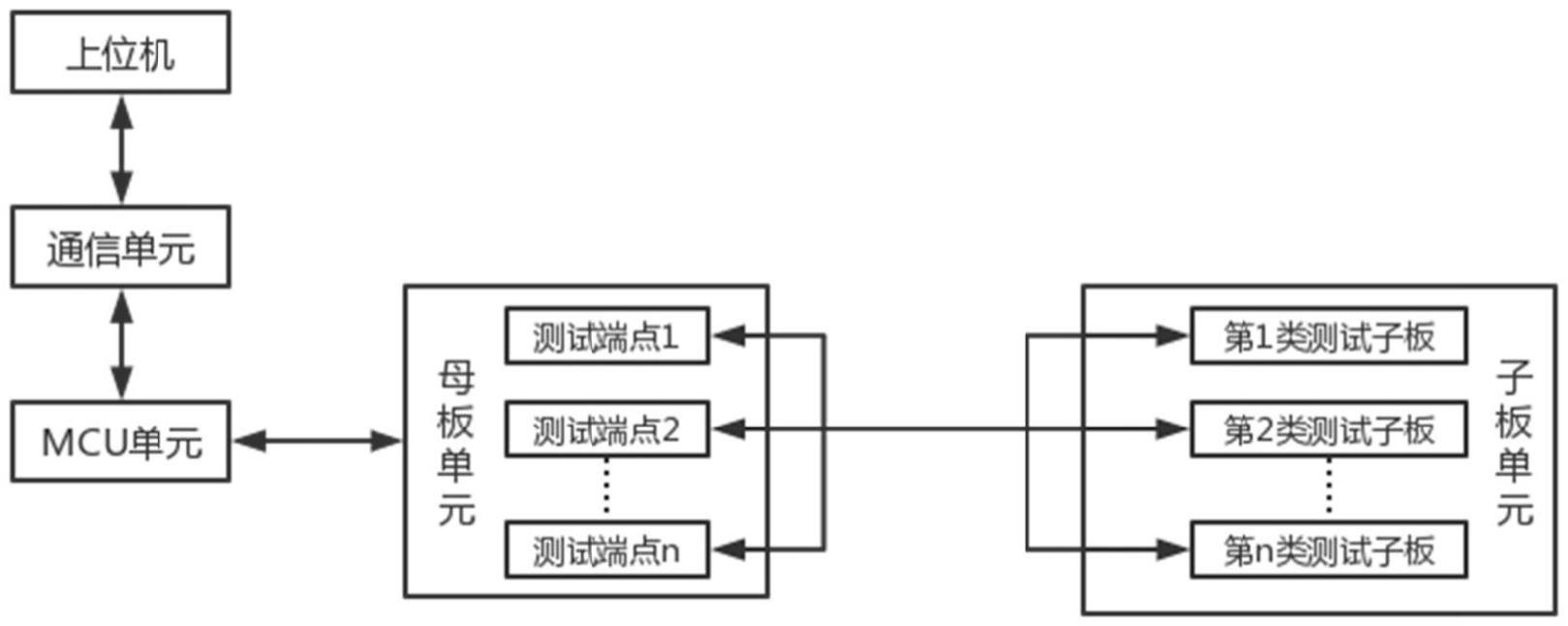

2、本实用新型实施例提供一种兼容性的子母板芯片测试系统,包括上位机、通信单元、mcu单元、母板单元和子板单元;

3、所述上位机与所述通信单元连接,所述上位机用于向所述通信单元发送测试指令和接收所述通信单元发送的测试结果;

4、所述mcu单元用于接收所述通信单元发送的测试指令,并发送相应的测试信息到所述母板单元,所述mcu单元接收所述母板单元发送的所述测试结果并输入至所述通信单元;

5、所述母板单元包括多个测试端点,所述母板单元接收所述mcu单元的测试信息并发送相应的选择信号至所述子板单元,所述母板单元相应的测试端点对所述子板单元进行测试得到所述测试结果,并将所述测试结果输入至所述mcu单元;

6、所述子板单元包括多个不同类型的测试子板,所述子板单元接收所述母板单元的选择信号,所述选择信号驱动相应的测试子板与所述相应的测试端点进行测试。

7、可选地,所述母板单元包括选择电路、测试电路和复位电路,所述选择电路分别与所述测试电路、所述mcu单元和所述子板单元连接,所述测试电路分别与所述mcu单元和所述子板单元连接,所述复位电路分别与所述mcu单元和所述子板单元连接。

8、可选地,所述选择电路包括选择子板电路和选择测试端点电路,所述选择子板电路分别与所述mcu单元和所述子板单元连接,所述选择测试端点电路分别与所述mcu单元和所述测试端点连接。

9、可选地,所述测试电路包括多个测试端点电路,所述测试端点电路分别与所述测试子板和所述mcu单元连接。

10、可选地,所述测试端点电路与所述测试子板之间通过spi接口进行通信。

11、可选地,所述复位电路包括多个子板复位电路,所述子板复位电路分别与所述测试子板和所述mcu单元连接。

12、可选地,所述通信单元包括通信板,所述通信板与所述上位机进行无线通信。

13、可选地,所述多个测试子板包括不同类型的测试子板,所述不同类型的测试子板可同时与所述母板单元连接测试。

14、可选地,所述多个测试端点的单个所述测试端点能测试不同类型的所述测试子板。

15、可选地,所述兼容性的子母板芯片测试系统还包括电源单元,所述电源单元分别与所述通信单元、所述mcu单元、所述母板单元和所述子板单元连接。

16、实施本实用新型实施例包括以下有益效果:本实用新型实施例提供了一种兼容性的子母板芯片测试系统,包括上位机、通信单元、mcu单元、母板单元和子板单元;上位机与通信单元连接,上位机用于向通信单元发送测试指令和接收通信单元发送的测试结果;mcu单元用于接收通信单元发送的测试指令,并发送相应的测试信息到母板单元,mcu单元接收母板单元发送的测试结果并输入至通信单元;母板单元包括多个测试端点,母板单元接收mcu单元的测试信息并发送相应的选择信号至子板单元,母板单元相应的测试端点对子板单元进行测试得到测试结果,并将测试结果输入至mcu单元;子板单元包括多个不同类型的测试子板,子板单元接收母板单元的选择信号,选择信号驱动相应的测试子板与相应的测试端点进行测试。通过上位机发送测试指令,然后母板单元相应的测试端点对子板单元相应的测试子板进行测试,从而只需设计一套母板便能兼容不同类型的子板进行老化测试。

技术特征:1.一种兼容性的子母板芯片测试系统,其特征在于,包括上位机、通信单元、mcu单元、母板单元和子板单元;

2.根据权利要求1所述的兼容性的子母板芯片测试系统,其特征在于,所述母板单元包括选择电路、测试电路和复位电路,所述选择电路分别与所述测试电路、所述mcu单元和所述子板单元连接,所述测试电路分别与所述mcu单元和所述子板单元连接,所述复位电路分别与所述mcu单元和所述子板单元连接。

3.根据权利要求2所述的兼容性的子母板芯片测试系统,其特征在于,所述选择电路包括选择子板电路和选择测试端点电路,所述选择子板电路分别与所述mcu单元和所述子板单元连接,所述选择测试端点电路分别与所述mcu单元和所述测试端点连接。

4.根据权利要求2所述的兼容性的子母板芯片测试系统,其特征在于,所述测试电路包括多个测试端点电路,所述测试端点电路分别与所述测试子板和所述mcu单元连接。

5.根据权利要求4所述的兼容性的子母板芯片测试系统,其特征在于,所述测试端点电路与所述测试子板之间通过spi接口进行通信。

6.根据权利要求2所述的兼容性的子母板芯片测试系统,其特征在于,所述复位电路包括多个子板复位电路,所述子板复位电路分别与所述测试子板和所述mcu单元连接。

7.根据权利要求1所述的兼容性的子母板芯片测试系统,其特征在于,所述通信单元包括通信板,所述通信板与所述上位机进行无线通信。

8.根据权利要求1所述的兼容性的子母板芯片测试系统,其特征在于,所述多个测试子板包括不同类型的测试子板,所述不同类型的测试子板可同时与所述母板单元连接测试。

9.根据权利要求1所述的兼容性的子母板芯片测试系统,其特征在于,所述多个测试端点的单个所述测试端点能测试不同类型的所述测试子板。

10.根据权利要求1所述的兼容性的子母板芯片测试系统,其特征在于,所述兼容性的子母板芯片测试系统还包括电源单元,所述电源单元分别与所述通信单元、所述mcu单元、所述母板单元和所述子板单元连接。

技术总结本技术公开了一种兼容性的子母板芯片测试系统,包括上位机、通信单元、MCU单元、母板单元和子板单元;上位机与所述通信单元连接,MCU单元用于接收通信单元发送的测试指令,并发送相应的测试信息到母板单元,母板单元包括多个测试端点,子板单元包括多个不同类型的测试子板,子板单元接收所述母板单元的选择信号,选择信号驱动相应的测试子板与相应的测试端点进行测试。通过上位机发送测试指令,然后母板单元相应的测试端点对子板单元相应的测试子板进行测试,从而只需设计一套母板便能兼容不同类型的子板进行老化测试,可广泛应用于芯片测试技术领域。技术研发人员:谢登煌受保护的技术使用者:深圳市晶存科技有限公司技术研发日:20230420技术公布日:2024/1/15本文地址:https://www.jishuxx.com/zhuanli/20240731/181796.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。