时序测试电路及其测试方法与流程

- 国知局

- 2024-07-31 19:14:05

本发明涉及半导体,特别是涉及一种时序测试电路及其测试方法。

背景技术:

1、请参阅图1,现有技术的sram(随机静态存储器)通过pad输入时钟、数据及控制信号,通过调整输入时钟的相位差测量出sram的setup(采样建立时间),hold(保持时间)及access time(访问时间)等各项时序。由于测试机台的精度不够高,且pad到内部逻辑的路径延时较长,测量结果误差较大。同时,该方法测试机的输入复杂,测试时间较长且容易出错。

2、为解决上述问题,需要提出一种新型的时序测试电路及其测试方法。

技术实现思路

1、鉴于以上所述现有技术的缺点,本发明的目的在于提供一种时序测试电路及其测试方法,用于解决现有技术中随机静态存储器通过pad输入时钟、数据及控制信号,通过调整输入时钟的相位差测量出sram的setup(采样建立时间),hold(保持时间)及access time(访问时间)等各项时序。由于测试机台的精度不够高,且pad到内部逻辑的路径延时较长,测量结果误差较大,同时,该方法测试机的输入复杂,测试时间较长且容易出错的问题。

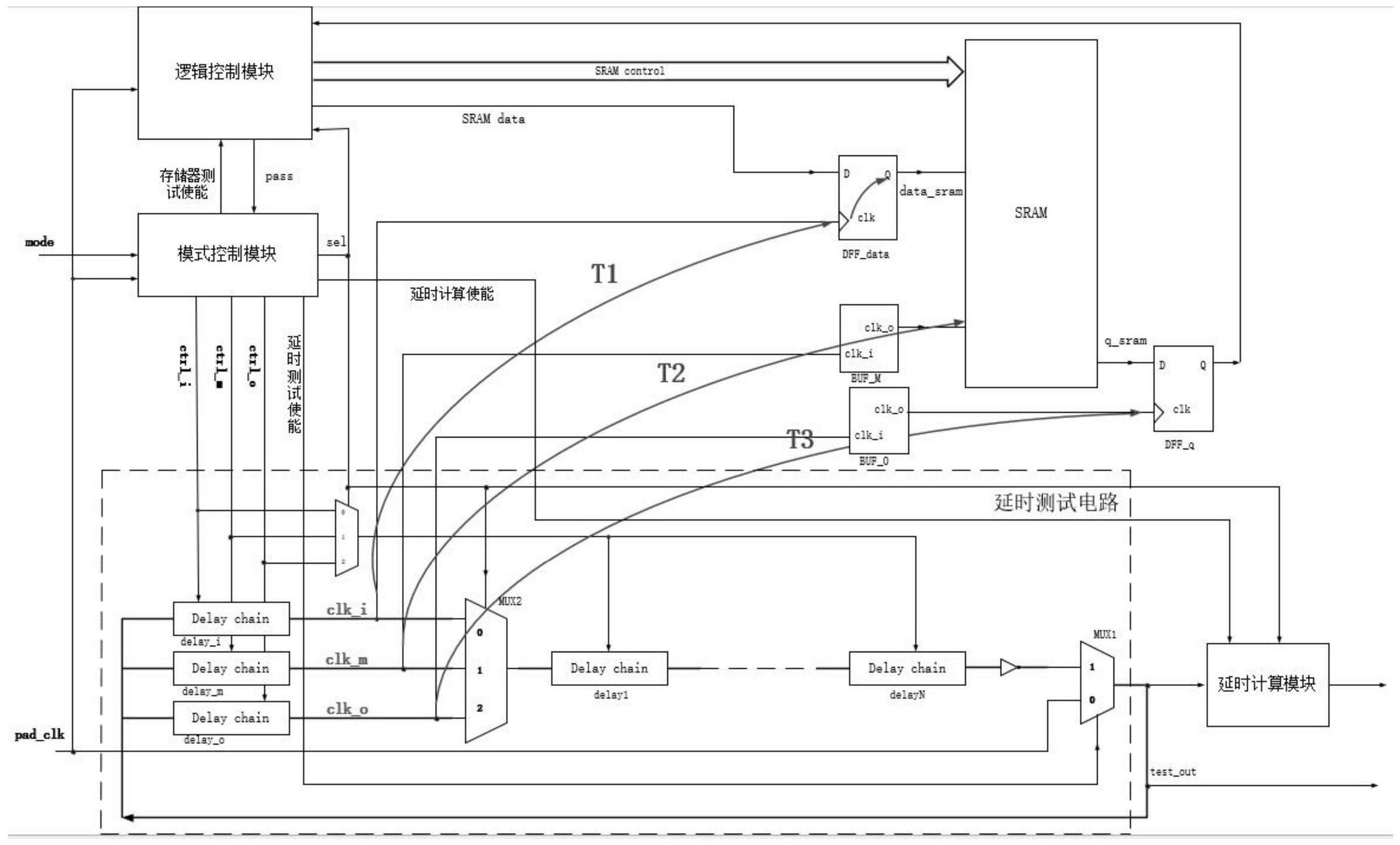

2、为实现上述目的及其他相关目的,本发明提供一种时序测试电路,包括:

3、逻辑控制模块、模式控制模块、延时计算模块、延时测试电路和sram存储单元;

4、所述sram存储单元包括待测试sram,待测试sram包括输入数据寄存器时钟clk_i输入端、sram时钟clk_m输入端和输出寄存器时钟clk_o输入端;

5、所述sram时序测试电路的工作模式为存储器测试模式、延时测试模式及延时计算模式;

6、所述逻辑控制模块用于在存储器测试模式下根据sram的第一算法产生sram的地址、数据及控制信号,根据sram的输出数据产生测试结果,测试结果包括测试通过和测试失败,将所述测试结果传输至模式控制模块;

7、所述模式控制模块用于产生各个工作模式的使能信号,并在存储器测试模式下根据第二算法及测试结果调整延时测试电路的开关控制信号,开关控制信号包括第一至三开关控制信号;在延时测试模式下,模式控制模块产生测试选择信号sel;

8、所述延时测试电路包括第一至三延时块以及延时链,延时链由多个延时块串接而成,第一至三开关控制信号通过第三多路选择器与延时链中每个延时块连接,延时链中延时块的开关由测试选择信号sel控制;第一至三延时块的输入端用于输入信号pad_clk,第一至三延时块的输出端分别根据第一至三开关控制信号输出第一至三时钟信号clk_i、clk_m及clk_o;

9、所述第一至三延时块的输出端分别与数据寄存器时钟clk_i输入端、sram时钟clk_m输入端和输出寄存器时钟clk_o输出端连接;

10、所述第一至三延时块的输出端还通过第二多路选择器与延时链的输入端连接,延时链的输出端与第一反相器的输入端连接,第一反相器的输出端以及输入信号pad_clk与第一多路选择器的输入端连接,第一多路选择器的输出端与延时计算模块的输入端连接;

11、所述延时测试电路用于在延时测试模式和延时计算模式下产生一个闭合的振荡环路,根据模式控制模块的开关控制信号及测试选择信号产生周期性的方波;延时测试电路用于在延时测试模式下通过测试机测量输出信号的频率,在延时计算模式下计算延时测试电路的延时。

12、优选地,所述第一算法的包括checkerboard和march-x。

13、优选地,所述第二算法包括二分法和遍历法。

14、优选地,所述第二时钟信号clk_m通过第一缓冲器与sram时钟clk_m输入端连接;第三时钟信号clk_o通过第二缓冲器与输出寄存器时钟clk_o输入端连接。

15、优选地,所述延时测试电路与逻辑控制模块、模式控制模块、延时计算模块、延时测试电路和sram存储单元在功能上相互独立;延时测试模式与存储器测试模式共用第一至三延时块。

16、优选地,所述模式控制模块式根据输入模式确定所测试的时序的类型,所测试的时序类型为采样建立时间、保持时间或访问时间。

17、优选地,所述第一至三延时块以及所述延时链中的延时块的结构相同。

18、优选地,所述延时块包括相串接的第二、三反相器,第二、三反相器之间设置有多个电容结构,电容结构中电容的一端通过开关连接于第二、三反相器之间,电容的另一端接地。

19、优选地,所述第一至三开关控制信号的调整方法包括:模式控制模块根据收到的测试结果,使用第二算法向前或向后搜索,找到待测的开关控制信号的值。

20、优选地,所述模式控制模块初始设置的第一至三开关控制信号ctrl_i、ctrl_m及ctrl_o需要保证第一次的测试结果为测试通过,后续根据每次收到的测试结果调整相应的第一至三开关控制信号。

21、优选地,sram时序测试电路采样建立时间测试模式的测试方法包括:固定第三开关控制信号ctrl_o,根据第一算法向前调整第二开关控制信号ctrl_m或者向后调整第一开关控制信号ctrl_i,在当前周期的下一个时钟周期进行数据比较并产生测试结果;保持时间测试模式的测试方法包括:固定第三开关控制信号ctrl_o,根据第一算法向前调整第一开关控制信号ctrl_i或者向后调整第二开关控制信号ctrl_m,在当前周期的第三个时钟周期进行数据比较并产生测试结果;访问时间测试模式的测试方法包括:固定第一开关控制信号ctrl_i,根据第一算法向前调整第三开关控制信号ctrl_o或者向后调整第二开关控制信号ctrl_m,在当前周期的下一个时钟周期进行数据比较并产生比较结果。

22、优选地,所述sram时序测试电路及其版图设计中:所述第一至三延时块的输出端分别与数据寄存器时钟clk_i输入端、sram时钟clk_m输入端和输出寄存器时钟clk_o输出端路径上的延时相同或趋向于相同;第一至三延时块在版图上到第二多路选择器的距离相同或趋向于相同。

23、优选地,所述sram时序测试电路及其版图设计中:第二多路选择器的三个输入端到输出端的电路结构相同。

24、优选地,所述sram时序测试电路及其版图设计中:输入数据寄存器寄存器的clk端到q端的距离与第一、二缓冲器输出至输入段的距离相同。

25、优选地,所述sram时序测试电路及其版图设计中:每个延时块的延时精度位于目标范围。

26、优选地,所述延时块的延时精度位于20~30ps。

27、优选地,利用所述采样建立时间测试模式获取第一至三开关控制信号ctrl_i、ctrl_m和ctrl_o之后,采样建立时间、保持时间或访问时间的时序测试值分别为

28、tsetup=tdlym-tdlyi=(ttotal_m-ttotal_i)/(n+1)/2、

29、thold=tdlyi-tdlym=(ttotal_i-ttotal_m)/(n+1)/2、

30、tacc=tdlyo-tdlym=(ttotal_o-ttotal_m)/(n+1)/2,其中,

31、tdlyi、tdlym、tdlyo分别为第三多路选择器选择为0/1/2时,第一至三延时块的延时值,

32、ttotal_i,ttotal_m,ttotal_o分别表示第二多路选择器分别为0/1/2时,延时测试电路的输出test_out上观测到的振荡电路周期。

33、本发明还提供一种上述时序测试电路的测试方法,包括:

34、所述存储器测试模式的测试方法包括:

35、步骤s11、复位后模式控制模块产生存储器测试使能,选择进入对应的时序测试模式,时序测试模式包括采样建立时间、保持时间或访问时间的测试模式;

36、步骤s12、第一至三延时块根据模块控制模块的第一至三开关控制信号ctrl_i、ctrl_m及ctrl_o产生待测试sram的测试时钟;

37、步骤s13、存储器测试模块根据不同的时序测试模式,产生sram的地址、数据及控制信号,并根据sram的输出数据,产生测试结果;

38、步骤s14、模式测试模块根据时序测试模式、第二算法及测试结果调整第一至三开关控制信号ctrl_i、ctrl_m和ctrl_o的值;

39、步骤s15、重复步骤二到步骤五,至找到符合目标值的第一至三开关控制信号ctrl_i、ctrl_m和ctrl_o的值。

40、所述延时测试模式及延时计算模式的测试方法包括:

41、步骤s21:模式控制模块将第一至三开关控制信号ctrl_i、ctrl_m和ctrl_o设置为存储器测试模式测量得到的开关控制校准值;

42、步骤s22:模式控制模块产生延时测试使能,等待延时测试电路产生闭合的振荡环路的周期振荡信号test_out,输出该周期震荡信号并通过测试机测量时钟频率;

43、步骤s23:模式控制模块产生延时计算使能,延时计算模块自动计算出振荡电路周期;

44、步骤s24:测得第一至三时钟信号clk_i、clk_m及clk_o对应振荡环路产生的周期信号的时钟周期ttotal_i、ttotal_m和ttotal_o;

45、步骤s25:计算时序测试采样建立时间、保持时间或访问时间的值。

46、如上所述,本发明的时序测试电路及其测试方法,具有以下有益效果:

47、本发明通过逻辑控制模块产生sram的地址、控制信号及数据,通过延时测试电路精确测试并计算延时,达到精确地自动化测试sram时序的目的,同时可简化测试程序,提高测试效率。

本文地址:https://www.jishuxx.com/zhuanli/20240731/181969.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌抄袭侵权/违法违规的内容, 请发送邮件至 YYfuon@163.com 举报,一经查实,本站将立刻删除。

下一篇

返回列表